# TI380FPA **PACKETBLASTER™**

46

45

44

43

41

40 VSSL

39

38

37

36

35

34

42 NC

PLLVDD

PLLCAP

PLLVSS

MRESET

MANT0

MANT1

MBGR

VDDL

MBRQ

EXTINT0

1 MBCLK1

SPWS011A - MARCH 1995 - REVISED AUGUST 1995

V SS MADL3 MADL2 MADL1 MADL0

52 51 50 49 48 47

**FN PACKAGE**

(TOP VIEW)

SSC MADL<sup>4</sup>

~

21 22 23 24 25 26 27 28 29 30 31 32 33

VIBEN | MOE | MVV VSS VSS VSSC VSSC VDD MAX2 VDD MAX2 VDD MAX0 MAX0 NDDIR

3 2  $\bigcirc$

MAXPL MADL7 MADL6 V DD MADL

MADH0

MADH1

MADH2

MADH3

Vssc

VDD 16

VDDL 17

MADH5

MADH6

MADH7

MADH4

VSSL 11

Vss 12

10

13

14

18

19

20

- Frame-Processing Accelerator for TI380C2x and TI380C3x

- Supports TI380C2x and TI380C3x Token-Ring<sup>™</sup> Adapters

- Supports TI380C2x Ethernet<sup>™</sup> Adapters

- Supports 4- or 6-MHz Adapter Local Bus Operation

- Interfaces Directly to TI380C2x Network Commprocessors

- Hardware Capture of Network Statistics

- Increases Adapter-Frame-Processing Rate up to 28K Frames per Second

- Single 5-V Supply

- 0.8-µm CMOS Technology

- 52-Pin Plastic Leaded Chip Carrier (FN)

- Operating Temperature Range 0°C to 70°C

#### description

The TI380FPA frame processing accelerator (FPA) provides hardware to accelerate the processing rate of frames by the network communications processor (commprocessor). It supports a 4-MHz or 6-MHz adapter local bus operation. The CPU of a normal TI380C2x or TI380C3x adapter is responsible for frame transport between network and host, gathering adapter and network statistics, local-network-management protocols, and medium-access-control (MAC) protocols. The TI380FPA puts the performance bottlenecks of frame transport and statistics gathering into dedicated hardware, leaving the CPU to run MAC and management protocols.

The TI380FPA is responsible for:

- Management of all commprocessor protocol handler (PH) operations. The FPA manages all receive- and transmit-frame queues.

- Management of adapter buffers. The FPA manages all adapter memory buffers, allocating them to the appropriate queues as required.

- Management of host direct memory access (DMA) by way of the commprocessor system interface (SIF) DMA controller.

- Management of frame transfers to the host. The FPA manages queues of frames to and from the host, manages rx/tx list information, and coordinates the two.

- Gathering adapter and network statistics in dedicated hardware counters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IBM and Token-Ring Network are trademarks of International Business Machines Corp. PacketBlaster is a trademark of Texas Instruments Incorporated. Ethernet is a trademark of Xerox Corporation.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

Copyright © 1995, Texas Instruments Incorporated

# TI380FPA PACKETBLASTER™

SPWS011A - MARCH 1995 - REVISED AUGUST 1995

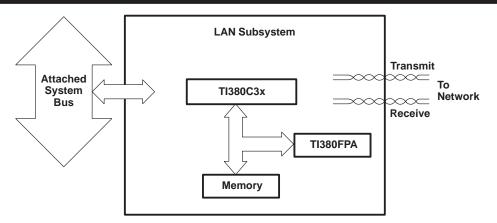

Figure 1. Network-Commprocessor Applications Diagram

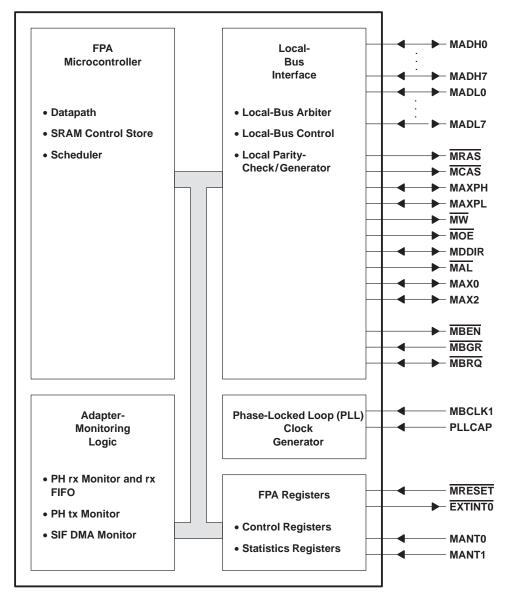

### functional block diagram

TI380FPA attaches directly to the adapter local memory bus of a TI380C2x or TI380C3x commprocessor. Generally, FPA pins should be directly connected to like-named pins of the TI380C2x and TI380C3x.

#### **Pin Functions**

| PIN                                                                  |                                            | ı/o† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------|--------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                 | NO.                                        | 1/01 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EXTINT0                                                              | 35                                         | 0    | FPA interrupt request (see Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MADH0<br>MADH1<br>MADH2<br>MADH3<br>MADH4<br>MADH5<br>MADH6<br>MADH7 | 8<br>9<br>10<br>13<br>15<br>18<br>19<br>20 | I/O  | Local-memory address, data, and status bus - high byte. For the first quarter of the local-memory cycle,<br>MADH0–MADH7 carry address bits AX4 and A0 to A6; for the second quarter, they carry status bits;<br>and for the third and fourth quarters, they carry data bits 0 to 7. The most significant bit is MADH0, and<br>the least significant bit is MADH7.<br>Memory Cycle<br>1Q 2Q 3Q 4Q<br>Signal AX4,A0–A6 Status D0–D7 D0–D7                               |

| MADL0<br>MADL1<br>MADL2<br>MADL3<br>MADL4<br>MADL5<br>MADL6<br>MADL7 | 47<br>48<br>49<br>50<br>52<br>2<br>4<br>5  | I/O  | Local-memory address, data, and status bus - low byte. For the first quarter of the local-memory cycle,<br>MADL0 – MADL7 carry address bits A7 to A14; for the second quarter, they carry address bits AX4 and<br>A0 to A6; and for the third and fourth quarters, they carry data bits 8 to 15. The most significant bit is<br>MADL0, and the least significant bit is MADL7.<br>Memory Cycle<br>1Q 2Q 3Q 4Q<br>Signal A7–A14 AX4,A0–A6 D8–D15 D8–D15                |

| MAL                                                                  | 32                                         | 0    | Memory-address latch. MAL is a strobe signal for sampling the address at the start of the memory cycle; it is used by SRAMs and EPROMs. The full 20-bit word address is valid on MAX0, MAXPH, MAX2, MAXPL, MADH0–MADH7, and MADL0–MADL7. Three 8-bit transparent latches can be used to retain a 20-bit static address throughout the cycle.<br>Rising edge = No signal latching<br>Falling edge = Allows the above address signals to be latched                     |

| MANT0<br>MANT1                                                       | 39<br>38                                   | I    | Test pin inputs. MANT0 and MANT1 should be left unconnected (see Note 2). Module-in-place test mode is achieved by tying MANT0 and MANT1 to ground. In this mode, all TI380FPA output pins are in the high-impedance state and internal pullups on all TI380FPA inputs are disabled (except MANT0 and MANT1).                                                                                                                                                         |

| MAX0                                                                 | 30                                         | I/O  | Local-memory-extended address bit. MAX0 drives AX0 at row-address time, which can be located by MRAS. Normally, MAX0 drives A12 at column address and data time for all cycles.         Memory Cycle         1Q       2Q       3Q       4Q         Signal       AX0       A12       A12       A12                                                                                                                                                                     |

| MAX2                                                                 | 28                                         | I/O  | Local-memory-extended address bit. MAX2 drives AX2 at row address time, which can be located by MRAS. Normally, MAX2 drives A14 at column address and data time for all cycles.         Memory Cycle         1Q       2Q       3Q       4Q         Signal       AX2       A14       A14       A14                                                                                                                                                                     |

| МАХРН                                                                | 7                                          | I/O  | Local-memory-extended address and parity - high byte. For the first quarter of a memory cycle, MAXPH carries the extended address bit AX1; for the second quarter of a memory cycle, MAXPH carries the extended address bit AX0; and for the last half of the memory cycle, MAXPH carries the parity bit for the high-data byte.<br>Memory Cycle           1Q         2Q         3Q         4Q           Signal         AX1         AX0         Parity         Parity |

$^{\dagger}$ I = input, O = output

NOTES: 1. Pin has an open-collector output. EXTINT0 should have an individual 1-kΩ pullup resistor. A 4.7-kΩ resistor can lead to transmit underruns in the adapter system and should not be used. For this reason, a 1-kΩ resistor is specified.

2. Pin has an internal pullup device to maintain a high-voltage level when left unconnected (no etch or loads). Alternatively, both pins tied together can be pulled high through a single 4.7-Ω pullup resistor.

## **Pin Functions (Continued)**

| PIN    |     | 1/0† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MAXPL  | 6   | I/O  | Local-memory-extended address and parity - low byte. For the first quarter of a memory cycle, MAXPL carries the extended address bit AX3; for the second quarter of a memory cycle, MAXPL carries extended address bit AX2; and for the last half of the memory cycle, MAXPL carries the parity bit for the low-data byte.           Memory Cycle           1Q         2Q         3Q         4Q           Signal         AX3         AX2         Parity         Parity                                                                                                                                                                                                                                                                                                                |

| MBCLK1 | 43  | I    | Local-bus clock 1. MBCLK1 is referenced for all local-bus transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MBEN   | 21  | 0    | Buffer enable. MBEN enables the bidirectional buffer outputs on the MADH, MAXPH, MAXPL, and MADL buses during the data phase. MBEN is used in conjunction with MDDIR, which selects the buffer output direction.         H       =       Buffer output disabled         L       =       Buffer output enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MBGR   | 37  | I    | Local bus grant. MBGR indicates that the FPA has been granted access to the adapter local-memory bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MBRQ   | 34  | I/O  | Local bus request. MBRQ is used by the FPA to request bus-master access to the adapter local-memory bus. The FPA also monitors MBRQ to allow it to defer to other higher-priority bus requests (see Note 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MCAS   | 26  | 0    | <ul> <li>Column-address strobe for DRAMs. The column address is valid for the 3/16 of the memory cycle following the row-address portion of the cycle. MCAS is driven low every memory cycle while the column address is valid on MADL0-MADL7, MAXPH, and MAXPL, except when one of the following conditions occurs:</li> <li>1) When the address accessed is a TI380C2x or TI380C3x internal register (&gt;01.0100 - &gt;01.01FF).</li> <li>2) When the address accessed is in the TI380C2x or TI380C3x external device-address range (&gt;01.0200 - &gt;01.02FF). This address range includes the FPA registers.</li> <li>3) When the FPA ROM bit is set, and the address accessed is in adapter ROM-address range (&gt;00.0000-&gt;00.FFFE or &gt;1F.0000-&gt;1F.FFFE).</li> </ul> |

| MDDIR  | 31  | I/O  | Data direction. MDDIR is used as a direction control for bidirectional bus drivers. MDDIR becomes valid before MBEN becomes active.         H = TI380FPA memory bus write         L = TI380FPA memory bus read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MOE    | 22  | 0    | <ul> <li>Memory output enable. MOE is used to enable the outputs of the DRAM memory during a read cycle.</li> <li>MOE is high for EPROM or BIA ROM read cycles.</li> <li>1) When the address read is a TI380C2x or TI380C3x internal register (&gt;01.0100-&gt;01.01FF).</li> <li>2) When the address read is in the TI380C2x or TI380C3x external device-address range (&gt;01.0200-&gt;01.02FF). This address range includes the FPA registers.</li> <li>3) When the FPA ROM bit is set, and the address read is in adapter ROM-address range (&gt;00.0000-&gt;00.FFFE or 1F.0000-1F.FFFE).</li> <li>H= Disable DRAM outputs</li> <li>L= Enable DRAM outputs</li> </ul>                                                                                                             |

| MRAS   | 23  | 0    | Row-address strobe for DRAMs. The row address lasts for the first 5/16 of the memory cycle. MRAS is driven low every memory cycle while the row address is valid on MADL0–MADL7, MAXPH, and MAXPL for both RAM and register-access cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MRESET | 41  | I    | Memory bus reset. MRESET is the reset signal provided by the TI380C2x or TI380C3x and is used to reset and initialize the FPA internal logic. While MRESET is asserted, all FPA output pins are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

$\dagger I = input, O = output$

NOTE 1: Pin has an open-collector output. EXTINTO should have an individual 1-kΩ pullup resistor. A 4.7-kΩ resistor can lead to transmit underruns in the adapter system and should not be used. For this reason, a 1-kΩ resistor is specified.

## **Pin Functions (Continued)**

| PIN<br>NAME      | NO.            | 1/0† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MW               | 24             | 0    | Local-memory write. $\overline{\text{MW}}$ is used to specify a write cycle on the local-memory bus. The data on the MADH0-MADH7 and MADL0-MADL7 buses is valid while $\overline{\text{MW}}$ is low. DRAMs latch data on the falling edge $\overline{\text{MW}}$ , while SRAMs latch data on the rising edge of $\overline{\text{MW}}$ .<br>H = Not a local memory-write cycle<br>L = Local memory write-cycle |

| NC               | 33<br>42       |      | No connect. Do not connect these pins.                                                                                                                                                                                                                                                                                                                                                                         |

| PLLCAP           | 45             | I    | Phase-locked loop (PLL) tuning capacitor (see Note 3).                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DDL</sub> | 17<br>36       | I    | Positive-supply voltage for digital logic. All $V_{DDL}$ pins must be attached to the common-system power-supply plane.                                                                                                                                                                                                                                                                                        |

| V <sub>DD</sub>  | 3<br>16<br>29  | I    | Positive-supply voltage for output buffers. All $V_{\text{DDL}}$ pins must be attached to the common-system power-supply plane.                                                                                                                                                                                                                                                                                |

| PLLVDD           | 46             | I    | Positive-supply voltage for phase-locked loop (see Note 4).                                                                                                                                                                                                                                                                                                                                                    |

| VSSC             | 1<br>14<br>27  | 1    | Ground reference for output buffers (clean ground). All $V_{SSC}$ pins must be attached to the common-system-ground plane.                                                                                                                                                                                                                                                                                     |

| V <sub>SSL</sub> | 11<br>40       | I    | Ground reference for digital logic. All $V_{SSL}$ pins must be attached to the common-system-ground plane.                                                                                                                                                                                                                                                                                                     |

| V <sub>SS</sub>  | 12<br>25<br>51 | I    | Ground connections for output buffers. All $V_{\text{SS}}$ pins must be attached to common-system-ground plane.                                                                                                                                                                                                                                                                                                |

| PLLVSS           | 44             | I    | Ground reference for phase-locked loop. Attach to the common-system-ground plane.                                                                                                                                                                                                                                                                                                                              |

$\dagger I = input, O = output$

NOTES: 2. Pin has an internal pullup device to maintain a high-voltage external level when left unconnected. Alternatively, both pins tied together can be pulled high through a single 4.7-Ω pullup resistor.

PLLCAP

- The PLLCAP requires the following connection: These components must be placed as close as possible to PLLCAP.

- 4. Isolate PLLV<sub>DD</sub> to a separate PLL power pad with ferrite bead separation from the common-system power-supply plane. A 0.1- $\mu$ F decoupling capacitor on PLLV<sub>DD</sub> is also necessary as shown. These components must be placed as close as possible to PLLV<sub>DD</sub>.

**0.1** μ**F**  $1 k\Omega$ GND  $\circ v_{DD}$ PLLVDD  $\sim$ **0.1** μ**F**

$\sim \sim$

### instructions for reading TI380FPA silicon revision code

The TI380FPA contains a register which returns a hard-wired value reflecting the revision of the TI380FPA silicon. The register can be read only before the CPHALT bit (in the SIFACL register) is cleared and the bring-up diagnostics (BUD) begins executing.

The following steps should be taken to read the revision register:

- 1. Set the ARESET bit in the SIFACL register (bit 8) to 1.

- 2. Wait a minimum of 14  $\mu$ s for the reset to take place.

- 3. Clear the ARESET bit and set the CPHALT bit in the same write to the SIFACL register.

- 4. One hundred µs after step 3, read adapter memory location 01.023E to obtain the silicon revision level.

Steps 1 through 3 are explained in more detail in the *TMS380 Second-Generation Token-Ring User's Guide* (literature number SPWU005).

# TI380FPA PACKETBLASTER™

SPWS011A - MARCH 1995 - REVISED AUGUST 1995

| absolute maximum ratings over operating free-air temperature range (unless otherwise noted) <sup>†</sup> |              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| Supply voltage range, V <sub>DD</sub> (see Note 5)                                                       | – 0.6 to 7 V |  |  |  |  |

| Input voltage range (see Note 5) – 0.                                                                    | .3 V to 20 V |  |  |  |  |

| Output voltage range                                                                                     | – 2 V to 7 V |  |  |  |  |

| Power dissipation                                                                                        | 0.5 W        |  |  |  |  |

| Operating free-air temperature range, T <sub>A</sub>                                                     | 0°C to 70°C  |  |  |  |  |

| Storage temperature range, T <sub>stg</sub>                                                              | °C to 150°C  |  |  |  |  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 5: Voltage values are with respect to  $V_{SS}$ .

## recommended operating conditions

|                 |                                                        | MIN  | NOM | MAX                  | UNIT |

|-----------------|--------------------------------------------------------|------|-----|----------------------|------|

| V <sub>DD</sub> | Supply voltage                                         | 4.75 | 5   | 5.25                 | V    |

| VSS             | Supply voltage (see Note 6)                            | 0    | 0   | 0                    | V    |

| VIH             | High-level input voltage                               | 2.0  |     | V <sub>DD</sub> +0.3 | V    |

| VIL             | Low-level input voltage, TTL-level signal (see Note 7) | -0.3 |     | 0.8                  | V    |

| IOH             | High-level output current                              |      |     | -400                 | μΑ   |

| IOL             | Low-level output current (see Note 8)                  |      |     | 2                    | mA   |

| Τ <sub>Α</sub>  | Operating free-air temperature                         | 0    |     | 70                   | °C   |

NOTES: 6. All V<sub>SS</sub> pins should be routed to system ground to minimize inductance.

7. The algebraic convention, where the more negative (less positive) limit is designated as a minimum, is used for logic-voltage levels only.

8. Output current of 2 mA is sufficient to drive five low-power Schottky TTL loads or ten advanced low-power Schottky TTL loads (worst case).

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|      | PARAMETER                                                 | TEST CON<br>(SEE N           |                        | MIN | МАХ  | UNIT |

|------|-----------------------------------------------------------|------------------------------|------------------------|-----|------|------|

| VOH  | High-level output voltage, TTL-level signal (see Note 10) | $V_{DD} = MIN,$              | IOH = MAX              | 2.4 |      | V    |

| VOL  | Low-level output voltage, TTL-level signal                | V <sub>DD</sub> = MIN,       | $I_{OL} = MAX$         |     | 0.6  | V    |

|      | High impedance output ourrent                             | V <sub>DD</sub> = MAX,       | V <sub>O</sub> = 2.4 V |     | 20   | μΑ   |

| 10   | High-impedance output current                             | V <sub>DD</sub> = MAX,       | $V_{O} = 0.4 V$        |     | - 20 |      |

| lj – | Input current, any input or input/output pin              | $V_{I} = V_{SS}$ to $V_{DI}$ | D                      |     | ± 20 | μΑ   |

| IDD  | Supply current                                            | V <sub>DD</sub> = MAX        |                        |     | 110  | mA   |

| Ci   | Input capacitance, any input                              | f = 1 MHz,                   | Others at 0 V          |     | 15   | pF   |

| Co   | Output capacitance, any output or input/output            | f = 1 MHz,                   | Others at 0 V          |     | 15   | pF   |

NOTES: 9. For conditions shown as MIN or MAX, use the appropriate value specified under the recommended operating conditions. 10. The following signals require an external pullup resistor: EXTINTO and MBRQ.

## PARAMETER MEASUREMENT INFORMATION

#### test measurement

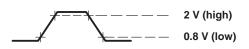

Outputs are driven to a minimum high-logic level of 2.4 V and to a maximum low-logic level of 0.6 V. These levels are compatible with TTL devices.

Output transition times are specified as follows: for a high-to-low transition on either an input or output signal, the level at which the signal is said to be no longer high is 2 V, and the level at which the signal is said to be low is 0.8 V. For a low-to-high transition, the level at which the signal is said to be no longer low is 0.8 V, and the level at which the signal is said to be high is 2 V, as shown below.

The rise and fall times are not specified but are assumed to be those of standard TTL devices, which are typically 1.5 ns.

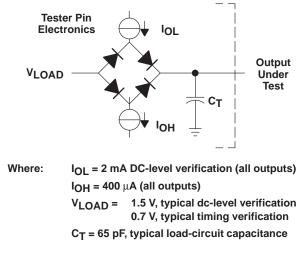

The test load circuit shown in Figure 2 represents the programmable load of the tester-pin electronics, that are used to verify timing parameters of TI380FPA output signals.

Figure 2. Test-Load Circuit

## PARAMETER MEASUREMENT INFORMATION

#### timing parameters

The timing parameters for all the pins of TI380FPA are shown in the following tables and are illustrated in the accompanying figures. The purpose of these figures and tables is to quantify the timing relationships among the various signals. The parameters are numbered for convenience.

#### static signals

The following table lists signals that are not allowed to change dynamically and have no timing associated with them. They should be strapped high or low as required.

| SIGNAL | FUNCTION                                        |

|--------|-------------------------------------------------|

| MANT0  | Test pin for TI manufacturing test <sup>†</sup> |

| MANT1  | Test pin for TI manufacturing test <sup>†</sup> |

† For unit-in-place test

Valid

V

## timing parameter symbology

Timing parameter symbols have been created in accordance with JEDEC standard 100. In order to shorten the symbols, some of the pin names and other related terminology have been abbreviated as shown below:

Rising edge

No longer low

|            | DR       | DRVR                               | RS          |                   |

|------------|----------|------------------------------------|-------------|-------------------|

|            | DRN      | DRVR                               | VDD         | V <sub>DDL</sub>  |

|            | OSC      | OSCIN                              |             |                   |

|            | SCK      | SBCLK                              |             |                   |

| Lower-ca   | se subso | cripts are defined as follows:     |             |                   |

|            | С        | cycle time                         | r           | rise time         |

|            | d        | delay time                         | sk          | skew              |

|            | h        | hold time                          | su          | setup time        |

|            | W        | pulse duration (width)             | t           | transition time   |

| The follow | wing add | itional letters and phrases are de | fined as    | follows:          |

|            | Н        | High                               | Z           | High impedance    |

|            | L        | Low                                | Falling edg | ge No longer high |

## PARAMETER MEASUREMENT INFORMATION

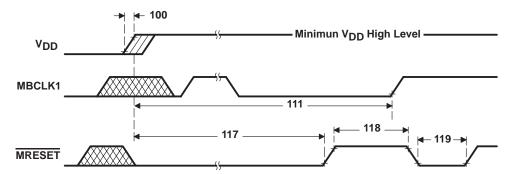

# power up, MBCLK1, MRESET timing

| NO.  |                          |                                                                        | MIN | MAX | UNIT |

|------|--------------------------|------------------------------------------------------------------------|-----|-----|------|

| 100† | tr(VDD)                  | Rise time, 1.2 V to minimum V <sub>DD</sub> -high level                |     | 1   | ms   |

| 111† | <sup>t</sup> d(CKV)      | Delay time, minimum V <sub>DD</sub> -high level to MBCLK1 valid        |     | 3   | ms   |

| 117† | <sup>t</sup> h(VDDH-RSL) | Hold time, MRESET low after V <sub>DD</sub> reaches minimum high level | 5   |     | ms   |

| 118† | <sup>t</sup> w(RSH)      | Pulse duration, MRESET high                                            | 14  |     | μs   |

| 119† | <sup>t</sup> w(RSL)      | Pulse duration, MRESET low                                             | 14  |     | μs   |

<sup>†</sup> This specification is provided as an aid to board design. This specification is not tested.

NOTE A: In order to represent the information on one illustration, nonactual phase and timebase characteristics are shown. Refer to specified parameters for precise information.

#### Figure 3. Power Up, MBCLK1, and MRESET Timing

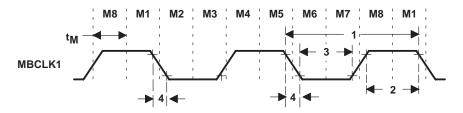

### clock timing: MBCLK1

t<sub>M</sub> is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                             | MIN  | MAX | UNIT |

|-----|-----------------------------|------|-----|------|

| 1   | Period of MBCLK1            | 83.3 |     | ns   |

| 2   | Pulse duration, MBCLK1 high | 33   |     | ns   |

| 3   | Pulse duration, MBCLK1 low  | 33   |     | ns   |

| 4   | Transition time, MBCLK1     | 5    |     | ns   |

Figure 4. Clock Timing: MBCLK1

## PARAMETER MEASUREMENT INFORMATION

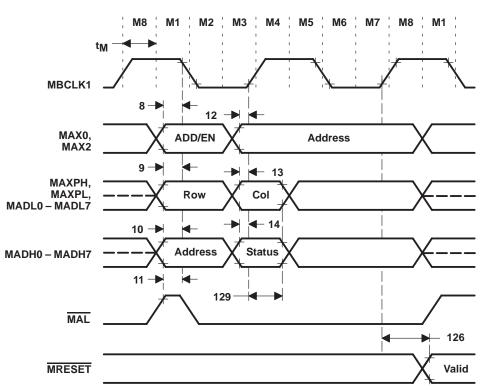

# FPA-bus-master timing: MAL, MRESET, and ADDRESS

t<sub>M</sub> is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                         | MIN                  | MAX | UNIT |

|-----|-----------------------------------------------------------------------------------------|----------------------|-----|------|

| 8   | Setup time, address/enable on MAX0 and MAX2 before MBCLK1 no longer high                | t <sub>M</sub> -9    |     | ns   |

| 9   | Setup time, row address on MADL0-MADL7, MAXPH, and MAXPL before MBCLK1 no longer high   | t <sub>M</sub> -14   |     | ns   |

| 10  | Setup time, address on MADH0-MADH7 before MBCLK1 no longer high                         | t <sub>M</sub> -14   |     | ns   |

| 11  | Setup time, MAL high before MBCLK1 no longer high                                       | t <sub>M</sub> -13   |     | ns   |

| 12  | Setup time, address on MAX0 and MAX2 before MBCLK1 no longer low                        | 0.5t <sub>M</sub> -9 |     | ns   |

| 13  | Setup time, column address on MADL0-MADL7, MAXPH, and MAXPL before MBCLK1 no longer low | 0.5t <sub>M</sub> -9 |     | ns   |

| 14  | Setup time, status on MADH0-MADH7 before MBCLK1 no longer low                           | 0.5t <sub>M</sub> -9 |     | ns   |

| 126 | Delay time, MBCLK1 no longer low to MRESET valid                                        | 0                    | 20  | ns   |

| 129 | Hold time, column address/status after MBCLK1 no longer low                             | t <sub>M</sub> -7    |     | ns   |

Figure 5. FPA-Bus-Master Timing: MAL, MRESET, and ADDRESS

## PARAMETER MEASUREMENT INFORMATION

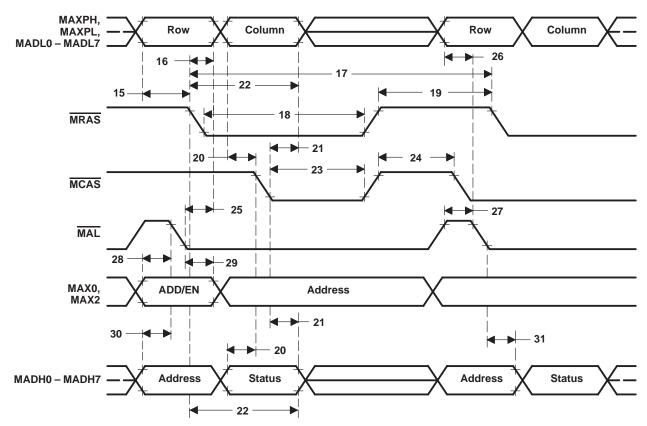

# FPA-bus-master timing: MRAS, MCAS, and MAL to ADDRESS

$t_{M}$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                                                | MIN                      | MAX | UNIT |

|-----|----------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|

| 15  | Setup time, row address on MADL0 – MADL7, MAXPH, and MAXPL before $\overline{\text{MRAS}}$ no longer high      | 1.5t <sub>M</sub> – 11.5 |     | ns   |

| 16  | Hold time, row address on MADL0-MADL7, MAXPH, and MAXPL after MRAS no longer high                              | t <sub>M</sub> -6.5      |     | ns   |

| 17  | Delay time, MRAS no longer high to MRAS no longer high in the next memory cycle                                | 8t <sub>M</sub>          |     | ns   |

| 18  | Pulse duration, MRAS low                                                                                       | 4.5t <sub>M</sub> -9     |     | ns   |

| 19  | Pulse duration, MRAS high                                                                                      | 3.5t <sub>M</sub> -9     |     | ns   |

| 20  | Setup time, column address (MADL0-MADL7, MAXPH, and MAXPL) and status (MADH0-MADH7) before MCAS no longer high | 0.5t <sub>M</sub> -9     |     | ns   |

| 21  | Hold time, column address (MADL0-MADL7, MAXPH, and MAXPL) and status (MADH0-MADH7) after MCAS low              | t <sub>M</sub> -9        |     | ns   |

| 22  | Hold time, column address (MADL0-MADL7, MAXPH, and MAXPL) and status (MADH0-MADH7) after MRAS no longer high   | 2.5t <sub>M</sub> -6.5   |     | ns   |

| 23  | Pulse duration, MCAS low                                                                                       | 3t <sub>M</sub> -9       |     | ns   |

| 24  | Pulse duration, MCAS high, refresh cycle follows read or write cycle                                           | 2t <sub>M</sub> -9       |     | ns   |

| 25  | Hold time, row address on MADL0-MADL7, MAXPH, and MAXPL after MAL low                                          | 1.5t <sub>M</sub> -9     |     | ns   |

| 26  | Setup time, row address on MADL0-MADL7, MAXPH, and MAXPL before $\overline{\text{MAL}}$ no longer high         | t <sub>M</sub> -9        |     | ns   |

| 27  | Pulse duration, MAL high                                                                                       | t <sub>M</sub> -9        |     | ns   |

| 28  | Setup time, address/enable on MAX0 and MAX2 before MAL no longer high                                          | t <sub>M</sub> -9        |     | ns   |

| 29  | Hold time, address/enable of MAX0 and MAX2 after MAL low                                                       | 1.5t <sub>M</sub> -9     |     | ns   |

| 30  | Setup time, address on MADH0-MADH7 before MAL no longer high                                                   | t <sub>M</sub> -9        |     | ns   |

| 31  | Hold time, address on MADH0–MADH7 after MAL low                                                                | 1.5t <sub>M</sub> -9     |     | ns   |

## PARAMETER MEASUREMENT INFORMATION

Figure 6. FPA-Bus-Master Timing: MRAS, MCAS, and MAL to ADDRESS

## PARAMETER MEASUREMENT INFORMATION

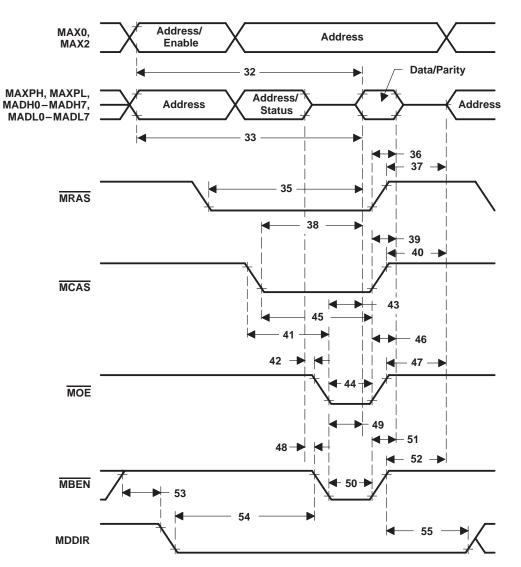

## FPA-bus-master timing: read cycle

$t_{M}$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                                                                  | MIN                   | MAX                     | UNIT |

|-----|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|------|

| 32  | Access time, address/enable valid on MAX0 and MAX2 to valid data/parity                                                          |                       | 6t <sub>M</sub> – 23    | ns   |

| 33  | Access time, address valid on MAXPH, MAXPL, MADH0–MADH7, and MADL0–MADL7 to valid data/parity                                    |                       | 6t <sub>M</sub> -23     | ns   |

| 35  | Access time, MRAS low to valid data/parity                                                                                       |                       | 4.5t <sub>M</sub> -21.5 | ns   |

| 36  | Hold time, valid data/parity after MRAS no longer low                                                                            | 0                     |                         | ns   |

| 37† | Hold time, address in the high-impedance state on MAXPH, MAXPL, MADH0-MADH7 and MADL0-MADL7 after MRAS high (see Note 11)        | 2t <sub>M</sub> -10.5 |                         | ns   |

| 38  | Access time, MCAS low to valid data/parity                                                                                       |                       | 3t <sub>M</sub> -23     | ns   |

| 39  | Hold time, valid data/parity after MCAS no longer low                                                                            | 0                     |                         | ns   |

| 40† | Hold time, address in the high-impedance state on MAXPH, MAXPL, MADH0-MADH7, and MADL0-MADL7 after MCAS high (see Note 11)       | 2t <sub>M</sub> -13   |                         | ns   |

| 41  | Delay time, MCAS no longer high to MOE low                                                                                       |                       | t <sub>M</sub> +13      | ns   |

| 42† | Setup time, address/status in the high-impedance state on MAXPH, MAXPL, MADL0-MADL7, and MADH0-MADH7 before MOE no longer high   | 0                     |                         | ns   |

| 43  | Access time, MOE low to valid data/parity                                                                                        |                       | 2t <sub>M</sub> -25     | ns   |

| 44  | Pulse duration, MOE low                                                                                                          | 2t <sub>M</sub> -9    |                         | ns   |

| 45  | Delay time, MCAS low to MOE no longer low                                                                                        | 3t <sub>M</sub> -9    |                         | ns   |

| 46  | Hold time, valid data/parity in after MOE no longer low                                                                          | 0                     |                         | ns   |

| 47† | Hold time, address in the high-impedance state on MAXPH, MAXPL, MADH0-MADH7, and MADL0-MADL7 after MOE high (see Note 11)        | 2t <sub>M</sub> -15   |                         | ns   |

| 48† | Setup time, address/status in the high-impedance state on MAXPH, MAXPL, MADL0-MADL7, and MADH0-MADH7, before MBEN no longer high | 0                     |                         | ns   |

| 49  | Access time, MBEN low to valid data/parity                                                                                       |                       | 2t <sub>M</sub> -25     | ns   |

| 50  | Pulse duration, MBEN low                                                                                                         | 2t <sub>M</sub> -9    |                         | ns   |

| 51  | Hold time, valid data/parity after MBEN no longer low                                                                            | 0                     |                         | ns   |

| 52† | Hold time, address in the high-impedance state on MAXPH, MAXPL, MADH0-MADH7, and MADL0-MADL7 after MBEN high (see Note 11)       | 2t <sub>M</sub> -15   |                         | ns   |

| 53  | Hold time, MDDIR high after MBEN high, read follows write cycle                                                                  | 1.5t <sub>M</sub> -12 |                         | ns   |

| 54  | Setup time, MDDIR low before MBEN no longer high                                                                                 | 3t <sub>M</sub> -9    |                         | ns   |

| 55  | Hold time, MDDIR low after MBEN high, write follows read cycle                                                                   | 3t <sub>M</sub> -12   |                         | ns   |

<sup>†</sup> This specification has been characterized to meet stated value. This parameter is not tested.

NOTE 11: The data/parity that exists on the address lines will most likely achieve the high-impedance state sometime later than the rising edge of MRAS, MCAS, MOE, or MBEN (between MIN and MAX of timing parameter 36) and will be a function of the memory being read. The MIN time given represents the time from the rising edge of MRAS, MCAS, MOE, or MBEN to the beginning of the next address and does not represent the actual high-impedance state on the address bus.

## PARAMETER MEASUREMENT INFORMATION

Figure 7. FPA-Bus-Master Timing: Read Cycle

# PARAMETER MEASUREMENT INFORMATION

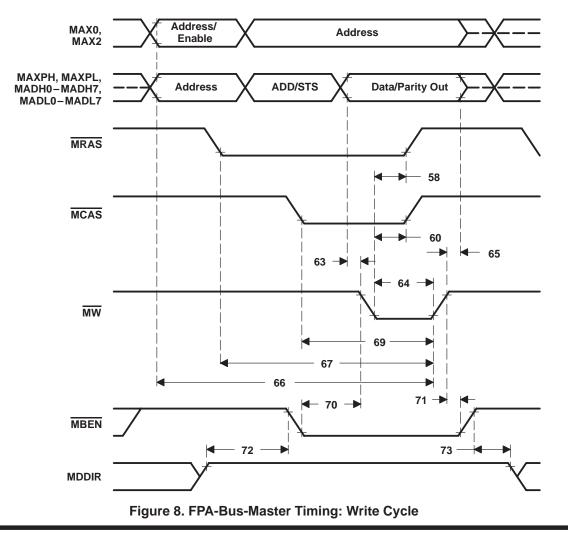

# FPA-bus-master timing: write cycle

$t_{M}$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                    | MIN                     | MAX | UNIT |

|-----|--------------------------------------------------------------------|-------------------------|-----|------|

| 58  | Setup time, MW low before MRAS no longer low                       | 1.5t <sub>M</sub> – 9   |     | ns   |

| 60  | Setup time, MW low before MCAS no longer low                       | 1.5t <sub>M</sub> -6.5  |     | ns   |

| 63  | Setup time, valid data/parity before MW no longer high             | 0.5t <sub>M</sub> -11.5 |     | ns   |

| 64  | Pulse duration, MW low                                             | 2.5t <sub>M</sub> -9    |     | ns   |

| 65  | Hold time, data/parity out valid after MW high                     | 0.5t <sub>M</sub> -10.5 |     | ns   |

| 66  | Setup time, address valid on MAX0 and MAX2 before MW no longer low | 7t <sub>M</sub> -11.5   |     | ns   |

| 67  | Hold time, MRAS low to MW no longer low                            | 5.5t <sub>M</sub> -9    |     | ns   |

| 69  | Hold time, MCAS low to MW no longer low                            | 4t <sub>M</sub> -11.5   |     | ns   |

| 70  | Setup time, MBEN low before MW no longer high                      | 1.5t <sub>M</sub> -13.5 |     | ns   |

| 71  | Hold time, MBEN low after MW high                                  | 0.5t <sub>M</sub> -6.5  |     | ns   |

| 72  | Setup time, MDDIR high before MBEN no longer high                  | 2t <sub>M</sub> -9      |     | ns   |

| 73  | Hold time, MDDIR high after MBEN high                              | 1.5t <sub>M</sub> -12   |     | ns   |

# TI380FPA PACKETBLASTER™

SPWS011A - MARCH 1995 - REVISED AUGUST 1995

# PARAMETER MEASUREMENT INFORMATION

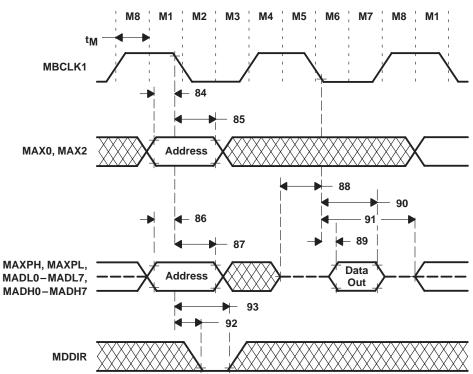

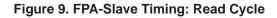

## FPA-slave timing: read cycle

$t_{M}$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                               | MIN                    | MAX | UNIT |

|-----|-----------------------------------------------------------------------------------------------|------------------------|-----|------|

| 84  | Setup time, address on MAX0, MAX2 before MBCLK1 falling edge, FPA-slave read                  | 10                     |     | ns   |

| 85  | Hold time, address on MAX0, MAX2 after MBCLK1 falling edge, FPA-slave read                    | 0                      |     | ns   |

| 86  | Setup time, valid address before MBCLK1 falling edge, FPA-slave read                          | 10                     |     | ns   |

| 87  | Hold time, valid address after MBCLK1 falling edge, FPA-slave read                            | 0                      |     | ns   |

| 88  | Setup time, address in the high-impedance state before MBCLK1 falling edge, FPA-slave read    | 0                      |     | ns   |

| 89  | Setup time, data/parity valid after MBCLK1 falling edge, FPA-slave read                       | 0.5t <sub>M</sub> + 10 |     | ns   |

| 90  | Hold time, data/parity valid after MBCLK1 falling edge, FPA-slave read                        | 2t <sub>M</sub>        |     | ns   |

| 91  | Setup time, data/parity in the high-impedance state after MBCLK1 falling edge, FPA-slave read | 2t <sub>M</sub> + 9    |     | ns   |

| 92  | Setup time, MDDIR low after MBCLK1 falling edge, FPA-slave read                               | t <sub>M</sub> – 15    |     | ns   |

| 93  | Hold time, MDDIR low after MBCLK1 falling edge, FPA-slave read                                | tM                     |     | ns   |

# PARAMETER MEASUREMENT INFORMATION

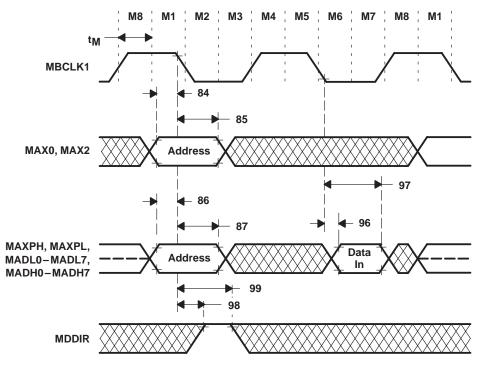

## FPA-slave timing: write cycle

$t_M$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                              | MIN MAX             | UNIT |

|-----|------------------------------------------------------------------------------|---------------------|------|

| 84  | Setup time, address on MAX0, MAX2 before MBCLK1 falling edge, FPA-slave read | 10                  | ns   |

| 85  | Hold time, address on MAX0, MAX2 after MBCLK1 falling edge, FPA-slave read   | 0                   | ns   |

| 86  | Setup time, valid address before MBCLK1 falling edge, FPA-slave read         | 10                  | ns   |

| 87  | Hold time, valid address after MBCLK1 falling edge, FPA-slave read           | 0                   | ns   |

| 96  | Setup time, valid data/parity after MBCLK1 falling edge, FPA-slave write     | t <sub>M</sub> – 15 | ns   |

| 97  | Hold time, valid data/parity after MBCLK1 falling edge, FPA-slave write      | t <sub>M</sub>      | ns   |

| 98  | Setup time, MDDIR high after MBCLK1 falling edge, FPA-slave write            | t <sub>M</sub> – 15 | ns   |

| 99  | Hold time, MDDIR high after MBCLK1 falling edge, FPA-slave read              | t <sub>M</sub>      | ns   |

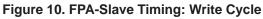

## PARAMETER MEASUREMENT INFORMATION

## FPA-slave timing: status monitoring

t<sub>M</sub> is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                        | MIN                  | MAX | UNIT |

|-----|----------------------------------------------------------------------------------------|----------------------|-----|------|

| 100 | Setup time, valid bus status on MADH0-MADH7 after MBCLK1 falling edge, FPA-slave cycle | 2t <sub>M</sub> – 5  |     | ns   |

| 101 | Hold time, valid bus status on MADH0-MADH7 after MBCLK1 falling edge, FPA-slave cycle  | 2t <sub>M</sub> + 10 |     | ns   |

Figure 11. FPA-Slave Timing: Status Monitoring

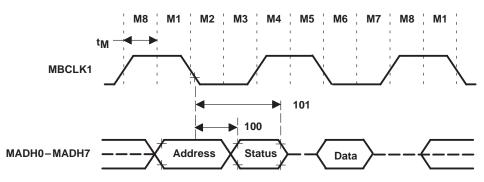

## FPA-bus arbitration: arbitration handshake

$t_{M}$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                           | MIN             | MAX | UNIT |

|-----|---------------------------------------------------------------------------|-----------------|-----|------|

| 76  | Setup time, MBRQ output low before MBCLK1 falling edge, FPA-bus request   | 10              |     | ns   |

| 77  | Hold time, MBRQ output low after MBCLK1 falling edge, FPA-bus request     | 3t <sub>M</sub> |     | ns   |

| 78  | Delay time, MBGR low after MBCLK1 falling edge, bus granted to FPA        | 10              |     | ns   |

| 81  | Setup time, MBRQ input valid before MBCLK1 falling edge, request override | 0               |     | ns   |

| 82  | Hold time, MBRQ input valid before MBCLK1 falling edge, request override  | tM              |     | ns   |

| 83  | Delay time, MBGR high after MBCLK1 falling edge, bus taken from FPA       | 0               |     | ns   |

M8 M1 M2 M3 M4 M5 M6 M7 M8 M1 M2 M3 M4 M5 M6 M7 M8

Figure 12. FPA-Bus Arbitration: Arbitration Handshake

## PARAMETER MEASUREMENT INFORMATION

## FPA-bus arbitration: FPA takes control of bus

$t_M$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                  | MIN                  | MAX                 | UNIT |

|-----|----------------------------------------------------------------------------------|----------------------|---------------------|------|

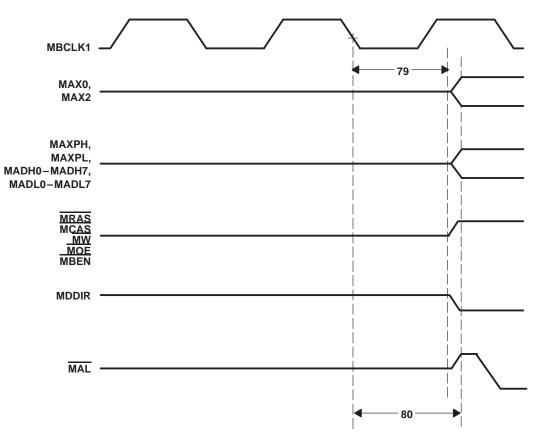

| 79  | Setup time, FPA in the high-impedance state after MBCLK1 rising edge, bus resume | 2t <sub>M</sub> – 13 |                     | ns   |

| 80  | Delay time, MBCLK1 falling edge to FPA valid, bus resume                         |                      | 2t <sub>M</sub> + 9 | ns   |

Figure 13. FPA-Bus Arbitration: FPA Takes Control of Bus

## PARAMETER MEASUREMENT INFORMATION

## FPA-bus arbitration: FPA releases control of bus

$t_{M}$  is the cycle time of one-eighth of a local-memory cycle (20.83 ns minimum).

| NO. |                                                                                  | MIN                    | MAX               | UNIT |

|-----|----------------------------------------------------------------------------------|------------------------|-------------------|------|

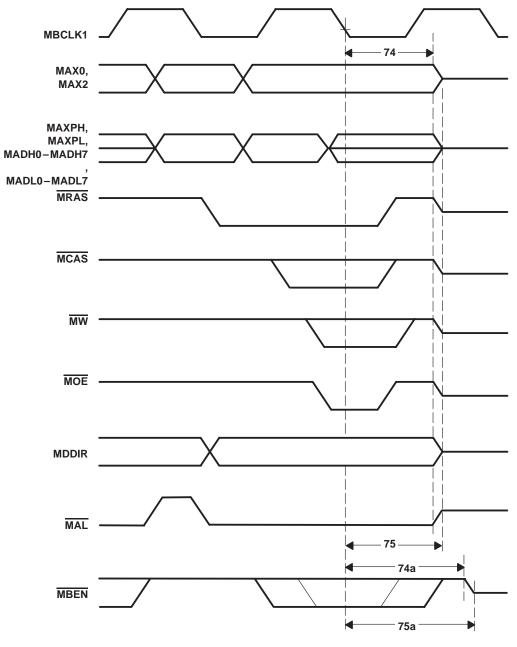

| 74  | Hold time, FPA after MBCLK1 falling edge, bus release                            | 2.5t <sub>M</sub> – 13 |                   | ns   |

| 74a | Hold time, MBEN valid after MBCLK1 falling edge, bus release                     | 3t <sub>M</sub> – 13   |                   | ns   |

| 75  | Delay time, MBCLK1 falling edge to FPA in the high-impedance state, bus release  |                        | 2.5t <sub>M</sub> | ns   |

| 75a | Delay time, MBCLK1 falling edge to MBEN in the high-impedance state, bus release |                        | 3t <sub>M</sub>   | ns   |

Figure 14. FPA-Bus Arbitration: FPA Releases Control of Bus

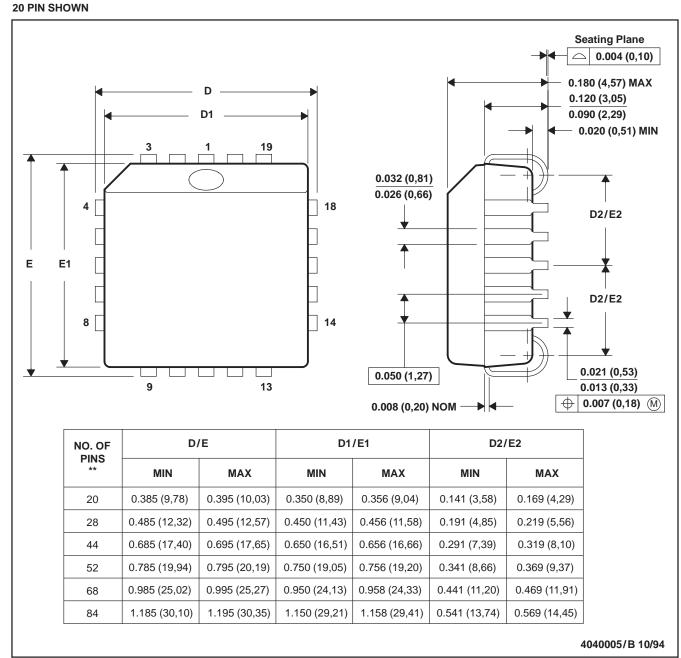

## MECHANICAL DATA

### PLASTIC J-LEADED CHIP CARRIER

FN (S-PQCC-J\*\*)

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-018

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated