#### SN65DPHY440SS, SN75DPHY440SS

SLLSEO9C -MARCH 2016-REVISED AUGUST 2019

# SNx5DPHY440SS CSI-2/DSI DPHY Re-timer

#### **Features**

- MIPI DPHY 1.1 Specification compliant

- Enables low-cost cable solutions

- Supports up to 4 lanes at 1.5 Gbps

- CSI-2/DSI Clock rates from 100 MHz To 750 MHz

- Sub mW Power in shutdown state

- MIPI DSI Bi-directional LP mode supported

- Supports for both ULPS and LP power states

- Adjustable output voltage swing

- Selectable TX Pre-emphasis levels

- Adjustable Rx EQ to compensate for ISI loss

- Configurable edge rate control

- Dynamic data and clock skew compensation

- 3-kV ESD HBM protection

- Industrial temperature range: -40°C to 85°C (SN65DPHY440SS)

- Commercial temperature range: 0°C to 70°C (SN75DPHY440SS)

- Available in single 1.8-Vlpply

# **Applications**

- Notebook PC

- Clam Ihell

- **Tablets**

- Camera

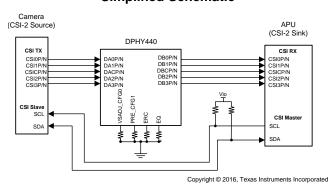

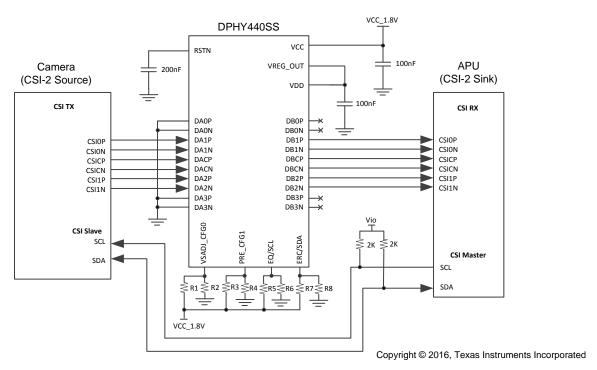

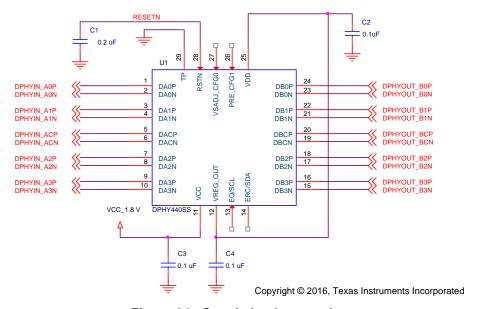

#### Simplified Schematic

# 3 Description

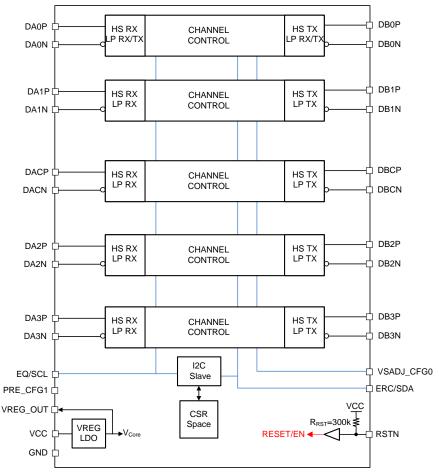

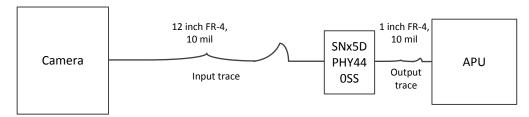

The DPHY440 is a one to four lane and clock MIPI DPHY re-timer that regenerates the DPHY signaling. The device complies with MIPI DPHY 1.1 standard and can be used in either a MIPI CSI-2 or MIPI DSI application at datarates of up to 1.5 Gbps.

The device compensates for PCB, connector, and cable related frequency loss and switching related loss to provide the optimum electrical performance from a CSI2/DSI source to sink. The DPHY440's DPHY inputs feature configurable equalizers.

The output pins automatically compensate for uneven skew between clock and data lanes received on its inputs ports. The DPHY440 output voltage swing and edge rate can be adjusted by changing the state of the VSADJ CFG0 pin and ERC pin respectively.

The DPHY440 is optimized for mobile applications, and contains activity detection circuitry on the DPHY Link interface that can transition into a lower power mode when in ULPS and LP states.

The SN65DPHY440SS is characterized for an industrial temperature range from -40°C to 85°C while SN75DPHY440SS is characterized for commercial temperature range from 0°C to 70°C.

#### Device Information (1)

| PART NUMBER                    | PACKAGE   | BODY SIZE (NOM)   |

|--------------------------------|-----------|-------------------|

| SN65DPHY440SS<br>SN75DPHY440SS | WQFN (28) | 3.50 mm x 5.50 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

### Typical Application

| 1 | Гэ | h | ما | Ωf  | Cor | 1ta | ntc  |

|---|----|---|----|-----|-----|-----|------|

|   | а  | U | 16 | OI. | CUI | ILE | IILS |

| 1 | Features 1                                   | 7.3 Feature Description                        | 12               |

|---|----------------------------------------------|------------------------------------------------|------------------|

| 2 | Applications 1                               | 7.4 Device Functional Modes                    | 14               |

| 3 | Description 1                                | 7.5 Register Maps                              | 15               |

| 4 | Revision History2                            | 8 Application and Implementation               | 21               |

| 5 | Pin Configuration and Functions 4            | 8.1 Application Information,                   | <mark>2</mark> 1 |

| 6 | Specifications                               | 8.2 Typical Application, CSI-2 Implementations | <mark>2</mark> 1 |

| • | 6.1 Absolute Maximum Ratings                 | 9 Power Supply Recommendations                 | 25               |

|   | 6.2 ESD Ratings                              | 10 Layout                                      | 26               |

|   | 6.3 Recommended Operating Conditions         | 10.1 Layout Guidelines                         | 26               |

|   | 6.4 Thermal Information                      | 10.2 Layout Example                            | 26               |

|   | 6.5 Electrical Characteristics, Power Supply | 11 Device and Documentation Support            | <mark>27</mark>  |

|   | 6.6 Electrical Characteristics               | 11.1 Related Links                             | <mark>27</mark>  |

|   | 6.7 Timing Requirements 8                    | 11.2 Community Resources                       | <mark>27</mark>  |

|   | 6.8 Switching Characteristics                | 11.3 Trademarks                                | <mark>27</mark>  |

|   | 6.9 Typical Characteristics10                | 11.4 Electrostatic Discharge Caution           | <mark>27</mark>  |

| 7 | Detailed Description 11                      | 11.5 Glossary                                  | 27               |

| - | 7.1 Overview 11                              | 12 Mechanical, Packaging, and Orderable        |                  |

|   | 7.2 Functional Block Diagram                 | Information                                    | 27               |

|   | •                                            |                                                |                  |

# 4 Revision History

| Cł | hanges from Revision B (August 2017) to Revision C                                                                                                       | Page |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed F <sub>(BR)</sub> MAX value From: 1 Gbps To: 1.5 Gbps in the Switching Characteristics table                                                     | 9    |

| Cł | hanges from Revision A (April 2016) to Revision B                                                                                                        | Page |

| •  | Changed Feature From: CSI-2/DSI Clock Rates From 100 MHz to 500 MHz To: CSI-2/DSI Clock Rates From 100 MHz to 750 MHz                                    |      |

| •  | Changed text in the <i>Description</i> From: MIPI DSI application at datarates of up to 1 Gbps. To: MIPI DSI application at datarates of up to 1.5 Gbps. | 1    |

| •  | Changed V <sub>IH</sub> = 4 dB To: V <sub>IH</sub> = 5 dB in the <i>Pin Functions</i> table                                                              | 4    |

| •  | Added a Test Condition of EQ is at 750 MHz to V <sub>(RXEQ1)</sub> n the <i>Electrical Characteristics</i> table                                         | 7    |

| •  | Changed V <sub>(RXEQ2)</sub> TYP value From: 4 dB To: 5 dB in the <i>Electrical Characteristics</i> table                                                | 7    |

| •  | Changed the MIPI DPHY HS Interface section in the Timing Requirements table                                                                              | 8    |

| •  | Changed F <sub>(HSCLK)</sub> From 500 µsMHz To: 750 MHz in the Switching Characteristics table                                                           | 9    |

| •  | Changed F <sub>(DESKEW)</sub> from 500 MHz To: 750 MHz.                                                                                                  | 9    |

| •  | Changed t <sub>R</sub> and t <sub>F</sub> Datarate Test Conditions and values                                                                            | 9    |

| •  | Changed text From: application at datarates of up to 1 Gbps To: application at datarates of up to 1.5 Gbps in the Overview section                       | 1′   |

| •  | Changed Table 1                                                                                                                                          |      |

| •  | Changed 11 – 4 dB To: 11 – 5 dB for RXEQ_CLK in Table 8                                                                                                  |      |

| •  | Changed 11 – 4 dB To: 11 – 5 dB for RXEQ_DATA in Table 8                                                                                                 |      |

| •  | Changed From: Data Rate To: Data Rate (200 Mbps to 1.5 Gbps) in Table 15                                                                                 |      |

Submit Documentation Feedback

Copyright © 2016–2019, Texas Instruments Incorporated

| C | hanges from Original (March 2016) to Revision A                                                                                    | Page           |

|---|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| • | Changed Features From: 3-kV ESD HBM Protection To: 2-kV ESD HBM Protection                                                         | 1              |

| • | Changed From: (approx. 100K) To: (100K) in the Pin Functions table for pins 13 and 14                                              | 4              |

| • | Changed From: (approx. 100K) To: (100K) in the Pin Functions table for pins 26, 27, and 28                                         | 5              |

| • | Changed ESD Ratings values. HBM From: ±2000 To: ±3000, and CDM Form: ±500 To: ±1000                                                | 6              |

| • | Changed V <sub>(RXEQ2)</sub> TYP value From: 5 dB To: 4 dB in the <i>Electrical Characteristics</i> table                          | 7              |

| • | Added MIN and MAX values to $ V_{OD(VD0)} $ , $ V_{OD(VD1)} $ , and $ V_{OD(VD2)} $ in the <i>Electrical Characteristics</i> table | <mark>7</mark> |

| • | Deleted rows Z <sub>OS</sub> and ΔZ <sub>OS</sub> from the <i>Electrical Characteristics</i> table                                 | 8              |

| • | Updated the MIPI DPHY LP Transmitter Interface section of the Switching Characteristics table                                      | 9              |

| • | Changed 5 dB to 4 dB in HS Receive Equalization and Table 1                                                                        | 12             |

| • | Changed 11 – 4 dB To: 11 – 5 dB in Table 8                                                                                         | 17             |

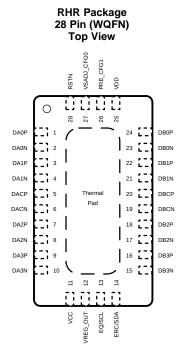

# 5 Pin Configuration and Functions

### **Pin Functions**

| PIN      | 1   |                                     | INTERNAL               |                                                                                                                                                                                                                                                                       |

|----------|-----|-------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | I/O                                 | PULLUP/PULLDOWN        | DESCRIPTION                                                                                                                                                                                                                                                           |

| DAOP     | 1   | 100-Ω                               |                        | CSI-2/DSI Lane 0 Differential positive Input. Supports DSI LP Backchannel. If unused, this pin should be tied to GND.                                                                                                                                                 |

| DAON     | 2   | Differential<br>Input               |                        | CSI-2/DSI Lane 0 Differential negative Input. Supports DSI LP Backchannel. If unused, this pin should be tied to GND.                                                                                                                                                 |

| DA1P     | 3   | 100-Ω<br>Differential               |                        | CSI-2/DSI Lane 1 Differential positive Input. If unused, this pin should be tied to GND.                                                                                                                                                                              |

| DA1N     | 4   | Input<br>(Failsafe)                 |                        | CSI-2/DSI Lane 1 Differential negative input. If unused, this pin should be tied to GND.                                                                                                                                                                              |

| DACP     | 5   | 100-Ω                               |                        | CSI-2/DSI Differential Clock positive Input                                                                                                                                                                                                                           |

| DACN     | 6   | Differential<br>Input<br>(Failsafe) |                        | CSI-2/DSI Differential Clock negative Input                                                                                                                                                                                                                           |

| DA2P     | 7   | 100-Ω<br>Differential               |                        | CSI-2/DSI Lane 2 Differential positive Input. If unused, this pin should be tied to GND.                                                                                                                                                                              |

| DA2N     | 8   | Input<br>(Failsafe)                 |                        | CSI-2/DSI Lane 2 Differential negative Input. If unused, this pin should be tied to GND.                                                                                                                                                                              |

| DA3P     | 9   | 100-Ω<br>Differential               |                        | CSI-2/DSI Lane 3 Differential positive Input. If unused, this pin should be tied to GND.                                                                                                                                                                              |

| DA3N     | 10  | Input<br>(Failsafe)                 |                        | CSI-2/DSI Lane 3 Differential negative Input. If unused, this pin should be tied to GND.                                                                                                                                                                              |

| VCC      | 11  | Power                               |                        | 1.8V (±10%) Supply.                                                                                                                                                                                                                                                   |

| VREG_OUT | 12  | Power                               |                        | 1.2 V Regulator Output. Requires a 0.1 µF capacitor to GND.                                                                                                                                                                                                           |

| EQ/SCL   | 13  | I/O<br>(3-level)                    | PU (100K)<br>PD (100K) | RX Equalization Select. Pin state sampled on rising edge of RSTN. This pin also functions as I2C SCL pin. $V_{IL}=0~\text{dB} \\ V_{IM}=2.5~\text{dB} \\ V_{IH}=5~\text{dB}$                                                                                          |

| ERC/SDA  | 14  | I/O<br>(3-level)                    | PU (100K)<br>PD (100K) | Edge Rate Control for DB[4:0]P/N High speed transmitter rise and fall time. Pin state sampled on rising edge of RSTN. This pin also functions as I2C SDA pin. $V_{IL} = 200 \text{ ps typical} \\ V_{IM} = 150 \text{ ps typical} \\ V_{IH} = 250 \text{ ps typical}$ |

# Pin Functions (continued)

| PI         | N           |                        | INTERNAL               |                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-------------|------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.         | I/O                    | PULLUP/PULLDOWN        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                            |

| DB3N       | 15          | 100-Ω<br>Differential  |                        | CSI-2/DSI Lane 3 Differential negative Output. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                         |

| DB3P       | 16          | Output                 |                        | CSI-2/DSI Lane 3 Differential positive Output. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                         |

| DB2N       | 17          | 100-Ω<br>Differential  |                        | CSI-2/DSI Lane 2 Differential negative Output. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                         |

| DB2P       | 18          | Output                 |                        | CSI-2/DSI Lane 2 Differential positive Output. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                         |

| DBCN       | 19          | 100-Ω                  |                        | CSI-2/DSI Differential Clock negative Output                                                                                                                                                                                                                                                                                                                                           |

| DBCP       | 20          | Differential<br>Output |                        | CSI-2/DSI Differential Clock positive Output                                                                                                                                                                                                                                                                                                                                           |

| DB1N       | 21          | 100-Ω<br>Differential  |                        | CSI-2/DSI Lane 1 Differential negative Output. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                         |

| DB1P       | 22          | Output                 |                        | CSI-2/DSI Lane 1 Differential positive Output. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                         |

| DB0N       | 23          | 100-Ω<br>Differential  |                        | CSI-2/DSI Lane 0 Differential negative Output. Supports DSI LP Back channel. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                           |

| DB0P       | 24          | Output                 |                        | CSI-2/DSI Lane 0 Differential positive Output. Supports DSI LP Back channel. If unused, this pin should be left unconnected.                                                                                                                                                                                                                                                           |

| VDD        | 25          | Power                  |                        | This pin must be connected to the VREG_OUT pin through at least a 10-mil trace and a 0.1 $\mu\text{F}$ capacitor to ground.                                                                                                                                                                                                                                                            |

| PRE_CFG1   | 26          | I/O<br>(3-level)       | PU (100K)<br>PD (100K) | Controls DPHY TX HS pre-emphasis level and the LP TX rise and fall times. Pin state is sampled on the rising edge of RSTN. $V_{IL}=0~\text{dB} \\ V_{IM}=0~\text{dB} \\ V_{IH}=2.5~\text{dB}$                                                                                                                                                                                          |

| VSADJ_CFG0 | 27          | l<br>(3-level)         | PU (100K)<br>PD (100K) | Controls output voltage swing for DB HS transmitters and the LP TX rise and fall times. Pin state is sampled on the rising edge of RSTN. Refer to Table 3 for details on voltage swing settings based on this pin and PRE_CFG1 sampled state.  V <sub>IL</sub> = 200 mV or 220 mV based on PRE_CFG1 sampled state.  V <sub>IM</sub> = 200 mV typical  V <sub>IH</sub> = 220 mV typical |

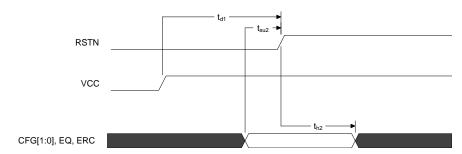

| RSTN       | 28          | I                      | PU (300K)              | Reset, active low. When low, all internal CSR are reset to default and DPHY440 is placed in low power state.                                                                                                                                                                                                                                                                           |

| GND        | Thermal pad | GND                    |                        | Ground.                                                                                                                                                                                                                                                                                                                                                                                |

Copyright © 2016–2019, Texas Instruments Incorporated

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                    | MIN  | MAX   | UNIT |

|---------------------------------------|------------------------------------|------|-------|------|

| Supply voltage range                  | V <sub>CC</sub>                    | -0.3 | 2.175 | V    |

|                                       | DPHY Lane I/O Differential Voltage | -0.3 | 1.4   | V    |

| Voltage range                         | RSTN                               | -0.3 | 2.175 | V    |

|                                       | All other terminals                | -0.3 | 2.175 | V    |

| Maximum junction tempera              | ature, T <sub>J</sub>              |      | 105   | °C   |

| Storage temperature, T <sub>stg</sub> |                                    | -65  | 150   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                 | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)          | ±3000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                | MIN  | NOM | MAX  | UNIT |

|----------------|------------------------------------------------|------|-----|------|------|

| $V_{CC}$       | Supply voltage                                 | 1.62 | 1.8 | 1.98 | V    |

| T <sub>A</sub> | Operating free-air temperature [SN65DPHY440SS] | -40  |     | 85   | °C   |

|                | Operating free-air temperature [SN75DPHY440SS] | 0    |     | 70   |      |

#### 6.4 Thermal Information

|                      |                                              | SNx5DPHY440SS |      |

|----------------------|----------------------------------------------|---------------|------|

|                      | THERMAL METRIC (1)                           | RHR (WQFN)    | UNIT |

|                      |                                              | 12 PINS       |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 42.1          | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 32.3          | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 12.8          | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.5           | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 12.6          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 5.2           | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics, Power Supply

over operating free-air temperature range (unless otherwise noted)

|             |                                                        |                                                                                       | MIN | NOM  | MAX | UNIT |

|-------------|--------------------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-----|------|

| PACTIVE1_SS | Power under normal operation for 4 data lanes + clock. | DPHY Lanes at 1 Gbps; $V_{CC}$ supply stable, $V_{CC} = 1.8 \text{ V}$ ;              |     | 150  |     | mW   |

| PACTIVE2_SS | Power under normal operation for 2 data lanes + clock. | DPHY Lanes 1 Gbps; V <sub>CC</sub> supply stable, V <sub>CC</sub> = 1.8 V;            |     | 115  |     | mW   |

| PLP11_SS    | LP11 Power                                             | All DPHY lanes in LP11; $V_{CC}$ supply stable; $V_{CC} = 1.8 \text{ V}$ ;            |     | 14   |     | mW   |

| PRSTN_SS    | RSTN Power                                             | RSTN held in asserted state (low); $V_{CC}$ supply stable; $V_{CC} = 1.8 \text{ V}$ ; |     | 0.75 |     | mW   |

### 6.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                  |                                                                                                                                                   | TEST CONDITIONS                                                                       | MIN                   | TYP                 | MAX                   | UNIT |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|------|

| Standard IO (R             | STN, ERC, EQ, CFG[1:0])                                                                                                                           |                                                                                       |                       |                     | •                     |      |

| V <sub>IL</sub>            | Low-level control signal input voltage                                                                                                            |                                                                                       |                       |                     | 0.2 x V <sub>CC</sub> | V    |

| V <sub>IM</sub>            | Mid-level control signal input voltage                                                                                                            |                                                                                       |                       | V <sub>CC</sub> / 2 |                       | V    |

| V <sub>IH</sub>            | High-level control signal input voltage                                                                                                           |                                                                                       | 0.8 x V <sub>CC</sub> |                     |                       | V    |

| V <sub>F</sub>             | Floating Voltage                                                                                                                                  | V <sub>IN</sub> = High Impedance                                                      |                       | V <sub>CC</sub> / 2 |                       | V    |

| V <sub>OL</sub>            | Low level output voltage (open-drain).<br>ERC (SDA) only                                                                                          | At I <sub>OL</sub> max.                                                               |                       |                     | 0.2 x V <sub>CC</sub> | V    |

| loL                        | Low Level Output Current                                                                                                                          |                                                                                       |                       |                     | 3                     | mA   |

| Ін                         | High level input current                                                                                                                          |                                                                                       |                       |                     | ±36                   | μΑ   |

| I <sub>IL</sub>            | Low level input current                                                                                                                           |                                                                                       |                       |                     | ±36                   | μA   |

| R <sub>PU</sub>            | Internal pull-up resistance                                                                                                                       |                                                                                       |                       | 100                 |                       | kΩ   |

| R <sub>PD</sub>            | Internal pull-down resistance                                                                                                                     |                                                                                       |                       | 100                 |                       | kΩ   |

| R <sub>(RSTN)</sub>        | RSTN control input pullup resistor                                                                                                                |                                                                                       |                       | 300                 |                       | kΩ   |

| MIPI Input Leal            | kage (DA1P/N, DA2P/N, DA3P/N, DACP/N)                                                                                                             |                                                                                       |                       |                     | <u> </u>              |      |

| I <sub>lkg</sub>           | Input failsafe leakage current                                                                                                                    | $V_{CC} = 0 \text{ V}; V_{DD} = 0 \text{ V}; \text{MIPI DPHY pulled}$<br>up to 1.35 V | -65                   |                     | 65                    | μAV  |

| MIPI DPHY HS               | RECIEVER INTERFACE (DA0P/N, DA1P/N                                                                                                                | , DA2P/N, DA3P/N, DACP/N)                                                             |                       |                     |                       |      |

| V <sub>(CM-RX_DC)</sub>    | Differential Input Common-mode voltage HS Receive mode                                                                                            | $V_{(CM-RX)} = (V_{A \times P} + V_{A \times N})/2$                                   | 70                    |                     | 330                   | mV   |

| V <sub>ID</sub>            | HS Receiver input differential voltage                                                                                                            | $ V_{ID}  =  V_{A \times P} - V_{A \times N} $                                        | 70                    |                     |                       | mV   |

| V <sub>IH(HS)</sub>        | Single-ended input high voltage                                                                                                                   |                                                                                       |                       |                     | 460                   | mV   |

| V <sub>IL(HS)</sub>        | Single-ended input low voltage                                                                                                                    |                                                                                       | -40                   |                     |                       | mV   |

| R <sub>(DIFF-HS)</sub>     | Differential input impedance                                                                                                                      |                                                                                       | 80                    | 100                 | 125                   | Ω    |

| V <sub>(RXEQ0)</sub>       | Rx EQ gain when EQ/SCL pin ≤ V <sub>IL</sub>                                                                                                      |                                                                                       |                       | 0                   |                       | dB   |

| V <sub>(RXEQ1)</sub>       | Rx EQ gain when EQ/SCL pin = V <sub>IM</sub>                                                                                                      | At 750 MHz                                                                            |                       | 2.5                 |                       | dB   |

| V <sub>(RXEQ2)</sub>       | Rx EQ gain when EQ/SCL pin ≥ V <sub>IH</sub>                                                                                                      | At 750 MHz                                                                            |                       | 5                   |                       | dB   |

| MIPI DPHY LP               | Receiver Interface (DA0P/N, DA1P/N, DA2                                                                                                           | P/N, DA3P/N, DACP/N, DB0P/N)                                                          |                       |                     |                       |      |

| V <sub>(LPIH)</sub>        | LP Logic 1 Input Voltage                                                                                                                          |                                                                                       | 880                   |                     |                       | mV   |

| V <sub>(LPIL)</sub>        | LP Logic 0 Input voltage                                                                                                                          |                                                                                       |                       |                     | 550                   | mV   |

| V <sub>(HYST)</sub>        | LP Input Hysteresis                                                                                                                               |                                                                                       | 25                    |                     |                       | mV   |

| MIPI DPHY HS               | Transmitter Interface (DB0P/N, DB1P/N, D                                                                                                          | DB2P/N, DB3P/N, DBCP/N)                                                               |                       |                     | <u> </u>              |      |

| V <sub>(CMTX)</sub>        | HS Transmit static common-mode voltage                                                                                                            | $V_{(CMTX)} = (V_{(BP)} + V_{(BN)}) / 2$                                              | 150                   | 200                 | 300                   | mV   |

| ΔV <sub>(CMTX) (1,0)</sub> | VCMTX mismatch when output is Differential-1 or differential-0.                                                                                   | $\Delta V_{(CMTX) (1,0)} = (V_{(CMTX) (1)} - V_{(CMTX) (0)})/2$                       |                       |                     | 5                     | mV   |

| V <sub>OD(VD0)</sub>       | HS Transmit differential voltage for CFG0 = 2'b00 with TX pre-emphasis disabled or for non-transition bit when TX pre-emphasis is enabled.        | $ V_{OD}  =  V_{(DP)} - V_{(DN)} $                                                    | 140                   | 180                 | 220                   | mV   |

| V <sub>OD(VD1)</sub>       | HS Transmit differential voltage for CFG0 = $V_{\rm IM}$ with TX pre-emphasis disabled or for non-transition bit when TX pre-emphasis is enabled. | $ V_{OD}  =  V_{(DP)} - V_{(DN)}  CFG0 = V_{IM}$                                      | 160                   | 200                 | 250                   | mV   |

Copyright © 2016–2019, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                                                                                     | TEST CONDITIONS                                               | MIN | TYP | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OD(VD2)</sub> | HS Transmit differential voltage for CFG0 = $V_{\rm IH}$ with TX pre-emphasis disabled or for non-transition bit when pre-emphasis is enabled | $ V_{OD}  =  V_{(DP)} - V_{(DN)}  \text{ CFG0} \ge V_{IH}$    | 170 | 220 | 270 | mV   |

| ΔV <sub>OD</sub>     | V <sub>OD</sub> mismatch when output is differential-1 or differential-0.                                                                     | $\Delta V_{OD} =  \Delta V_{O(D1)}  -  \Delta V_{O(D0)} $     |     |     | 14  | mV   |

| V <sub>OH(HS)</sub>  | HS Output high voltage for non-transition bit.                                                                                                | age for non-<br>CFG0 ≥ V <sub>IH</sub> HS Pre = 2.5 dB        |     | 430 | mV  |      |

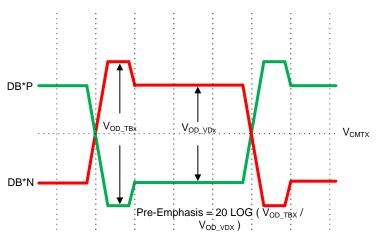

| V <sub>(PRE1)</sub>  | Pre-emphasis Level for HSTX_PRE = 2'b00 Refer to Figure 3                                                                                     | PRE = 20 x LOG (V <sub>OD(TBx)</sub> / V <sub>OD(VDX)</sub> ) |     | 1.5 |     | dB   |

| V <sub>(PRE2)</sub>  | Pre-emphasis level for HSTX_PRE = 2'b1X. Refer to Figure 3                                                                                    | PRE = 20 x LOG (V <sub>OD(TBx)</sub> / V <sub>OD(VDX)</sub> ) |     | 2.5 |     | dB   |

| MIPI DPHY L          | P Transmitter Interface (DB0P/N, DB1P/N, D                                                                                                    | DB2P/N, DB3P/N, DBCP/N, DA0P/N)                               | •   |     | •   |      |

| V <sub>(LPOH)</sub>  | LP Output High Level                                                                                                                          |                                                               | 1.1 | 1.2 | 1.3 | V    |

| V <sub>(LPOL)</sub>  | LP Output Low Level                                                                                                                           |                                                               | -50 |     | 50  | mV   |

| V <sub>IH(CD)</sub>  | LP Logic 1 contention threshold                                                                                                               |                                                               | 450 |     |     | mV   |

| V <sub>IL(CD)</sub>  | LP Logc 0 contention threshold                                                                                                                |                                                               |     |     | 200 | mV   |

| Z <sub>O(LP)</sub>   | Output Impedance of LP transmitter                                                                                                            |                                                               | 110 |     |     | Ω    |

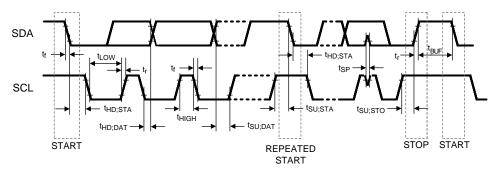

# 6.7 Timing Requirements

|                                |                                                          |                                                     | MIN      | NOM MAX  | UNIT |

|--------------------------------|----------------------------------------------------------|-----------------------------------------------------|----------|----------|------|

| I2C (ERC (S                    | DA), EQ (SCL))                                           |                                                     |          |          |      |

| t <sub>HD;STA</sub>            | Hold Time (repeated) START condition. After this period, | the first clock pulse is generated                  | 4        |          | μs   |

| t <sub>LOW</sub>               | Low period of SCL clock                                  |                                                     | 4.7      |          | μs   |

| t <sub>HIGH</sub>              | High period of SCL clock                                 |                                                     | 4        |          | μs   |

| t <sub>SU;STA</sub>            | Setup time for a repeated START condition                |                                                     | 4.7      |          | μs   |

| t <sub>HD;DAT</sub>            | Data hold time                                           |                                                     | 5        |          | μs   |

| t <sub>SU;DAT</sub>            | Data setup time                                          |                                                     | 4        |          | μs   |

| t <sub>SU;STO</sub>            | Setup time for STOP condition                            |                                                     | 4        |          | μs   |

| t <sub>BUF</sub>               | Bus free time between a STOP and START condition         |                                                     | 4.7      |          | μs   |

| MIPI DPHY I                    | HS Interface                                             |                                                     |          | ·        |      |

| t <sub>HSPD</sub>              | Propagation delay from DA to DB.                         |                                                     | 4 + 12ns | 4 + 40ns | UI   |

| t <sub>DBC_DCYCLE</sub>        | DAC to DBC output duty cycle distortion percentage       | 750 MHz clock with 50%-50% duty cycle at DAC input. | -5       | 5        | %    |

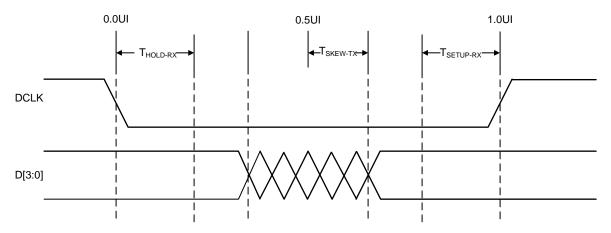

| t <sub>SKEW-TX-1G</sub>        | Data to Clock variation from 0.5UI. Refer to Figure 2    | Datarate ≤ 1 Gbps                                   | -0.1     | 0.1      | UI   |

| t <sub>SETUP-RX-1G</sub>       | Data to Clock setup time. Refer to Figure 2              | Datarate ≤ 1 Gbps                                   | 0.1      |          | UI   |

| t <sub>HOLD-RX-1G</sub>        | Clock to data hold time. Refer to Figure 2               | Datarate ≤ 1 Gbps                                   | 0.1      |          | UI   |

| t <sub>SKEW-TX-1P5G</sub>      | Data to Clock variation from 0.5UI. Refer to Figure 2    | Datarate > 1 Gbps                                   | -0.15    | 0.15     | UI   |

| t <sub>SETUP-RX-</sub><br>1P5G | Data to Clock setup time. Refer to Figure 2              | Datarate > 1 Gbps                                   | 0.15     |          | UI   |

| t <sub>HOLD-RX-1P5G</sub>      | Clock to data hold time. Refer to Figure 2               | Datarate > 1 Gbps                                   | 0.15     |          | UI   |

Product Folder Links: SN65DPHY440SS SN75DPHY440SS

# 6.8 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                             | TEST CONDITIONS                                                            | MIN | TYP (1) | MAX  | UNIT   |

|----------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----|---------|------|--------|

| I2C (ERC (SDA)             | ), EQ (SCL))                                          |                                                                            |     |         |      |        |

| F <sub>(SCL)</sub>         | I2C Clock Freqency                                    |                                                                            |     |         | 100  | kHz    |

| t <sub>F_I2C</sub>         | Fall time of both SDA and SCL signals                 | Load of 350 pF with 2-K pullup                                             |     |         | 300  | ns     |

| t <sub>R_I2C</sub>         | Rise Time of both SDA and SCL signals                 | resistor.<br>Measure at 30% - 70%                                          |     |         | 1000 | ns     |

| DPHY LINK                  |                                                       |                                                                            |     |         | ,    |        |

| F <sub>(BR)</sub>          | Bit Rate                                              |                                                                            |     |         | 1.5  | Gbps   |

| F <sub>(HSCLK)</sub>       | HS Clock Input range                                  |                                                                            | 100 |         | 750  | MHz    |

| F <sub>(DESKEW)</sub>      | Automatic Deskew range                                |                                                                            | 220 |         | 750  | MHz    |

|                            | Receiver Interface (DA0P/N, DA1P/N, DA2P              | /N, DA3P/N, DACP/N)                                                        |     |         | ,    |        |

| $\Delta V_{(CMRX\_HF)}$    | Common-mode Interface beyond 450 MHz                  | Z                                                                          |     |         | 100  | mV     |

| $\Delta V_{(CMRX\_LF)}$    | Common-mode interference 50 MHz – 450                 | ) MHz                                                                      | -50 |         | 50   | mV     |

| MIPI DPHY HS               | Transmitter Interface (DB0P/N, DB1P/N, DE             | 2P/N, DB3P/N, DBCP/N)                                                      |     |         | ,    |        |

| $\Delta V_{(CMRX\_HF)}$    | Common-level variations above 450 MHz                 |                                                                            |     |         | 5    | mVrms  |

| $\Delta V_{(CMRX\_LF)}$    | Common-level variation between 50 MHz                 | – 450 MHz.                                                                 |     |         | 25   | mVpeak |

|                            |                                                       | Datarate ≤ 1 Gbps                                                          |     |         | 0.3  | UI     |

| $t_R$ and $t_F$            | 20% - 80% rise time and fall time                     | Datarate > 1 Gbps                                                          |     |         | 0.35 | UI     |

|                            |                                                       |                                                                            | 100 |         |      | ps     |

| MIPI DPHY LP               | Receiver Interface (DA0P/N, DA1P/N, DA2P              | /N, DA3P/N, DACP/N, DB0P/N)                                                |     |         |      |        |

| e <sub>SPIKE</sub>         | Input Pulse rejection                                 |                                                                            |     |         | 300  | V ps   |

| t <sub>MIN(RX)</sub>       | Minimum pulse width response                          |                                                                            | 20  |         |      | ns     |

| V <sub>(INT)</sub>         | Peak interference amplitude                           |                                                                            |     |         | 200  | mv     |

| F <sub>(INT)</sub>         | Interference Frequency                                |                                                                            | 450 |         |      | Mhz    |

| t <sub>(LP-PULSE-RX)</sub> | Pulse Width of the XOR of DAxP and DAxN               | First LP XOR clock pulse after Stop state or last pulse before Stop state. | 42  |         |      | ns     |

|                            |                                                       | All other pulses.                                                          | 22  |         |      | ns     |

| MIPI DPHY LP               | Transmitter Interface (DB0P/N, DB1P/N, DB             | 2P/N, DB3P/N, DBCP/N, DA0P/N)                                              |     |         |      |        |

| t <sub>REOT</sub>          | 30% - 85% rise time and fall time                     | Measured at end of HS transmission.                                        |     |         | 35   | ns     |

| t <sub>(LP-PULSE-TX)</sub> | Pulse Width of the LP XOR clock                       | First LP XOR clock pulse after Stop state or last pulse before Stop state  | 40  |         |      | ns     |

|                            |                                                       | All other pulses                                                           | 20  |         |      | ns     |

| t <sub>(LP-PER-TX)</sub>   | Period of the LP XOR clock                            |                                                                            | 90  |         |      | ns     |

|                            | Slew Rate at C <sub>LOAD</sub> = 70 pF                |                                                                            |     |         | 150  | mV/ns  |

| δV/δtsr                    | Slew Rate at C <sub>LOAD</sub> = 0 pF Falling edge or | ly                                                                         | 30  |         |      | mV/ns  |

|                            | Slew Rate at C <sub>LOAD</sub> = 0 pF Rising edge or  |                                                                            | 30  |         |      | mV/ns  |

| C <sub>LOAD</sub>          | Load Capacitance                                      |                                                                            |     |         | 70   | pF     |

## (1) (1) All typical values are at $V_{CC} = 3.3 \text{ V}$ , and $T_A = 25^{\circ}\text{C}$ .

Figure 1. I<sup>2</sup>C Timing

Figure 2. DPHY HS RX and TX Timing

Figure 3. DPHY HS TX Pre-emphasis

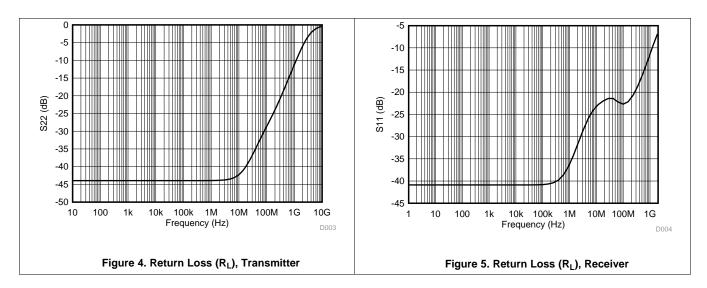

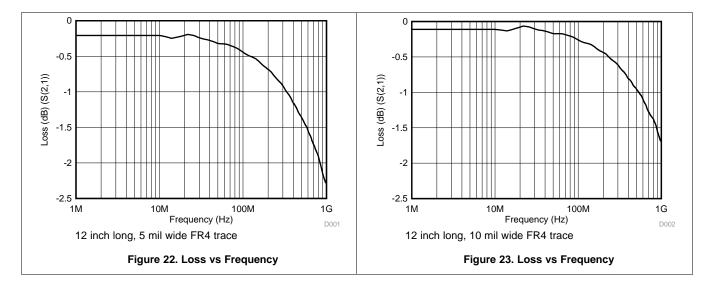

# 6.9 Typical Characteristics

Submit Documentation Feedback

Copyright © 2016–2019, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

The DPHY440SS is a one to four lane and clock MIPI DPHY re-driver that regenerates the DPHY signaling. The device complies with MIPI DPHY 1.1 standard and can be used in either a MIPI CSI-2 or MIPI DSI application at datarates of up to 1.5 Gbps.

The device compensates for PCB, connector, and cable related frequency loss and switching related loss to provide the optimum electrical performance from a CSI2/DSI source to sink. The DPHY440 DPHY inputs feature configurable equalizers.

The output pins will automatically compensate for uneven skew between clock and data lanes. The DPHY440 output swing and edge rate can be adjusted by changing the state of the VSADJ\_CFG0 pin and ERC pin respectively.

The DPHY440 is optimized for mobile applications, and contains activity detection circuitry on the DPHY Link interface that can transition into a lower power mode when in ULPS and LP states.

The device is characterized for an extended operational temperature range from -40°C to 85°C.

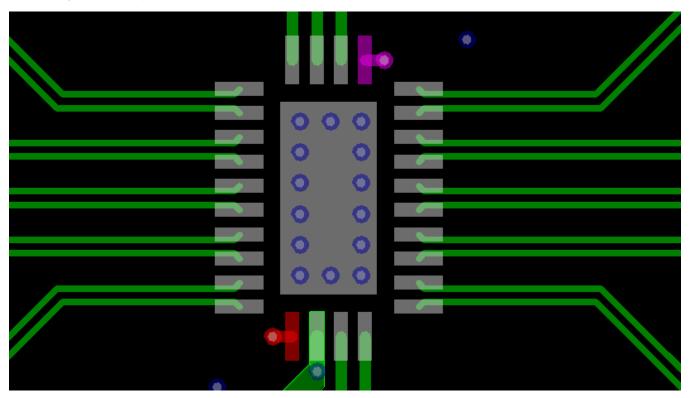

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

### 7.3.1 HS Receive Equalization

The DPHY440 supports three levels of receive equalization to compensate for ISI loss in the channel. These three levels are 0 dB, 2.5 dB, and 5 dB at 750MHz. The equalization level used by the DPHY440 is determined by the state of the EQ/SCL pin at the rising edge of RSTN. If necessary, the receiver equalization level can also be set through writing to the RXEQ register via the local I2C interface

Table 1. EQ/SCL pin Function

| EQ/SCL PIN        | HS Rx EQUALIZATION                    |

|-------------------|---------------------------------------|

| ≤ V <sub>IL</sub> | 0 dB                                  |

| V <sub>IM</sub>   | 2.1 dB at 500 MHz / 2.5 dB at 750 MHz |

| ≥ V <sub>IH</sub> | 4 dB at 500 MHz / 5 dB at 750 MHz     |

### 7.3.2 HS TX Edge Rate Control

The DPHY440 supports control of the rise and fall time for the DB[3:0]P/N and DBCP/N High Speed (HS) transmitters. Depending on system operating datarate, the HS edge rate may need to be adjusted to help improve EMI performance. The HS edge rate setting is determined through the sampled state of ERC/SDA pin at the rising edge of RSTN. If necessary, the HS edge rate can be adjusted by writing to the HS\_ERC register via the local I2C interface.

Table 2. 8.3.2 HS TX Edge Rate Control

| ERC/SDA PIN       | HS RISE/FALL TIMES |

|-------------------|--------------------|

| ≤ V <sub>IL</sub> | 200 ps typical     |

| V <sub>IM</sub>   | 150 ps typical     |

| ≥ V <sub>IH</sub> | 250 ps typical     |

The DPHY440 also supports edge rate control for the LP interface. The adjustment of LP TX edge rate is determined by the state of the VSADJ\_CFG0 and PRE\_CFG1 pins as depicted in Table 3, but can also be modified by changing LP\_ERC register through the local I2C interface

#### 7.3.3 TX Voltage Swing and Pre-Emphasis Control

In some applications, the DPHY440 may be placed at a location in the system where the channel from DPHY440 DB[3:0]P/N interface to the DPHY Sink (CSI-2 or DSI) is extremely long and the DPHY Sink does not have enough receive equalization to compensate for the ISI loss. In this application, the system architect may want to use the DPHY440 TX pre-emphasis feature to compensate for the lack of equalization at the DPHY sink. The DPHY440 provides two levels of pre-emphasis: 0 dB, and 2.5 dB. The TX Pre-emphasis settings is determined through the sampled sate of PRE\_CFG[1:0] pins at the rising edge of RSTN. If necessary, the TX Pre-emphasis settings can be adjusted by writing to the HSTX\_PRE register through the local I2C interface.

This feature must only be used when the HS pre-emphasis bit (transition bit) is attenuated by the channel. Enabling pre-emphasis in a system that has little channel loss (transition bit is not attenuated) may result in negative impact to system performance.

Table 3. HS Voltage Swing, HS Pre-emphasis, LPTX Edge Rate Controls

| VSADJ_CFG0        | PRE_CFG1          | HS TX VOD | HS TX PRE-EMPHASIS | DB[3:0] LP TX RISE/FALL<br>TIME |

|-------------------|-------------------|-----------|--------------------|---------------------------------|

| ≤V <sub>IL</sub>  | ≤ V <sub>IL</sub> | 200 mV    | 0 dB               | 18 ns                           |

| $V_{IM}$          | ≤ V <sub>IL</sub> | 200 mV    | 0 dB               | 27 ns                           |

| ≥ V <sub>IH</sub> | ≤ V <sub>IL</sub> | 220 mV    | 0 dB               | 18 ns                           |

| ≤V <sub>IL</sub>  | V <sub>IM</sub>   | 200 mV    | 0 dB               | 27 ns                           |

| V <sub>IM</sub>   | V <sub>IM</sub>   | 200 mV    | 0 dB               | 21 ns                           |

| ≥ V <sub>IH</sub> | V <sub>IM</sub>   | 220 mV    | 0 dB               | 21 ns                           |

| ≤V <sub>IL</sub>  | ≥ V <sub>IH</sub> | 220 mV    | 2.5 dB             | 27 ns                           |

| V <sub>IM</sub>   | ≥ V <sub>IH</sub> | 200 mV    | 2.5 dB             | 21 ns                           |

| ≥ V <sub>IH</sub> | ≥ V <sub>IH</sub> | 220 mV    | 2.5 dB             | 21 ns                           |

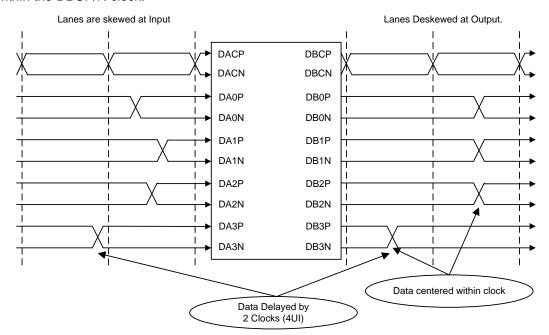

## 7.3.4 Dynamic De-skew

The DPHY440 implements a dynamic de-skew feature which will continuously de-skew the HS data received on the DA[3:0]P/N interface and provide a retimed version on the DB[3:0]P/N interface. The retimed version is centered within the DBCP/N clock.

Figure 6. Dynamic De-skew

#### **NOTE**

The dynamic de-skew feature is only enabled in HS mode, and causes a 2 clock (4 UI) delay of data while data traverses from DA to DB.

Copyright © 2016–2019, Texas Instruments Incorporated

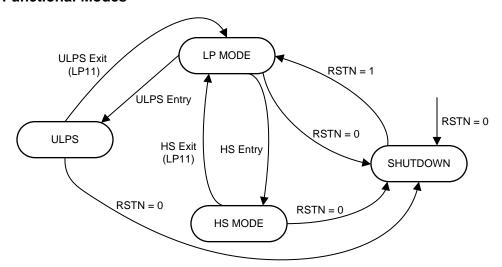

#### 7.4 Device Functional Modes

Figure 7. Functional Modes

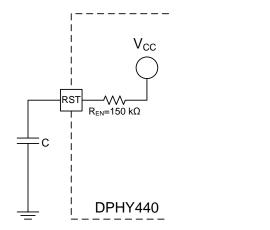

#### 7.4.1 Shutdown Mode

The DPHY440 can be placed into a low power consumption state by asserting the RSTN pin low while maintaining a stable  $V_{CC}$  and  $V_{DD}$  power supply. While in the Shutdown state, the DPHY440 drives DB[3:0]P/N and DBCP/N pins to the LP00 state. The DPHY440 ignores all activity on the DA[3:0]P/N and DACP/N pins while in Shutdown mode. The Shutdown mode is exited by de-asserting the RSTN pin high. Upon exiting Shutdown mode, the DPHY440 enters LP Mode operation and pass what is received on the DA interface to the DB interface.

#### 7.4.2 LP Mode

In this mode, the DPHY440 passes LP signals between DA[3:0]P/N and DB[3:0]P/N. The internal terminations for the HS receiver and HS transmitter are disabled when operating in this mode.

The MIPI DSI specification defines bidirectional communication between the host and peripheral. When a response is needed by the peripheral, the response is returned using LP signaling from DB0P/N to DA0P/N. The DPHY440 only supports this communication over lane 0 (DB0P/N to DA0P/N). The remaining lanes cannot be used for LP communications from peripheral to host (reverse direction).

#### 7.4.3 ULPS Mode

The DPHY440 is continuously monitoring the DPHY LP protocol for entry into the ULPS state. Upon entry into the ULPS state, the DPHY440 keeps active the logic necessary for LP signaling (LP rx, LPtx, LP state machine, so forth). All logic needed for HS operation are disabled. This allows for a lower power state than can be achieved when in operating other LP power states.

NOTE

ULPS mode can only be entered from LP Mode.

#### 7.4.4 HS Mode

The HS mode is entered when the required sequence of LP signals is detected by the LP state machine. In this mode, the internal termination for both the HS receiver and HS transmitter is enabled and the dynamic de-skew feature is enabled. The DPHY440 remains in this mode until a HS exit is detected by the LP state machine. Upon detecting the HS exit, the DPHY440 immediately transitions to *LP Mode*.

#### 7.5 Register Maps

The DPHY440 local I2C interface is enabled when RSTN is input high. Access to the CSR registers is supported during ultra-low power state (ULPS). The EQ/SCL and ERC/SDA terminals are used for I<sup>2</sup>C clock and I<sup>2</sup>C data respectively. The DPHY440 I2C interface conforms to the two-wire serial interface defined by the I<sup>2</sup>C Bus Specification, Version 2.1 (January 2000) and supports up to 100 kHz.

The device address byte is the first byte received following the START condition from the master device. The 7 bit device address for DPHY440 is factory preset to 1101100.

Table 4. DPHY440 I<sup>2</sup>C Target Address Description

| Bit 7 (MSB)                                   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (W/R) |  |  |  |

|-----------------------------------------------|-------|-------|-------|-------|-------|-------|-------------|--|--|--|

| 1                                             | 1     | 0     | 1     | 1     | 0     | 0     | 0/1         |  |  |  |

| Address Cycle is 0xD8 (Write) and 0xD9 (Read) |       |       |       |       |       |       |             |  |  |  |

The following procedure should be followed to write to the DPHY440 I<sup>2</sup>C registers:

- 1. The master initiates a write operation by generating a start condition (S), followed by the DPHY440 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The DPHY440 acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within DPHY440) to be written, consisting of one byte of data, MSB-first

- 4. The DPHY440 acknowledges the sub-address cycle.

- 5. The master presents the first byte of data to be written to the I<sup>2</sup>C register.

- 6. The DPHY440 acknowledges the byte transfer.

- 7. The master may continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the DPHY440.

- 8. The master terminates the write operation by generating a stop condition (P).

The following procedure should be followed to read the DPHY440 I<sup>2</sup>C registers:

- 1. The master initiates a read operation by generating a start condition (S), followed by the DPHY440 7-bit address and a one-value "W/R" bit to indicate a read cycle

- 2. The DPHY440 acknowledges the address cycle.

- 3. The DPHY440 transmit the contents of the memory registers MSB-first starting at register 00h or last read sub-address+1. If a write to the DPHY440 I<sup>2</sup>C register occurred prior to the read, then the DPHY440 starts at the sub-address specified in the write.

- 4. The DPHY440 will wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master after each byte transfer; the I2C master acknowledges reception of each data byte transfer.

- 5. If an ACK is received, the DPHY440 transmits the next byte of data.

- 6. The master terminates the read operation by generating a stop condition (P).

The following procedure should be followed for setting a starting sub-address for I<sup>2</sup>C reads:

- 1. The master initiates a write operation by generating a start condition (S), followed by the DPHY440 7-bit address and a zero-value "W/R" bit to indicate a write cycle.

- 2. The DPHY440 acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within DPHY440) to be written, consisting of one byte of data, MSB-first.

- 4. The DPHY440 acknowledges the sub-address cycle.

- 5. The master terminates the write operation by generating a stop condition (P).

#### NOTE

If no sub-addressing is included for the read procedure, and reads start at register offset 00h and continue byte by byte through the registers until the I2C master terminates the read operation. If a  $\rm I^2C$  write occurred prior to the read, then the reads start at the sub-address specified by the write.

Copyright © 2016–2019, Texas Instruments Incorporated

#### 7.5.1 BIT Access Tag Conventions

A table of bit descriptions is typically included for each register description that indicates the bit field name, field description, and the field access tags. The field access tags are described in Table 5.

**Table 5. Tag Conventions**

| ACCESS TAG | NAME      | DEFINITION                                                                             |

|------------|-----------|----------------------------------------------------------------------------------------|

| R          | Read      | The field may be read by software.                                                     |

| W          | Write     | The field may be written by software                                                   |

| S          | Set       | The field may be set by a write of one. Writes of zero to the field have no effect.    |

| С          | Clear     | The field may be cleared by a write of one. Write of zero to the field have no effect. |

| U          | Update    | Hardware may autonomously update this field                                            |

| N/A        | No Access | Not accessible or not applicable                                                       |

### 7.5.2 Standard CSR Registers (address = 0x000 - 0x07)

Figure 8. Standard CSR Registers (0x000 - 0x07)

| 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------|---|---|---|---|---|---|---|--|--|

| DEVICE_ID   |   |   |   |   |   |   |   |  |  |

| R R R R R R |   |   |   |   |   |   |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 6. Standard CSR Registers (0x000 - 0x07)

| Bit | Field     | Туре | Reset | Description                                                                                                                                                     |

|-----|-----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DEVICE_ID | R    | 0     | For the DPHY440 these fields return a string of ASCII characters returning "DPHY100".  Addresses 0x07 - 0x00 = {0x20, 0x30, 0x30, 0x31, 0x59, 0x48, 0x50, 0x44} |

### 7.5.3 Standard CSR Register (address = 0x08)

#### Figure 9. Standard CSR Register (0x08)

| 7          | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------|-------------|---|---|---|---|---|---|--|--|--|

| DEVICE_REV |             |   |   |   |   |   |   |  |  |  |

| R          | R R R R R R |   |   |   |   |   |   |  |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 7. Standard CSR Register (0x08)

| Bit | Field      | Туре | Reset | Description      |

|-----|------------|------|-------|------------------|

| 7:0 | DEVICE_REV | R    | 0     | Device revision. |

Product Folder Links: SN65DPHY440SS SN75DPHY440SS

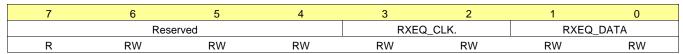

### 7.5.4 Standard CSR Register (address = 0x09)

### Figure 10. Standard CSR Register(0x09)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 8. Standard CSR Register (0x09)

| Bit | Field     | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                |

|-----|-----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved  | R    | 0     | Reserved                                                                                                                                                                                                                                                                                                                                                                   |

| 3:2 | RXEQ_CLK  | RW   | 0     | This field selects the EQ level of the DACP/N. The value in this field will match the sampled state of EQ/SCL pin at the rising edge of RSTN. Software can change the value of this field at a later time. $00-0 \text{ dB (EQ/SCL pin} = V_{IL})\\ 01-2.5 \text{ dB (EQ/SCL pin} = V_{IM})\\ 10-\text{Reserved}.\\ 11-5 \text{ dB (EQ/SCL pin} = V_{IH})$                 |

| 1:0 | RXEQ_DATA | RW   | 0     | This field selects the EQ level of the DA[3:0]P/N . The value in this field will match the sampled state of EQ/SCL pin at the rising edge of RSTN. Software can change the value of this field at a later time. $00-0~\text{dB. (EQ/SCL pin}=V_{\text{IL}})\\01-2.5~\text{dB (EQ/SCL pin}=V_{\text{IM}})\\10-\text{Reserved.}\\11-5~\text{dB. (EQ/SCL pin}=V_{\text{IH}})$ |

### 7.5.5 Standard CSR Register (address = 0x0A)

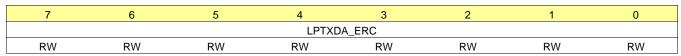

# Figure 11. Standard CSR Register (0x0A)

| 7     | 6     | 5     | 4          | 3 | 2        | 1  | 0       |  |

|-------|-------|-------|------------|---|----------|----|---------|--|

| LPTXD | A_ERC | LPTXD | LPTXDB_ERC |   | Reserved |    | HSC_ERC |  |

| RW    | RW    | RW    | RW         | R | R        | RW | RW      |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 9. Standard CSR Register (0x0A)

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | LPTXDA_ERC | RW   | 0     | This field controls the edge rate of the DA0P/N LP transmitters.  00 – 18 ns at 70 pF (Default)  01 – 21 ns at 70 pF  10 – 15 ns at 70 pF  11 – 27 ns at 70 pF                                                                                                                                                                                                |

| 5:4 | LPTXDB_ERC | RW   | 0     | This field controls the edge rate of the DB[3:0]P/N LP transmitters. The value in this field will be updated by hardware based on the state of the CFG[1:0] pin. Refer to Table 3 for settings based on sampled state of CFG[1:0] Software can change the value of this field at a later time.  00 – 18 ns at 70 pF  10 – 15 ns at 70 pF  11 – 27 ns at 70 pF |

| 3:2 | Reserved   | R    |       | Reserved                                                                                                                                                                                                                                                                                                                                                      |

| 1:0 | HSC_ERC    | RW   | 0     | This field controls the edge rate of the DBCP/N high speed transmitter. The value of this field will match the sampled state of the ERC pin. Software can change the value of this field at a later time. $00-200~ps~at~1~Gbps.~(ERC~pin=V_{IL})\\01-150~ps~at~1~Gbps.~(ERC~pin=V_{IM})\\10-250~ps~at~1~Gbps.~(ERC~pin=V_{IH})\\11-300~ps~at~1~Gbps$          |

Copyright © 2016–2019, Texas Instruments Incorporated

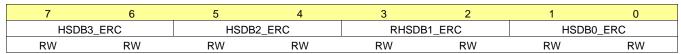

### 7.5.6 Standard CSR Register (address = 0x0B)

# Figure 12. Standard CSR Register (0x0B)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 10. Standard CSR Register (0x0B)

|     | 1          |      |                                                                                                                                                                                                                                                                                                                                                                         | <u> </u>                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|