# SiI9022A/SiI9024A HDMI Transmitter

Data Brief

Document # SiI-DB-1076-B

December 2009

#### **Copyright Notice**

Copyright © 2009 Silicon Image, Inc. All rights reserved. These materials contain proprietary and confidential information (including trade secrets, copyright and other interests) of Silicon Image, Inc. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/or services from Silicon Image or its affiliates, and/or only in connection with your purchase of products and/or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions herein. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of or distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

#### **Patents**

The subject matter described herein contains one or more inventions claimed in patents and / or patents pending owned by Silicon Image, Inc., including but not limited to the inventions claimed in US patents #6,914,637, #6,151,334, #6,026,124, #5,974,464 and #5,825,824.

#### **Trademark Acknowledgment**

Silicon Image<sup>TM</sup>, VastLane<sup>TM</sup>, SteelVine<sup>TM</sup>, PinnaClear<sup>TM</sup>, Simplay<sup>TM</sup>, Simplay HD<sup>TM</sup>, Satalink<sup>TM</sup>, Mobile High-definition Link<sup>TM</sup>, MHL<sup>TM</sup>, InstaPort<sup>TM</sup>, TMDS<sup>TM</sup>, and LiquidHD<sup>TM</sup> are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. HDMI<sup>®</sup>, the HDMI logo and High-Definition Multimedia Interface<sup>TM</sup> are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC. x.v.Color<sup>TM</sup> is a trademark of Sony Corporation.

#### **Further Information**

To request other materials, detailed hardware and software guides, and additional information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at <a href="www.siliconimage.com">www.siliconimage.com</a>. Information about obtaining licenses required for using HDMI and HDCP technologies is available from <a href="www.hdmi.org">www.hdmi.org</a> and <a href="www.digital-cp.com">www.digital-cp.com</a>.

© 2009 Silicon Image. Inc. All rights reserved.

## **General Description**

The SiI9022A/SiI9024A HDMI transmitter supports the High Definition Multimedia Interface (HDMI) Specification on a wide range of mobile products. High definition camcorders, digital still cameras, and personal mobile devices connect directly to a large installed base of HDMI TVs and DVI PC monitors by using the flexible audio and video interfaces provided by this ultra-low-power solution. S/PDIF or I<sup>2</sup>S inputs enable a pure digital audio connection to virtually any system audio processor or codec. This transmitter is the next generation of its family and is an enhanced replacement for the SiI9022/SiI9024 device, with lower power and enhanced features.

The SiI9024A transmitter supports High-bandwidth Digital Content Protection (HDCP) for devices that require secure content delivery.

### Video Input

- xvYCC metadata support

- BTA-T1004 video input format

- Integrated color space converter allows direct connection to all major MPEG decoders, including those that provide only an ITU-R.656 output

- Internal DE generator supports non-embedded sync formats.

### **HDMI Output**

- HDMI, HDCP, and DVI compatibile

- TMDS<sup>®</sup> core runs at 165 MHz

- Video resolutions up to 1080p and UXGA (72-pin QFN package supports 165-MHz dual-edge mode)

- The SiI9024A transmitter is pre-programmed with HDCP keys and has completely self-sequencing HDCP detection and authentication, including SHA-1 for repeaters.

### **Control Capability**

- Consumer Electronics Control (CEC) interface incorporates an HDMI-compliant CEC I/O with hardware protocol and arbitration logic, and requires no external calibration

- Monitor detection is supported through both Hot Plug and Receiver Sense circuits

- Single slave I<sup>2</sup>C from host, passing through to master I<sup>2</sup>C interface for DDC connection, simplifies board layout and lowers cost

- Defaults to SiI9020 transmitter register-compatible mode for operation with existing legacy software.

### **Digital Audio Interface:**

- Four I<sup>2</sup>S inputs for Dolby Digital, DTS, or MPEG2 audio with programmable channel mapping (49-ball package supports one I<sup>2</sup>S input)

- DVD-Audio input (2 or up to 8 channels)

- MCLK is not required for I<sup>2</sup>S and S/PDIF

- S/PDIF input supports 2-channel PCM or compressed Dolby Digital and DTS digital

- 2:1 and 4:1 down-sampling to handle 96-kHz and 192-kHz audio streams.

### **Power Management**

- Flexible power management with hot-plug wakeup

- Ultra low power requirement: less than 90 mW active, 150 μW standby.

### **Packaging**

- 81-ball VFBGA (4.0 x 4.0 mm) package

- 72-pin QFN (10 x 10 mm) package

- 49-ball VFBGA (4.0 x 4.0 mm) package

- Standard part covers extended (-20 to +85 °C) temperature range.

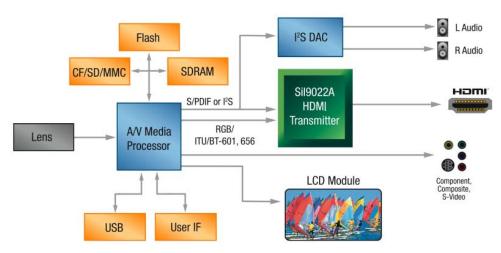

Figure 1. Typical Application (SiI9022A HDMI Transmitter Shown)

## Comparison of the SiI9022A/SiI9024A Device With Other HDMI **Transmitters**

Table 1 summarizes the differences among the previous Silicon Image HDMI transmitters and the SiI9022A/SiI9024A HDMI transmitters.

Table 1. Summary of Features

| <b>HDMI Transmitter</b>         | SiI9030        | Si19020          | SiI9022                                    | SiI9022-6         | SiI9024                                    | SiI9024-6         | SiI9022A                                   | SiI9024A                                   | SiI9022A                      | SiI9024A                       |

|---------------------------------|----------------|------------------|--------------------------------------------|-------------------|--------------------------------------------|-------------------|--------------------------------------------|--------------------------------------------|-------------------------------|--------------------------------|

|                                 | 8119030        | 5119020          | 5119022                                    | 8119022-6         | 8119024                                    | 8119024-6         | VFF                                        | BGA                                        | Q                             | FN                             |

| Video Input                     | •              |                  | •                                          |                   |                                            | •                 |                                            |                                            |                               |                                |

| Clock duty cycle                | 60/40          | 60/40            | 70/30                                      | 70/30             | 70/30                                      | 70/30             | 70/30                                      | 70/30                                      | 70/30                         | 70/30                          |

| Max frequency                   | 150 MHz        | 84 MHz           | 82.5 MHz                                   | 165 MHz           | 82.5 MHz                                   | 165 MHz           | 165 MHz                                    | 165 MHz                                    | 165 MHz <sup>3</sup>          | 165 MHz <sup>3</sup>           |

| Input signal level <sup>2</sup> | 3.3 V          | 3.3 V            | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8 V | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8 V | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8 V             | 3.3 V or<br>1.8 V              |

| Audio Input                     | •              |                  | •                                          |                   |                                            |                   |                                            |                                            |                               |                                |

| Max S/PDIF frequency            | 96 kHz         | 96 kHz           | 192 kHz                                    | 192 kHz           | 192 kHz                                    | 192 kHz           | 192 kHz                                    | 192 kHz                                    | 192 kHz                       | 192 kHz                        |

| I <sup>2</sup> S MCLK required? | Yes            | Yes              | Optional                                   | Optional          | Optional                                   | Optional          | Optional                                   | Optional                                   | Optional                      | Optional                       |

| S/PDIF MCLK required?           | Yes            | Yes              | Optional                                   | Optional          | Optional                                   | Optional          | Optional                                   | Optional                                   | Optional                      | Optional                       |

| DDC I <sup>2</sup> C Bus        |                |                  | •                                          |                   |                                            |                   |                                            |                                            |                               |                                |

| Voltage tolerance <sup>1</sup>  | 5 V            | 5 V              | 5 V                                        | 5 V               | 5 V                                        | 5 V               | 5 V                                        | 5 V                                        | 5 V                           | 5 V                            |

| HDCP                            |                |                  |                                            |                   |                                            |                   |                                            |                                            |                               |                                |

| Encryption engine               | Yes            | No               | No                                         | No                | Yes                                        | Yes               | No                                         | Yes                                        | No                            | Yes                            |

| Auto authentication             | No             | No               | No                                         | No                | Yes                                        | Yes               | No                                         | Yes                                        | No                            | Yes                            |

| Other                           |                |                  |                                            |                   |                                            |                   |                                            |                                            |                               |                                |

| Core power supply               | 1.8 V          | 1.8 V            | 1.2 V                                      | 1.2 V             | 1.2 V                                      | 1.2 V             | 1.2 V                                      | 1.2 V                                      | 1.2 V                         | 1.2 V                          |

| I/O power supply <sup>2</sup>   | 3.3 V          | 3.3 V            | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8 V | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8 V | 3.3 V or<br>1.8V                           | 3.3 V or<br>1.8 V                          | 3.3 V or<br>1.8V <sup>4</sup> | 3.3 V or<br>1.8 V <sup>4</sup> |

| Package                         | 80-pin<br>TQFP | 84-ball<br>TFBGA | 84-ball<br>TFBGA<br>or<br>81-ball<br>VFBGA | 84-ball<br>TFBGA  | 84-ball<br>TFBGA<br>or<br>81-ball<br>VFBGA | 84-ball<br>TFBGA  | 81-ball<br>VFBGA<br>or<br>49-ball<br>VFBGA | 81-ball<br>VFBGA<br>or<br>49-ball<br>VFBGA | 72-pin<br>QFN                 | 72-pin<br>QFN                  |

#### **Notes:**

- 1. I<sup>2</sup>C inputs are 3.3-V or 5-V tolerant only when chip IOVCC is applied, except in the case of the SiI9022A/SiI9024A devices, for which the state of chip IOVCC doesn't matter.

- The SiI9022A/SiI9024A 81-ball and 72-pin package supports both 1.8-V and 3.3-V threshold-compliant operation. The 49-ball package only supports 1.8-V compliant I/O. Both devices have 3.3-V tolerant I/O when IOVCC is

- 3. Supports up to 165 MHz dual-edge and single-edge modes.

- 4. For dual-edge mode above 82.5 MHz, only 3.3 V  $\pm$  10% can be used for IOVCC.

## **Ball and Pin Diagrams**

### 81-ball VFBGA Package

Figure 2 shows the ball diagram for the SiI9022A/SiI9024A transmitter in the 81-ball package. Balls are shaded using the grouping shown in Figure 4 on page 5.

|   | 1            | 2            | 3       | 4       | 5       | 6       | 7            | 8            | 9             |

|---|--------------|--------------|---------|---------|---------|---------|--------------|--------------|---------------|

| Α | HCTRL_<br>IO | RSVD         | GND     | HDATA_O | HDATA_O | HDATA_O | HDATA_O      | GND          | EXT_<br>SWING |

| В | CCTRL_<br>IO | VDD          | HDATA_O | HDATA_O | HDATA_O | HDATA_O | CCTRL_<br>IO | CCTRL_I      | RSVD          |

| С | CCTRL_<br>IO | CCTRL_<br>IO | CCTRL_I | CVCC12  | GND     | AVCC12  | AVCC12       | HCTRL_<br>IO | HCTRL_<br>IO  |

| D | GND          | GND          | VCC12   | GND     | vcc     | GND     | VCC12        | HCTRL_O      | CCTRL_O       |

| E | VDATA_1      | VDATA_1      | VDATA_1 | VDATA_1 | VCC     | ADATA_1 | VCC12        | vcc          | vcc           |

| F | VDATA_1      | VDATA_1      | VDATA_1 | VDATA_1 | VCC12   | ADATA_1 | ACTRL_1      | ACTRL_1      | ADATA_1       |

| G | VDATA_1      | VDATA_1      | VDATA_1 | VDATA_1 | GND     | VCC12   | ADATA_1      | ACTRL_1      | ADATA_1       |

| Н | VDATA_1      | VDATA_1      | VCTRL_1 | VDATA_1 | GND     | VDATA_1 | VDATA_1      | VDATA_1      | VCTRL_I       |

| J | VDATA_1      | VDATA_1      | VDATA_1 | VDATA_1 | GND     | VDATA_1 | VDATA_1      | VCTRL_I      | VCTRL_I       |

| Ball Name | Purpose                                                                    |

|-----------|----------------------------------------------------------------------------|

| VDATA_I   | Video data Input                                                           |

| VCTRL_I   | Video control Input                                                        |

| ADATA_I   | Audio data Input (S/PDIF, 1 <sup>2</sup> S)                                |

| ACTRL_I   | Audio control Input (WS, MCLK, SCK)                                        |

| CCTRL_x   | Chip control Input, Output, or Input/Output (INT, RESET, CSCL, CSDA, etc.) |

| HDATA_O   | HDMI data Output (TMDS-level signals)                                      |

| HCTRL_x   | HDMI control Input, Output, or Input/Output                                |

Figure 2. 81-ball Ball Diagram (Top View)

### 49-ball VFBGA Package

Figure 3 shows the ball diagram for the SiI9022A/SiI9024A transmitter in the 49-ball package. Balls are shaded using the grouping shown in Figure 4 on the next page.

| _ | 1        | 2            | 3       | 4       | 5        | 6                   | 7        |

|---|----------|--------------|---------|---------|----------|---------------------|----------|

| Α | HDATA_O  | HDATA_O      | HDATA_O | HDATA_O | HDATA_O  | HDATA_O             | HDATA_O  |

| В | HCTRL_IO | HDATA_O      | GND     | VCC12   | CCTRL_IO | RSVDL               | CCTRL_I  |

| С | CCTRL_IO | CCTRL_<br>IO | VDD     | VCC12   | CCTRL_I  | CCTRL_O             | CCTRL_IO |

| D | VDATA_I  | VDATA_I      | GND     | GND     | HCTRL_I  | ACTRL_I             | ADATA_I  |

| E | VDATA_I  | VDATA_I      | VCC     | VDATA_I | ACTRL_I  | VDATA_I             | ACTRL_I  |

| F | VDATA_I  | VDATA_I      | VCTRL_I | VDATA_I | VDATA_I  | VDATA_I             | VCTRL_I  |

| G | VDATA_I  | VDATA_I      | VDATA_I | VDATA_I | VDATA_I  | VCTRL_I/<br>ADATA_I | VCTRL_I  |

| <b>Ball Name</b> | Purpose                                                                    |

|------------------|----------------------------------------------------------------------------|

| VDATA_I          | Video data Input                                                           |

| VCTRL_I          | Video control Input                                                        |

| ADATA_I          | Audio data Input (S/PDIF, I <sup>2</sup> D)                                |

| ACTRL_I          | Audio control Input (WS, MCLK, SCK)                                        |

| CCTRL_x          | Chip control Input, Output, or Input/Output (INT, RESET, CSCL, CSDA, etc.) |

| HDATA_O          | HDMI data Output (TMDS-level signals)                                      |

| HCTRL_x          | HDMI control Input, Output, or Input/Output                                |

Figure 3. 49-ball Ball Diagram (Top View)

### 72-pin QFN Package

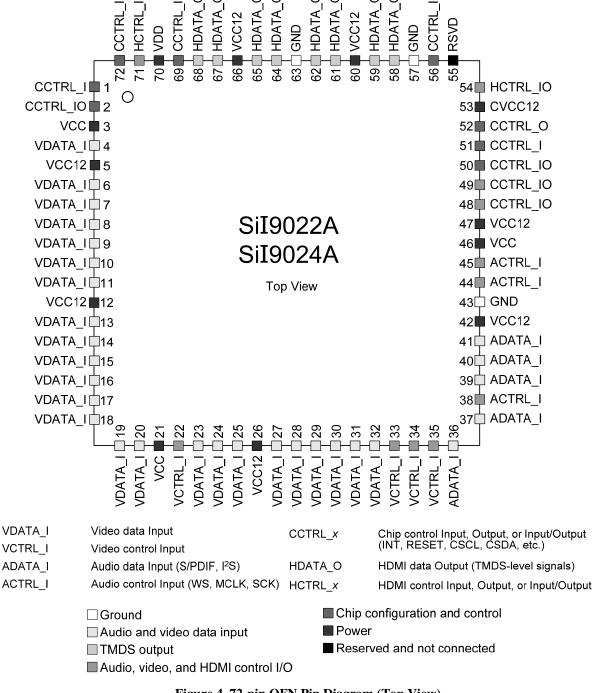

Figure 4 shows the pin diagram for the SiI9022A/SiI9024A transmitter in the 72-pin package.

Figure 4. 72-pin QFN Pin Diagram (Top View)

## **Packaging**

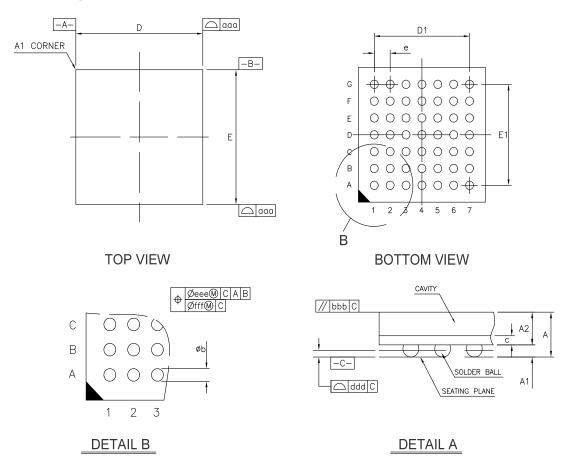

## **49-ball Package Dimensions**

Figure 5. 49-ball VFBGA Package Diagram (SiI902nAYBT)

JEDEC Package Code MO-225

| Item | Description                             | Min      | Тур   | Max   |

|------|-----------------------------------------|----------|-------|-------|

| A    | Thickness                               | _        | _     | 0.80  |

| A1   | Stand-off                               | 0.13     | 0.18  | 0.23  |

| A2   | Substrate thickness +<br>Mold thickness | 0.446    | 0.486 | 0.526 |

| D    | Body size                               | 3.90     | 4.00  | 4.10  |

| Е    | Body size                               | 3.90     | 4.00  | 4.10  |

| D1   | Footprint                               | _        | 3.00  | _     |

| E1   | Footprint                               | _        | 3.00  | _     |

| b    | Ball width                              | 0.20     | 0.25  | 0.30  |

| e    | Ball pitch                              | — 0.50 — |       | _     |

| aaa  | Package edge tolerance                  |          | 0.10  |       |

| bbb  | Mold flatness                           | 0.10     |       |       |

| ddd  | Coplanarity                             | 0.08     |       |       |

| eee  | Ball offset (package)                   |          | 0.15  |       |

| fff  | Ball offset (ball)                      |          | 0.05  |       |

All dimensions are in millimeters.

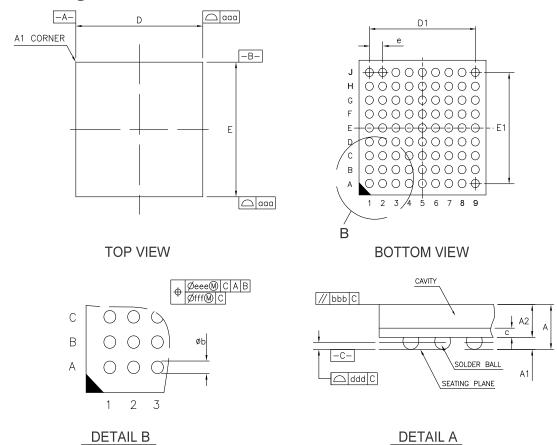

## 81-ball Package Dimensions

Figure 6. 81-ball VFBGA Package Diagram (SiI902nARBT)

JEDEC Package Code MO-225

| Item | Description                             | Min   | Typ   | Max   |

|------|-----------------------------------------|-------|-------|-------|

| A    | Thickness                               | _     |       | 0.80  |

| A1   | Stand-off                               | 0.13  | 0.18  | 0.23  |

| A2   | Substrate thickness +<br>Mold thickness | 0.446 | 0.486 | 0.526 |

| D    | Body size                               | 3.90  | 4.00  | 4.10  |

| E    | Body size                               | 3.90  | 4.00  | 4.10  |

| D1   | Footprint                               | _     | 3.20  | _     |

| E1   | Footprint                               | _     | 3.20  | _     |

| b    | Ball width                              | 0.20  | 0.25  | 0.30  |

| e    | Ball pitch                              | _     | 0.40  | _     |

| aaa  | Package edge tolerance                  |       | 0.10  |       |

| bbb  | Mold flatness                           | 0.10  |       |       |

| ddd  | Coplanarity                             | 0.08  |       |       |

| eee  | Ball offset (package)                   | 0.15  |       |       |

| fff  | Ball offset (ball)                      |       | 0.05  |       |

All dimensions are in millimeters.

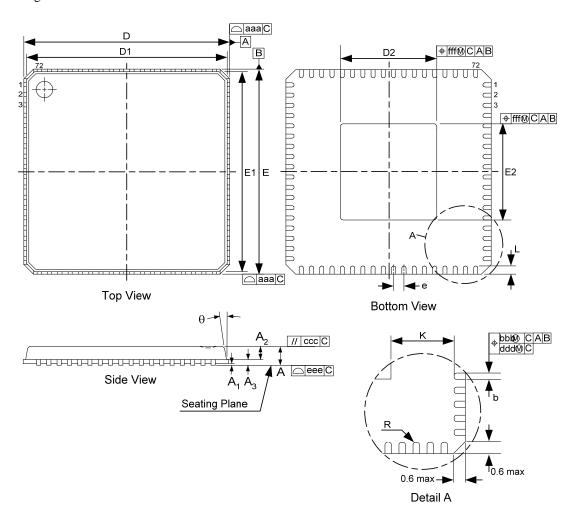

## 72-pin Package Dimensions

These drawings are not to scale.

Figure 7. 72-pin QFN Package Diagram (SiI902nACNU) JEDEC Package Code MO-220

| Item  | Description       | Min       | Тур  | Max  |  |

|-------|-------------------|-----------|------|------|--|

| A     | Thickness         | 0.80      | 0.85 | 0.90 |  |

| $A_1$ | Stand-off         | 0.00      | 0.02 | 0.05 |  |

| $A_2$ | Body thickness    | 0.60      | 0.65 | 0.70 |  |

| A3    |                   | 0.20 REF  |      |      |  |

| D     | Footprint         | 10.00 BSC |      |      |  |

| Е     | Footprint         | 10.00 BSC |      |      |  |

| $D_1$ | Body size         | 9.75 BSC  |      |      |  |

| $E_1$ | Body size         | 9.75 BSC  |      |      |  |

| D2    | ePad size         | 4.55      | 4.70 | 4.85 |  |

| E2    | ePad size         | 4.55      | 4.70 | 4.85 |  |

| b     | Plated lead width | 0.18      | 0.23 | 0.28 |  |

| Item | Description            | Min  | Тур      | Max  |

|------|------------------------|------|----------|------|

| e    | Lead pitch             |      | 0.50 BSC |      |

| K    | ePad-to-pin clearance  | 0.20 |          |      |

| L    | Lead foot length       | 0.30 | 0.40     | 0.50 |

| R    | Lead radius            | 0.09 |          |      |

| θ    | Lead foot angle        | 0°   | _        | 14°  |

| aaa  | Package edge tolerance | _    | _        | 0.15 |

| bbb  |                        |      |          | 0.10 |

| ccc  |                        |      |          | 0.10 |

| ddd  |                        |      |          | 0.05 |

| eee  |                        | _    | _        | 0.08 |

| fff  | ePad edge tolerance    |      |          | 0.10 |

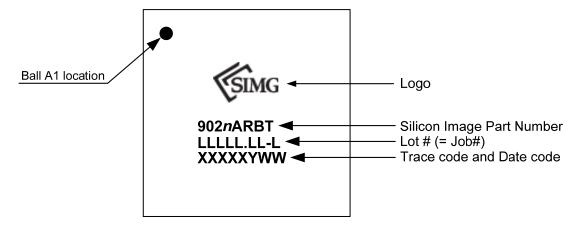

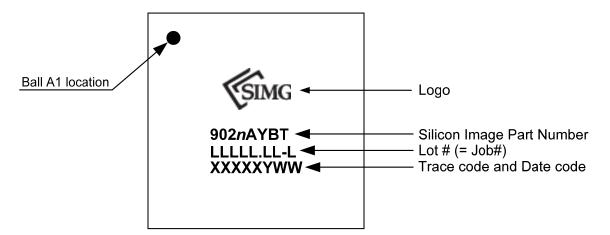

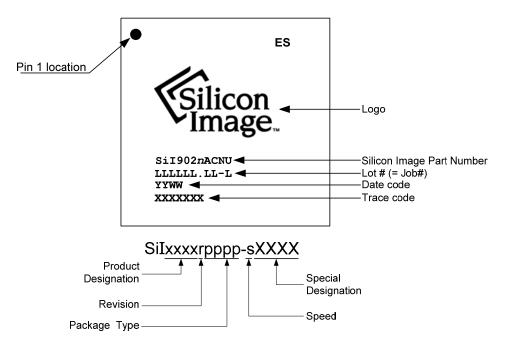

### **Marking Specification**

Marking drawings are not to scale.

Figure 8. Marking Diagram (SiI902nARBT)

Figure 9. Marking Diagram (SiI902nAYBT)

Figure 10. Marking Diagram (SiI902nACNU)

## **Ordering Information**

| Part Numbers | Package Type           | Pixel Clock Range | Security | Temperature Grade        |

|--------------|------------------------|-------------------|----------|--------------------------|

| SiI9022ARBT  | 81-ball 4 x 4 mm VFBGA | 25–165 MHz        | _        | Extended (-20 to +85 °C) |

| SiI9022AYBT  | 49-ball 4 x 4 mm VFBGA | 25–165 MHz        | _        | Extended (-20 to +85 °C) |

| SiI9022ACNU  | 72-pin 10 x 10 mm QFN  | 25–165 MHz        | _        | Extended (-20 to +85 °C) |

| SiI9024ARBT  | 81-ball 4 x 4 mm VFBGA | 25–165 MHz        | HDCP     | Extended (-20 to +85 °C) |

| SiI9024AYBT  | 49-ball 4 x 4 mm VFBGA | 25–165 MHz        | HDCP     | Extended (-20 to +85 °C) |

| SiI9024ACNU  | 72-pin 10 x 10 mm QFN  | 25–165 MHz        | HDCP     | Extended (-20 to +85 °C) |

The universal package can be used in both lead-free and ordinary process lines.

#### **Disclaimers**

These materials are provided on an "AS IS" basis. Silicon Image, Inc. and its affiliates disclaim all representations and warranties (express, implied, statutory or otherwise), including but not limited to: (i) all implied warranties of merchantability, fitness for a particular purpose, and/or non-infringement of third party rights; (ii) all warranties arising out of course-of-dealing, usage, and/or trade; and (iii) all warranties that the information or results provided in, or that may be obtained from use of, the materials are accurate, reliable, complete, up-to-date, or produce specific outcomes. Silicon Image, Inc. and its affiliates assume no liability or responsibility for any errors or omissions in these materials, makes no commitment or warranty to correct any such errors or omissions or update or keep current the information contained in these materials, and expressly disclaims all direct, indirect, special, incidental, consequential, reliance and punitive damages, including WITHOUT LIMITATION any loss of profits arising out of your access to, use or interpretation of, or actions taken or not taken based on the content of these materials.

Silicon Image, Inc. and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, delete, and/or change any of this information.

Notwithstanding the foregoing, these materials shall not, in the absence of authorization under U.S. and local law and regulations, as required, be used by or exported or re-exported to (i) any U.S. sanctioned or embargoed country, or to nationals or residents of such countries; or (ii) any person, entity, organization or other party identified on the U.S. Department of Commerce's Denied Persons or Entity List, the U.S. Department of Treasury's Specially Designated Nationals or Blocked Persons List, or the Department of State's Debarred Parties List, as published and revised from time to time; (iii) any party engaged in nuclear, chemical/biological weapons or missile proliferation activities; or (iv) any party for use in the design, development, or production of rocket systems or unmanned air vehicles.

#### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by Silicon Image, Inc. and/or its affiliates are provided on as "AS IS" basis, except to the extent that Silicon Image, Inc. and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied). EXCEPT FOR SUCH LIMITED WARRANTY, SILICON IMAGE, INC. AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY SILICON IMAGE, INC. AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR USE OR RESALE IN SYSTEMS WHERE THE FAILURE. MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, USE IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW, DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

1060 E. Arques Avenue Sunnyvale, CA 94085 T 408.616.4000 F 408.830.9530 www.siliconimage.com