### **Features**

100-pin plastic quad flat pack (QFP), surfacemount package IEEE 488.1-compatible transceivers on chip

- Fast data transfer

- Up to 1.5 Mbytes/s using interlocked IEEE 488.1 handshake

- Up to 8 Mbytes/s using HS488<sup>™</sup>

Two 8-bit 16-deep FIFOs buffer data between GPIB and CPU

- Vith exception of Controller, performs all IEEE 488 interface functions SH1, AH1, T5 or TE5, L3 or LE3, SR1, R1, PP1 or PP2, DC1, DT1, and C0

- Meets all IEEE 488.2 requirements

- Bus line monitoring

Preferred implementation of

- requesting service Not sending messages when there are no Listeners

- Software compatible with Turbo488<sup>™</sup>/NAT4882<sup>™</sup> ASICs Reduces software overhead

- Does not lose a data byte if ATN is

- asserted while transmitting data Static interrupts status bits that do

- not clear when read

- Automatically transmits END or performs RFD holdoff on last byte of DMA transfer

- Interrupts when handshake is complete on last byte of a DMA

- transfer Has 32-bit counter for large

- uninterrupted data transfers Programmable timer interrupt for general-purpose timing us Complete in-system functional testing with internal loop-back mode

- ISA bus glue logic on chip

- IsA bus glue logic on chip Direct memory access (DMA) Device status indicator pins My Addresse, Talk Addressed, Listen Addressed, REM, DCAS, TRIG Automatically processes IEEE 488 commands and reads undefined commands commands

- Handles 6 primary and secondary addressing modes Automatic EOS and/or NL message

- detection Programmable data transfer rate -

- TTL-compatible CMOS device

## Description

The TNT4882 provides a single-chip IEEE 488.2 Talker/Listener interface to the general-purpose interface bus (GPIB). The TNT4882 combines the circuitry of the NAT4882 IEEE 488.2 application-specific integrated circuit (ASIC), Turbo488 performance-enhancing ASIC, and GPIB transceivers to create a single-chip IEEE 488.2 interface. Because the TNT4882 contains the NAT4882 register set, which in turn has the NEC  $\mu$ PD7210 and TI TMS 9914A register sets, developers using any of these chips can easily port existing code directly to the TNT4882, thereby significantly reducing software development time. Also, with just a few modifications, you can implement all the improved features of the IEEE 488.2 standard. The TNT4882 is ideal for use in all IEEE 488 instrument designs because of its small size, surface-mount ability, and performance enhancements that include HS488, a new high-speed mode for GPIB transfers.

## HS488 Overview

The HS488 high-speed mode for GPIB transfers increases the maximum data transfer rate of devices on a GPIB network up to 8 Mbytes/s. The TNT4882 completely and transparently handles the HS488 protocol without additional circuitry, a method that is a superset of the IEEE 488 standard. Thus, you can mix existing GPIB devices with HS488 devices without changing your application programs. The TNT4882 can implement high-speed data transfers automatically. Maximum data transfer rates obtainable using HS488 depend on the host architecture and system configuration.

## Architecture, Modes

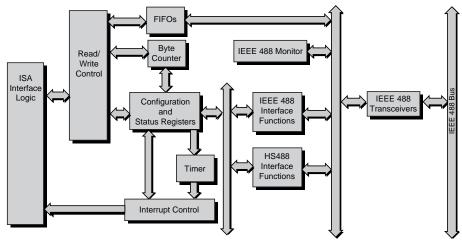

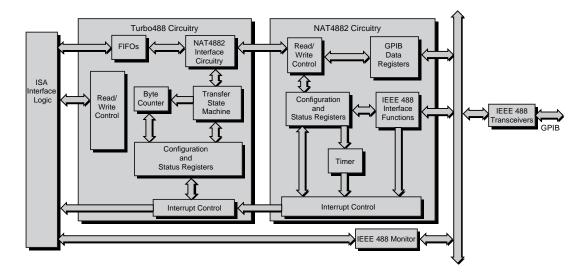

The TNT4882 integrates the circuitry of the Turbo488, NAT4882, and IEEE 488.1- compatible transceivers. The TNT4882 circuitry logically interconnects these three components in one of two ways - "one-chip mode" (see Figure 1) or "two-chip mode" (see Figure 2)

The TNT4882 powers up in two-chip mode, which exactly duplicates the Turbo488/NAT4882 chipset for software compatibility. During I/O accesses in two-chip mode, the CPU accesses the Turbo488 and passes all accesses within a certain address range to the NAT4882. The Turbo488 also manages transfers between its internal first-in first-out buffers (FIFOs) and the NAT4882, arbitrating between these data transfers and any I/O accesses of the NAT4882 by the CPU. Accesses to the NAT4882 registers take longer than Turbo488 accesses because all accesses to the NAT4882 registers must go through the Turbo488 and its arbiter.

To achieve higher data transfer rates, you can switch the TNT4882 to one-chip mode in software. In one-chip mode, the first-in first-out (FIFO) buffer connects directly to the GPIB transceivers and the CPU accesses all registers directly. You can access NAT4882 registers in the same amount of time as Turbo488 registers because accesses to these registers do not go through the Turbo488.

The NAT4882 portion of the TNT4882 can emulate either the NEC µPD7210 or the TI TMS9914A GPIB controller chips. The state of one of the TNT4882 input pins determines the chip emulation mode on power up, but you can switch the chip emulation mode back and forth between 7210 and 9914 modes through software.

The register map of the NAT4882 portion of the TNT4882 changes to emulate either the 7210 or the 9914, but the Turbo488 registers are identical in both chip emulation modes. You cannot use one-chip mode with the 9914 emulation mode. Because the Turbo488 was designed to interface to the 7210 and not the 9914, the software can rearrange the register map of the 9914 mode NAT4882 registers so that the 9914 mode Command/Data Out Register and Data In Register and the Auxiliary Command Register appear at the same addresses as the corresponding 7210 mode registers. The Turbo488 can then perform DMA transfers with the NAT4882 in 9914 mode.

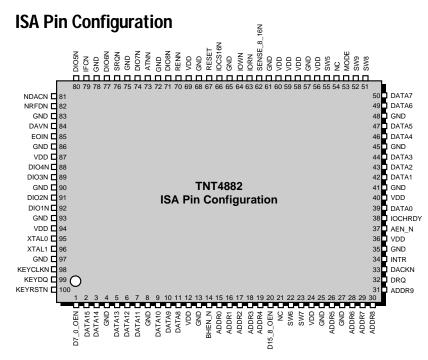

The TNT4882 has two different pin configurations – Generic (see Figure 3) and ISA (see Figure 4). The TNT4882 determines which configuration to use by the location of the power (VDD) and ground pins. The Generic pin configuration provides a simple interface to any CPU. Using the ISA pin configuration, you can connect the TNT4882 directly to an ISA (IBM PC AT) bus without any external glue logic or data transceivers. You can also use the ISA pin configuration TNT4882 with an 8-bit (PC/XT) bus. You may want to use the ISA version for interfaces other than an ISA bus to take advantage of the built-in 5-bit address decoder. You can use two-chip mode, one-chip mode, 7210 mode, and 9914 mode identically with either pin configuration.

## TNT4882 Block Diagrams

Figure 1. TNT4882 One-Chip Mode

Figure 2. TNT4882 Two-Chip Mode

#### **Generic Pin Configuration** RESETI BBUSN MRN RDN d ND GND GND MODE NC DCAS GND GND UDD GND GND CSN \_\_\_\_\_ 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 DATA7 49 DATA6 48 GND NRFDN **D** DAVN DATA5 DATA4 EOIN GND GND VDD DATA3 DIO4N DATA2 DIO3N DATA1 **TNT4882** GND GND **Generic Pin Configuration** VDD DIO2N DIO1N DATA0 GND GND GND GND GND GND VDD C XTALO C XTAL1 GND 🗖 INTR KEYCLKN DACKN KEYDQ 🗖 99 С KEYRSTN **D** 100 BURST RDN BBUS\_OEN I DATA14 BATA14 GND DATA13 DATA10 DATA10 DATA10 DATA10 DATA10 DATA10 DATA10 DATA10 DATA10

Figure 3. TNT4882 Generic Pin Configuration

## **Generic Pin Description**

All pins with names that end in 'N' are active low; all others are active high. All input (I) and bidirectional (I/O) pins have an internal pull-up resistor between 50 k $\Omega$  and 150 k $\Omega$ .

Note: You can also see the "Hardware Considerations" chapter of the "TNT Programmer Reference Manual" (P/N 320724-01) for more information.

| Pin No.(s)        | Name(s)   | Туре | Description                                                                                   |

|-------------------|-----------|------|-----------------------------------------------------------------------------------------------|

| 1                 | BBUS_OEN  | 0    | Asserts when DATA7-0 (B bus) is enabled for output                                            |

| 2,3,5,6,7,9,10,11 | DATA15-8  | I/O  | Upper 8 bits of bidirectional three-state data bus for transfer of commands, data, and status |

|                   |           |      | between TNT4882 and CPU – also known as the A bus                                             |

| 14                | ABUSN     | 1    | Enables register accesses through the A bus (DATA15-8) – DATA15 is the most significant bit   |

| 19-15             | ADDR4-0   | 1    | Determines which register to access during a read or write operation                          |

| 20                | ABUS_OEN  | 0    | Asserts when DATA15-8 (A bus) is enabled for output                                           |

| 21                | TADCS     | 0    | Asserts when the TNT4882 is an active or addressed IEEE 488 Talker (TADS, TACS, or SPAS)      |

| 22                | CPUACC    | 0    | Asserts in two-chip mode during a NAT4882 register I/O access                                 |

| 23                | TRIG      | 0    | Asserts when in DTAS or when the auxiliary trigger software command is issued                 |

| 26                | PAGED     | 1    | Asserting this pin pages in the page-in registers in the 7210 mode                            |

| 28                | REM       | 0    | Asserts when the TNT4882 is in a remote state (REMS or RWLS)                                  |

| 29                | SWAPN     | 1    | Rearranges the order of the registers when asserted and in 9914 mode                          |

| 30                | FIFO_RDY  | 0    | Asserts when the FIFO is ready for burst access                                               |

| 31                | BURST_RDN | 1    | When asserted, places the TNT4882 in a burst read mode, in which the first word in the        |

|                   |           |      | FIFO is always driven on the TNT4882 data bus – words are removed from the FIFOs at           |

|                   |           |      | each rising edge of RDN – see reference manual for details                                    |

| 32                | DRQ       | 0    | Asserts to request a DMA transfer cycle                                                       |

| 33                | DACKN     | 1    | Enables FIFO accesses during a DMA transfer cycle                                             |

| 34                | INTR      | 0    | Asserts when one or more of the unmasked interrupt conditions becomes true                    |

| 38                | RDY1      | 0    | Asserts during an I/O access to indicate that the read data is available or that the write    |

|                   |           |      | data has been latched – asserts immediately on an access to Turbo488 registers or in          |

|                   |           |      | one-chip mode                                                                                 |

| 50,49,47,46,      | DATA7-0   | I/O  | Lower eight bits of bidirectional three-state data bus for transfer of commands, data, and    |

| 44,43,42,39       |           |      | status between TNT4882 and CPU – also known as the B bus – DATA7 is the most significant bit  |

Table continued on page 4

Table continued from page 3

| Pin No.(s)         | Name(s)             | Туре | Description                                                                           |

|--------------------|---------------------|------|---------------------------------------------------------------------------------------|

| 51                 | DCAS                | 0    | Asserts when the device clear state machine is in DCAS                                |

| 52                 | NC                  | 0    | Leave this pin unconnected                                                            |

| 53                 | MODE                | I    | Determines whether the TNT4882 powers up in 7210 or 9914 emulation mode –             |

|                    |                     |      | High = 7210 mode, Low = 9914 mode                                                     |

| 55                 | CSN                 | I    | Chip Select enables I/O transfers between the CPU and the TNT4882                     |

| 62                 | BBUSN               | I    | Enables register accesses through the B bus (DATA7-0)                                 |

| 63                 | RDN                 | I    | Enables the contents of the registers selected by ADDR 4:0 and CSN or the FIFOs to    |

|                    |                     |      | appear on the data bus selected by ABUSN and BBUSN                                    |

| 64                 | WRN                 | I    | Latches data on the bus selected by ABUSN and BBUSN into an internal TNT4882 register |

|                    |                     |      | on the trailing (rising) edge of WRN                                                  |

| 66                 | LADCS               | 0    | Asserts when the TNT4882 is addressed as a Listener                                   |

| 67                 | RESETN              | I    | Holds the TNT4882 in its idle state                                                   |

| 71,74,77,80,88,    | DIO8-1N             | I/O  | 8-bit bidirectional IEEE 488 data bus                                                 |

| 89,91,92           |                     |      |                                                                                       |

| 70,73,76,79,       | RENN, ATNN, SRQN,   | I/O  | IEEE 488 control signals                                                              |

| 81,82,84,85        | IFCN, NDACN, NRFDN, |      |                                                                                       |

|                    | DAVN, EOIN          |      |                                                                                       |

| 95                 | XTALO               | 0    | Output of crystal circuit – use only for driving a quartz crystal                     |

| 96                 | XTAL1               | I    | Crystal oscillator input – drive with a 40 MHz CMOS input level clock signal          |

| 98                 | KEYCLKN             | 0    | Strobes data to or from a DS1204 electronic key                                       |

| 99                 | KEYDQ               | I/O  | Transmits serial data between the TNT4882 and a DS1204 key                            |

| 100                | KEYRSTN             | 0    | Resets a DS1204 key                                                                   |

| 4,8,13,25,27,35,37 | GND                 | _    | Ground pins – 0 V                                                                     |

| 41,45,48,54,56,57, |                     |      |                                                                                       |

| 59,61,65,68,72,75, |                     |      |                                                                                       |

| 78,83,86,90,93,97  |                     |      |                                                                                       |

| 12,24,36,40,58,    | VDD                 | _    | Power pins – +5 V (±5%)                                                               |

| 60,69,87,94        |                     |      |                                                                                       |

Figure 4. TNT4882 ISA Pin Configuration

### **ISA Pin Description**

All input (I) and bidirectional (I/O) pins have an internal pull-up resistor between 50 k $\Omega$  and 150 k $\Omega$ . Pins with names that end in "N" are active low signals – all others are active high. Open-collector outputs are type "OC." Note: You can also see the "Hardware Considerations" chapter of the "TNT Programmer Reference Manual" (P/N 320724-01) for more information.

| Pin No.(s)                                                           | Name(s)                                                | Туре | Description                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------|--------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                    | D7_0_0EN                                               | 0    | Asserts when DATA7-0 bus is enabled for output – may be left unconnected                                                                                                                                                                                                                                                        |

| 2,3,5,6,7,9,10,11                                                    | DATA15-8                                               | 1/0  | Upper eight bits of bidirectional three-state data bus for transfer of commands,<br>data, and status between TNT4882 and CPU – can connect directly to the AT bus –<br>DATA15 is the most significant bit                                                                                                                       |

| 14                                                                   | BHEN N                                                 | 1    | Enables access to upper eight bits of data bus when asserted                                                                                                                                                                                                                                                                    |

| 19-15                                                                | ADDR4-0                                                |      | Determines which register will be accessed during an I/O access                                                                                                                                                                                                                                                                 |

| 31,30,29,28,26                                                       | ADDR9-5                                                | 1    | Determines if an I/O address is within the range occupied by the TNT4882 –<br>the chip is selected and an I/O access occurs when ADDR9-5 match SW9-5 and<br>AEN_N is asserted                                                                                                                                                   |

| 20                                                                   | D15_8_OEN                                              | 0    | Asserts when DATA15:8 bus is enabled for output - may be left unconnected                                                                                                                                                                                                                                                       |

| 21,54                                                                | NC                                                     | 0    | Leave unconnected                                                                                                                                                                                                                                                                                                               |

| 52,51,23,22,55                                                       | SW9-5                                                  | 1    | Determines the base address of the TNT4882                                                                                                                                                                                                                                                                                      |

| 32                                                                   | DRQ                                                    | 0    | Asserts to request a DMA transfer cycle                                                                                                                                                                                                                                                                                         |

| 33                                                                   | DACKN                                                  | I    | Enables FIFO accesses during a DMA transfer cycle                                                                                                                                                                                                                                                                               |

| 34                                                                   | INTR                                                   | 0    | Asserts when one or more of the unmasked interrupt conditions becomes true                                                                                                                                                                                                                                                      |

| 37                                                                   | AEN_N                                                  | I    | Enables I/O accesses to the TNT4882                                                                                                                                                                                                                                                                                             |

| 38                                                                   | IOCHRDY                                                | OC   | When the TNT4882 is not accessed, this open-collector signal is not driven, and a pull-up resistor on the system board keeps it pulled high – at the start of some TNT4882 accesses, the TNT4882 may drive it low, then pull it high again during the cycle to indicate that the TNT4882 is ready for the CPU to end that cycle |

| 50,49,47,46,44,<br>43,42,39                                          | DATA7-0                                                | 1/0  | Lower eight bits of bidirectional three-state data bus for transfer of commands, data,<br>and status between TNT4882 and CPU – can connect directly to the AT bus – DATA7<br>is the most significant bit                                                                                                                        |

| 53                                                                   | MODE                                                   | I    | Forces the TNT4882 to 7210 (high) or 9914 (low) emulation mode on a hardware reset – may be left unconnected                                                                                                                                                                                                                    |

| 62                                                                   | SENSE_8_16N                                            | I    | Pull this pin low to tell the TNT4882 that it is connected to a 16-bit bus – leave it unconnected if the TNT4882 is connected to an 8-bit bus                                                                                                                                                                                   |

| 63                                                                   | IORN                                                   | I    | Drives the contents of the register selected by ADDR4-0 on the data bus when the TNT4882 is selected                                                                                                                                                                                                                            |

| 64                                                                   | IOWN                                                   | I    | The value on the data bus is latched into the register selected by ADDR4-0 on the<br>rising edge of IOWN when you select the TNT4882                                                                                                                                                                                            |

| 66                                                                   | IOCS16N                                                | OC   | Driven low during an access to the upper data bus                                                                                                                                                                                                                                                                               |

| 67                                                                   | RESET                                                  | 1    | Causes a hardware reset and holds the TNT4882 in its idle state while asserted                                                                                                                                                                                                                                                  |

| 71,74,77,80,88,<br>89,91,92                                          | DIO8-1N                                                | 1/0  | 8-bit bidirectional IEEE 488 data bus                                                                                                                                                                                                                                                                                           |

| 70,73,76,79,81,<br>82,84,85                                          | renn, atnn, srqn,<br>IFCN, ndacn, nrfdn,<br>Davn, eoin | 1/0  | IEEE 488 control signals                                                                                                                                                                                                                                                                                                        |

| 95                                                                   | XTALO                                                  | 0    | Output of crystal circuit – use only for driving a quartz crystal                                                                                                                                                                                                                                                               |

| 96                                                                   | XTAL1                                                  | 1    | Crystal oscillator input – drive with a 40 MHz CMOS input level clock signal                                                                                                                                                                                                                                                    |

| 98                                                                   | KEYCLKN                                                | 0    | Strobes data to or from the DS1204 electronic key                                                                                                                                                                                                                                                                               |

| 99                                                                   | KEYDQ                                                  | 1/0  | Transmits serial data between the TNT4882 and a DS1204 key                                                                                                                                                                                                                                                                      |

| 100                                                                  | KEYRSTN                                                | 0    | Resets a DS1204 key                                                                                                                                                                                                                                                                                                             |

| 4,8,13,25,27,35,41,<br>45,48,57,61,65,68,72,<br>75,78,83,86,90,93,97 | GND                                                    | -    | Ground pins – 0 V                                                                                                                                                                                                                                                                                                               |

| 12,24,36,40,56,58,<br>59,60,69,87,94                                 | VDD                                                    | -    | Power pins – +5 V (±5%)                                                                                                                                                                                                                                                                                                         |

### **TNT4882 Register Map**

|         |            |               |                | NAT4882 Re         | egisters           |                |                |  |  |

|---------|------------|---------------|----------------|--------------------|--------------------|----------------|----------------|--|--|

|         |            | 7210 N        | lode           | 9914 N             |                    | 9914 Mode      | Swapped        |  |  |

| ADDR4-0 | Hex Offset | Read Register | Write Register | Read Register      | Write Register     | Read Register  | Write Register |  |  |

| 00000   | 0          | DIR           | CDOR           | ISRO               | IMRO               | DIR            | CDOR           |  |  |

| 00010   | 2          | ISR1          | IMR1           | ISR1               | IMR1               | CPTR           | PPR            |  |  |

| 00100   | 4          | ISR2          | IMR2           | ADSR               | IMR2               | SPSR           | SPMR           |  |  |

| н       | и          |               |                |                    | EOSR               |                |                |  |  |

| н       | и          |               |                |                    | BCR                |                |                |  |  |

| и       | и          |               |                |                    | ACCR               |                |                |  |  |

| 00110   | 6          | SPSR          | SPMR           | BSR                | AUXCR              | ISR2           | ADR            |  |  |

| 01000   | 8          | ADSR          | ADMR           | ISR2               | ADR                | ADSR           | IMR2           |  |  |

| ш       | п          |               |                |                    |                    |                | EOSR           |  |  |

| н       | и          |               |                |                    |                    |                | BCR            |  |  |

| ш       | и          |               |                |                    |                    |                | ACCR           |  |  |

| 01010   | A          | CPTR          | AUXMR          | SPSR               | SPMR               | BSR            | AUXCR          |  |  |

| 01100   | С          | ADRO          | ADR            | CPTR               | PPR                | ISRO           | IMRO           |  |  |

| 01110   | E          | ADR1          | EOSR           | DIR                | CDOR               | ISR1           | IMR1           |  |  |

| 10001   | 11         | DSR           | SH_CNT         | -                  | -                  | -              | -              |  |  |

| 10011   | 13         | -             | HIER           | -                  | -                  | -              | -              |  |  |

| 10101   | 15         | -             | MISC           | -                  | -                  | -              | -              |  |  |

| 10111   | 17         | CSR           | KEYREG         | -                  | -                  | -              | -              |  |  |

| 11011   | 1B         | SASR          | DCR            | -                  | -                  | -              | -              |  |  |

| 11101   | 1D         | ISRO          | IMRO           | -                  | -                  | -              | -              |  |  |

| 11111   | 1F         | BSR           | BCR            | -                  | -                  | -              | -              |  |  |

|         |            |               | Turb           | 0488 Registers (Sa | ame in All Modes)  |                |                |  |  |

| ADDR4-0 | Hex Offset |               | Read Register  | ŭ 、                |                    | Write Register |                |  |  |

| 01001   | 9          |               | CNT2           |                    | CNT2               |                |                |  |  |

| 01011   | В          |               | CNT3           |                    |                    | CNT3           |                |  |  |

| 01101   | D          |               | -              |                    | HSSEL              |                |                |  |  |

| 10000   | 10         |               | STS1           |                    |                    | CFG            |                |  |  |

| 10010   | 12         |               | IMR3           |                    |                    | IMR3           |                |  |  |

| 10100   | 14         |               | CNTO           |                    |                    | CNTO           |                |  |  |

| 10110   | 16         |               | CNT1           |                    |                    | CNT1           |                |  |  |

| 11000   | 18         |               | FIFOB          |                    |                    | FIFOB          |                |  |  |

| 11001   | 19         |               | FIFOA          |                    |                    | FIFOA          |                |  |  |

| 11010   | 1A         |               | ISR3           |                    |                    | CCR            |                |  |  |

| 11100   | 1C         |               | STS2           |                    |                    | CMDR           |                |  |  |

| 11110   | 1E         |               | TIMER          |                    | 1                  | TIMER          |                |  |  |

|         |            |               |                | rs Only Accessible | in ISA Pin Configu |                |                |  |  |

| ADDR4-0 | Hex Offset |               | Read Register  |                    | Write Register     |                |                |  |  |

| 00101   | 5          |               | -              |                    |                    | ACCWR          |                |  |  |

| 00111   | 7          |               | -              |                    |                    | INTR           |                |  |  |

### **Notes on Register Map**

1. For complete register descriptions, see the "TNT4882 Programmer Reference Manual" (320724-01)

2. Some of the 7210 mode registers, such as the ISR1, have the same names as some of the 9914 mode registers. The 7210 mode registers are NOT the same as their 9914 mode counterparts. Be sure to refer to the appropriate bit map for the chip emulation mode you are using when programming these registers.

3. The shaded registers are "paged-in registers." Paged-in registers only exist in 9914 mode. Writing to the address of the 9914 mode ADSR normally does not access any registers. Writing one of four page-in commands to the AUXCR changes all subsequent writes to that address to that of the corresponding paged-in register. The two readable paged-in registers, the 9914 mode SPSR and ISR2, are both paged in whenever any one of the four writable paged-in registers is paged in. When you write the clear page-in command to the AUXCR, all paged-in registers are paged out again and are no longer accessible.

4. There are several unused bytes in the address space of the TNT4882. These addresses are reserved for adding new features to the chip. You should not map any external hardware into these addresses or access them at any time, as this may cause compatibility problems with future versions of the TNT4882.

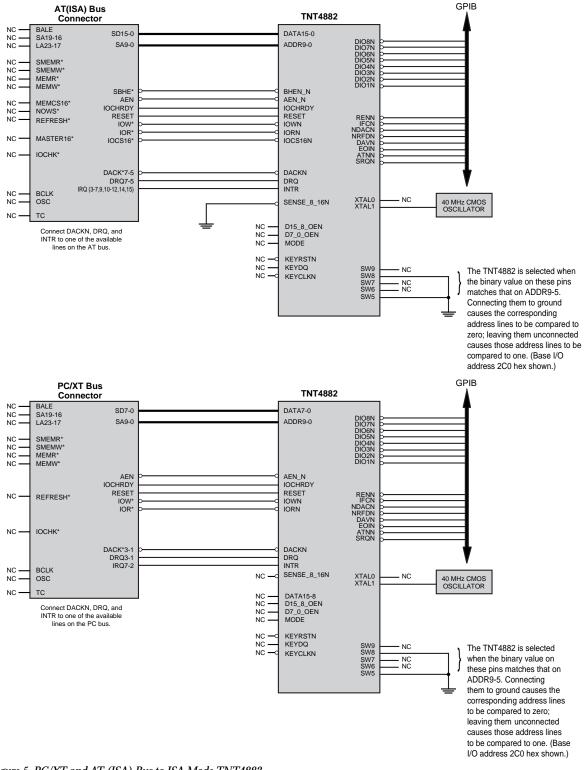

#### Hardware Interfacing – ISA Mode TNT4882

Figure 5. PC/XT and AT (ISA) Bus to ISA Mode TNT4882

## ISA Pin Configuration Byte Lane Table

This table shows which byte lane accesses the TNT4882 internal registers during an I/O access when you use the ISA pin configuration. All combinations of ADDR4-1, SENSE\_8\_16N, and BHEN\_N not shown in this table are illegal. You should not apply these combinations to the TNT4882 while the chip is selected. The accessed register is determined only by ADDR4-0, not SENSE\_8\_16N or BHEN\_N.

| SENSE_8_16N | BHEN_N | ADDR4-0 | IORN | IOWN | DATA15-8   | DATA7-0    |

|-------------|--------|---------|------|------|------------|------------|

| 0           | 0      | 11000   | 0    | 1    | FIFOA      | FIFOB      |

| 0           | 0      | 11000   | 1    | 0    | FIFOA      | FIFOB      |

| 0           | 0      | XXXX1   | 0    | 1    | Read       | Not Driven |

| 0           | 0      | XXXX1   | 1    | 0    | Written    | Ignored    |

| 0           | 1      | XXXXO   | 0    | 1    | Not Driven | Read       |

| 0           | 1      | XXXXO   | 1    | 0    | Ignored    | Written    |

| 1           | 1      | XXXXO   | 0    | 1    | Not Driven | Read       |

| 1           | 1      | XXXXO   | 1    | 0    | Ignored    | Written    |

| 1           | 1      | XXXX1   | 0    | 1    | Not Driven | Read       |

| 1           | 1      | XXXX1   | 1    | 0    | Ignored    | Written    |

#### GPIB **TNT4882-AQ** CPU (80186) (GENERIC) DRQ0 DRQ DIO8N DIO7N DIO6N DIO5N DIO4N DIO3N RDY1 ARDY RD RRN WR WRN INT0 INTR DIO2N DIO1N RESET RESETN ABUSN BHE RENN IFCN NDACN NRFDN DAVN EOIN ATNN SRQN AD0 BBUSN DACKN Decode AD15-0 CSN 74573 ALE ADDR4-0 74245 **DATA15-8** XTAL0 XTAL1 NC 40 MHz CMOS OSCILLATOR DEN DT/R KEYRSTN KEYDQ KEYCLKN NC DATA7-0 - NC 73245 NC NC CPUACC PAGED NC -SWAPN NC NC BURST\_RDN TADCS LADCS NC NC -FIFO\_RDY NC MODE NC NC NC REM TRIG DCAS ABUS\_OEN BBUS\_OEN NC NC

## Hardware Interfacing – Generic Mode TNT4882

Figure 6. Intel CPU to Generic Mode TNT4882

### **Generic Pin Configuration Byte Lane Table**

This table shows which byte lanes will access TNT4882 registers during I/O accesses.

| ABUSN | BBUSN | ADDR4-0 | D15-8  | D7-0   |

|-------|-------|---------|--------|--------|

| 0     | 1     | 11000   | FIFOB  | unused |

| 1     | 0     | 11000   | unused | FIFOB  |

| 0     | 0     | 11000   | FIFOA  | FIFOB  |

| 0     | 1     | XXXXX*  | used   | unused |

| 1     | 0     | XXXXX*  | unused | used   |

\*Any address except 11000

#### **Generic Mode DC Characteristics**

| Parameter                                                                        | Symbol          | Min  | Max             | Unit | Notes                         |

|----------------------------------------------------------------------------------|-----------------|------|-----------------|------|-------------------------------|

| Supply voltage                                                                   | V <sub>DD</sub> | 4.75 | 5.25            | V    |                               |

| Voltage input low                                                                | VIL             | -0.5 | 0.8             | V    |                               |

| Voltage input high                                                               | VIH             | 2.0  | V <sub>CC</sub> | V    |                               |

| Voltage output low                                                               | Vol             | 0.0  | 0.4             | V    |                               |

| Voltage output high                                                              | Voh             | 2.4  | V <sub>DD</sub> | V    |                               |

| Supply current                                                                   | I <sub>DD</sub> |      | 90              | mA   | 50 mA, typical                |

| Output current low<br>DATA15-0, LADCS, DRQ, INTR, RDY1                           | l <sub>oL</sub> |      | 24              | mA   | $V_{OL} = 0.4 V$              |

| Output current low<br>BBUS_OEN, ABUS_OEN, TADCS,<br>CPUACC, REM, TRIG, DCAS, CIC | I <sub>OL</sub> |      | 8               | mA   | $V_{OL} = 0.4 V$              |

| FIFO_RDY                                                                         | loL             |      | 4               | mA   | $V_{OL} = 0.4 V$              |

| Output current low<br>KEYDQ, KEYRSTN, KEYCLKN                                    | I <sub>OL</sub> |      | 2               | mA   | $V_{OL} = 0.4 V$              |

| DIO8-1N, IFCN, SRQN, EOIN, ATNN,<br>RENN, DAVN, NRFDN, NDACN                     | lol             |      | 48              | mA   | $V_{OL} = 0.4 V$              |

| Output current high                                                              | I <sub>OH</sub> |      | -12             | mA   | $V_{OH} = V_{DD} - 0.5 V$     |

| DATA15-0, LADCS, DRQ, INTR, RDY1                                                 |                 |      | -24             | mA   | $V_{OH} = 2.4 V$              |

| Output current high<br>BBUS_OEN, ABUS_OEN, TADCS,                                | Іон             |      | -4              | mA   | $V_{OH} = V_{DD} \cdot 0.5 V$ |

| CPUACC, REM, TRIG, DCAS                                                          |                 |      | -8              | mA   | $V_{OH} = 2.4 V$              |

| FIFO_RDY                                                                         | I <sub>ОН</sub> |      | -2              | mA   | $V_{OH} = V_{DD} \cdot 0.5 V$ |

|                                                                                  |                 |      | -4              |      | V <sub>OH</sub> = 2.4 V       |

| Output current high                                                              | I <sub>он</sub> |      | -1              | mA   | $V_{OH} = V_{DD} \cdot 0.5 V$ |

| KEYDQ, KEYRSTN, KEYCLKN                                                          |                 |      | -2              | mA   | $V_{OH} = 2.4 V$              |

| DIO8-1N, IFCN, SRQN, EOIN, ATNN,                                                 | I <sub>OH</sub> |      | 16              | mA   | $V_{OH} = 2.4 V$              |

| RENN, DAVN, NRFDN, NDACN                                                         |                 |      |                 |      |                               |

| Input leakage current – all pins                                                 | I <sub>H</sub>  |      | ±10             | μΑ   | $V_{DD} = 5.5 V$              |

| Output leakage current – all pins                                                | l <sub>oz</sub> |      | ±10             | μΑ   | $V_{DD} = 5.5 V$              |

#### **Generic Mode Capacitance**

| Parameter                                                 | Symbol | Min | Тур | Max | Unit | Notes |

|-----------------------------------------------------------|--------|-----|-----|-----|------|-------|

| Pin capacitance                                           | С      |     |     | 50  | рF   |       |

| DIO8-1N, RENN, ATNN, IFCN, SRQN, DAVN, EOIN, NDACN, NRFDN |        |     |     |     |      |       |

| Pin capacitance all other pins                            | С      |     | 3.6 |     | pF   |       |

#### **Generic Mode AC Characteristics**

|                                                          |                   | Comm | ercial | Indus | strial |               |

|----------------------------------------------------------|-------------------|------|--------|-------|--------|---------------|

| Parameter                                                | Symbol            | Min  | Max    | Min   | Max    | Unit          |

| Address setup to RDN = 0, WRN = 0                        | tas               | 24   |        | 27    |        | ns            |

| Data delay from RDN = 0, CSN = 0 (one-chip mode access)  | t <sub>RD</sub>   |      | 71     |       | 78     | ns            |

| Data float from RDN = 1                                  | t <sub>DF</sub>   |      | 40     |       | 44     | ns            |

| RDN pulsewidth (I/O access)                              | t <sub>RW</sub>   | 71   |        | 78    |        | ns            |

| RDN recovery width                                       | t <sub>RR</sub>   | 40   |        | 44    |        | ns            |

| Address hold from RDN = 1, WRN = 1                       | t <sub>AH</sub>   | 0    |        | 0     |        | ns            |

| DRQ unassertion                                          | tou               |      | 78     |       | 86     | ns            |

| Data delay from RDN = 0, DACKN = 0                       | t <sub>DR</sub>   |      | 40     |       | 44     | ns            |

| Data setup to WRN = 1                                    | tws               | 14   |        | 16    |        | ns            |

| Data hold from WRN = 1                                   | t <sub>WH</sub>   | 0    |        | 0     |        | ns            |

| CSN setup to RDN or WRN                                  | tcs               | 0    |        | 0     |        | ns            |

| CSN hold from RDN or WRN                                 | t <sub>cH</sub>   | 0    |        | 0     |        | ns            |

| DACKN setup to RDN or WRN                                | t <sub>DS</sub>   | 0    |        | 0     |        | ns            |

| DACKN hold from RDN or WRN                               | t <sub>DH</sub>   | 0    |        | 0     |        | ns            |

| RDN or WRN to CPUACC (two-chip mode NAT4882 access only) | t <sub>CPU</sub>  |      | 26     |       | 29     | ns            |

| RDN or WRN to RDY1 assert                                | t <sub>ARDY</sub> |      |        |       |        |               |

| Two-chip mode NAT4882 access                             |                   |      | 10     |       | 10     | clock periods |

| Other accesses                                           |                   |      | 25     |       | 28     | ns            |

| RDN or WRN to RDY1 unassert                              | t <sub>URDY</sub> |      | 22     |       | 25     | ns            |

| WRN pulse width (DMA access)                             | twp               | 40   |        | 44    |        | ns            |

| RDN pulse width (DMA access)                             | t <sub>RP</sub>   | 40   |        | 44    |        | ns            |

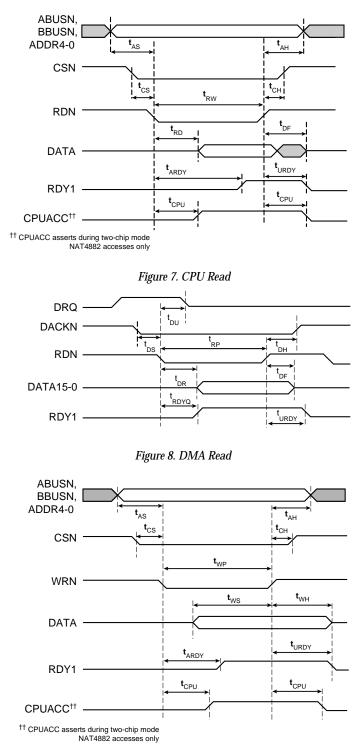

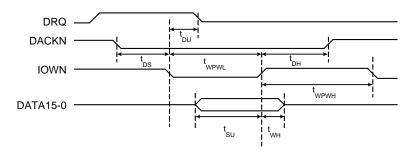

### **Generic Mode AC Characteristics Waveforms**

Figure 9. CPU Write

Waveforms continued on page 12

Waveforms continued from page 11

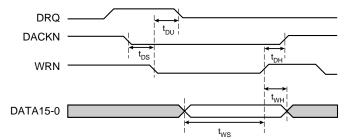

Figure 10. DMA Write

## **ISA Mode DC Characteristics**

| Parameter                                                                           | Symbol          | Min  | Max  | Unit | Notes                         |

|-------------------------------------------------------------------------------------|-----------------|------|------|------|-------------------------------|

| Supply voltage                                                                      | V <sub>DD</sub> | 4.75 | 5.25 | V    |                               |

| Voltage input low                                                                   | V <sub>IL</sub> | -0.5 | 0.8  | V    |                               |

| Voltage input high                                                                  | VIH             | 2.0  | Vcc  | V    |                               |

| Voltage output low                                                                  | Vol             | 0.0  | 0.4  | V    |                               |

| Voltage output high                                                                 | Vон             | 2.4  | VDD  | V    |                               |

| Supply current                                                                      | loo             |      | 90   | mA   | 50 mA, typical                |

| Output current low<br>DATA15-0<br>DRQ, INTR, IOCS16, IOCHRDY                        | l <sub>ol</sub> |      | 24   | mA   | $V_{OL} = 0.4 V$              |

| Output current low<br>D7_0_OEN                                                      | l <sub>ol</sub> |      | 16   | mA   | $V_{OL} = 0.4 V$              |

| Output current low<br>D15_8_OEN, TP_INTWTN                                          | I <sub>OL</sub> |      | 8    | mA   | $V_{OL} = 0.4 V$              |

| Output current low<br>KEYDQ, KEYRSTN, KEYCLKN                                       | la              |      | 2    | mA   | $V_{OL} = 0.4 V$              |

| Output current low<br>DIO8-1N, RENN, ATNN, IFCN, SRQN,<br>DAVN, EOIN, NDACN, NRFDN  | lol             |      | 48   | mA   | $V_{OL} = 0.4 V$              |

| Output current high<br>DATA15-0                                                     | I <sub>OH</sub> |      | -12  | mA   | $V_{OH} = V_{DD}$ -0.5 V      |

| DRQ, INTR                                                                           |                 |      | -24  | mA   | V <sub>OH</sub> = 2.4 V       |

| Output current high<br>D7_0_OEN                                                     | I <sub>OH</sub> |      | -8   | mA   | $V_{OH} = V_{DD}$ -0.5 V      |

|                                                                                     |                 |      | -16  | mA   | V <sub>OH</sub> = 2.4 V       |

| Output current high<br>D15_8_OEN,                                                   | Іон             |      | -4   | mA   | $V_{OH} = V_{DD} \cdot 0.5 V$ |

| TP_INTWTN                                                                           |                 |      | -8   | mA   | V <sub>OH</sub> = 2.4 V       |

| Output current high<br>KEYDQ, KEYRSTN,                                              | I <sub>OH</sub> |      | -1   | mA   | $V_{OH} = V_{DD} \cdot 0.5 V$ |

| KEYCLKN                                                                             |                 |      | -2   | mA   | V <sub>OH</sub> = 2.4 V       |

| Output current high<br>DIO8-1N, RENN, ATNN, IFCN, SRQN,<br>DAVN, EOIN, NDACN, NRFDN | I <sub>он</sub> |      | -16  | mA   | V <sub>OH</sub> = 2.4 V       |

| Input leakage current – all pins                                                    | I <sub>IH</sub> |      | ±10  | mA   | V <sub>DD</sub> = 5.5 V       |

| Output leakage current – all pins                                                   | loz             |      | ±10  | mA   | V <sub>DD</sub> = 5.5 V       |

## **ISA Mode Capacitance**

| Parameter                        | Symbol | Min | Тур | Max | Unit | Notes |

|----------------------------------|--------|-----|-----|-----|------|-------|

| Pin capacitance                  | С      |     | 3.6 |     | pF   |       |

| DATA15-0, DRQ, INTR, IOCS16N,    |        |     |     |     |      |       |

| IOCHRDY, ADDR6                   |        |     |     |     |      |       |

| Pin capacitance                  | С      |     | 3.0 |     | pF   |       |

| D7_0_OEN, D15_8_OEN, TP_INTWTN,  |        |     |     |     |      |       |

| KEYDQ, KEYRSTN, KEYCLKN, ADDR4,  |        |     |     |     |      |       |

| ADDR8, ADDR9                     |        |     |     |     |      |       |

| Pin capacitance                  | С      |     | 3.5 |     | pF   |       |

| BHEN_N, ADDR3-0, ADDR5, ADDR7,   |        |     |     |     |      |       |

| DACKN, AEN_N, MODE, TESTMODE,    |        |     |     |     |      |       |

| PWBSEL2-0, SW9, SENSE_8_16N,     |        |     |     |     |      |       |

| IORN, IOWN, RESET                |        |     |     |     |      |       |

| Pin capacitance                  | С      |     |     | 50  | pF   |       |

| DIO8-1N, RENN, ATNN, IFCN, SRQN, |        |     |     |     |      |       |

| DAVN, EOIN, NDACN, NRFDN         |        |     |     |     |      |       |

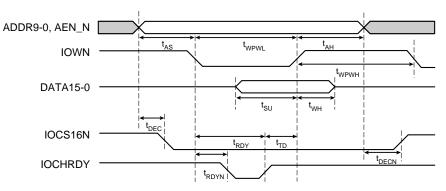

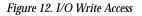

## **ISA Mode AC Characteristics**

| Parameter                               | Symbol            | Min | Max | Unit | Notes                     |

|-----------------------------------------|-------------------|-----|-----|------|---------------------------|

| ADDR9-0 setup to IORN, IOWN             | tas               | 30  |     | ns   |                           |

| ADDR9-0 hold from IORN, IOWN            | t <sub>AH</sub>   | 0   |     | ns   |                           |

| DACKN setup to IORN, IOWN               | t <sub>DS</sub>   | 0   |     | ns   |                           |

| DACKN hold from IORN, IOWN              | t <sub>DH</sub>   | 20  |     | ns   |                           |

| Data setup time to IOWN rising          | t <sub>su</sub>   | 22  |     | ns   |                           |

| Data hold time from IOWN rising         | t <sub>wн</sub>   | 0   |     | ns   |                           |

| IORN low pulse width                    | t <sub>RPWL</sub> | 100 |     | ns   |                           |

| IORN high pulse width                   | t <sub>RPWH</sub> | 42  |     | ns   |                           |

| IOWN low pulse width                    | t <sub>WPWL</sub> | 100 |     | ns   |                           |

| IOWN high pulse width                   | t <sub>WPWH</sub> | 100 |     | ns   |                           |

| IORN or IOWN held from IOCHRDY          | t <sub>TD</sub>   | 20  |     | ns   |                           |

| DRQ unassertion time                    | t <sub>DU</sub>   |     | 73  | ns   | Due to FIFO full/empty    |

| DRQ unassertion time                    | t <sub>DU</sub>   |     | 48  | ns   | Due to byte count reached |

| Data access time from IORN falling, DMA | t <sub>DACC</sub> |     | 80  | ns   |                           |

| Data access time from IORN falling, I/O | t <sub>ACC</sub>  |     | 80  | ns   |                           |

| Data hold time from IORN rising         | t <sub>RH</sub>   | 0   |     | ns   |                           |

| Data float time from IORN rising        | t <sub>DF</sub>   |     | 30  | ns   |                           |

| IOCS16N assertion after valid address   | t <sub>DEC</sub>  |     | 30  | ns   |                           |

| IOCS16N negation after invalid address  | t <sub>DECN</sub> |     | 20  | ns   |                           |

| IOCHRDY negation from IORN or IOWN      | t <sub>RDYN</sub> |     | 40  | ns   |                           |

| IOCHRDY release after IORN or IOWN      | t <sub>RDY</sub>  |     | 350 | ns   |                           |

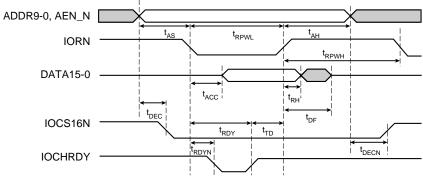

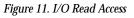

## ISA Mode AC Characteristics Waveforms

Waveforms continued on page 14

Waveforms continued from page 13

Figure 14. DMA Write Access

### **Absolute Maximum Ratings**

| Property                              | Range                          | Units |

|---------------------------------------|--------------------------------|-------|

| Supply voltage, VDD                   | - 0.5 to + 7.0                 | V     |

| Input voltage, V <sub>IN</sub>        | - 0.5 to V <sub>CC</sub> + 0.5 | V     |

| Output voltage, Vout                  | - 0.5 to V <sub>cc</sub> + 0.5 | V     |

| Storage temperature, T <sub>STG</sub> | - 55 to 150                    | °C    |

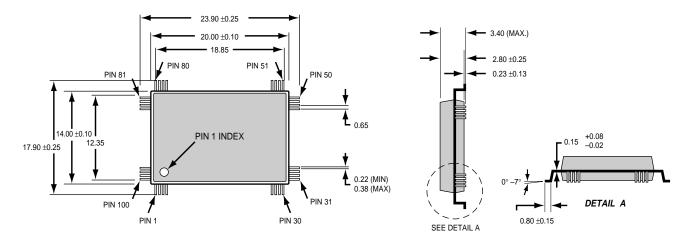

FRONT VIEW

SIDE VIEW

### NOTES:

- 1. All dimensions are shown in millimeters.

- 2. Unless otherwise specified, all dimensions are nominal.

- 3. When converting from millimeters to inches, four significant digits to the right of the decimal point are necessary.

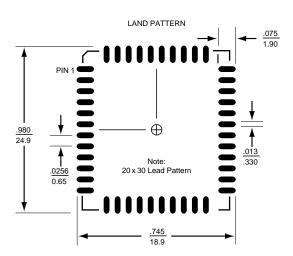

Figure 16. Mechanical Data

Figure 17. Recommended Land Pattern (not to scale)

## **Technical Support**

National Instruments strives to provide you with quality technical assistance worldwide. We currently offer electronic technical support along with our technical support centers staffed by Applications Engineers.

Access information from our Web site at **www.natinst.com** Our FTP site is dedicated to 24-hour support, with a collection of files and documents to answer your questions. Log on to our Internet host at ftp.natinst.com

You can fax questions to our Applications Engineers anytime at (800) 328-2203 or (512) 683-5678. Or, you can call from 8:00 a.m. to 6:00 p.m. (central time) at (512) 795-8248. Internationally, contact your local office. National Instruments sponsors a wide variety of group activities, such as user group meetings at trade shows and at large industrial sites. Our users also receive our quarterly *Instrumentation Newsletter*<sup>\*\*</sup> with the latest information on new products, product updates, application tips, and current events. In addition, sign up for *NI News*, our electronic news service at **www.natinst.com/news**

### Warranty

All National Instruments data acquisition, computer-based instrument, VXIbus, and MXIbus products are covered by a oneyear warranty. GPIB hardware products are covered by a two-year warranty from the date of shipment. The warranty covers board failures, components, cables, connectors, and switches, but does not cover faults caused by misuse. The owner may return a failed assembly to National Instruments for repair during the warranty period. Extended warranties are available at an additional charge.

Information furnished by National Instruments is believed to be accurate and reliable. National Instruments reserves the right to change product specifications without notice.

## Seminars/Training

Free and fee-paid seminars are presented several times a year in cities around the world. Comprehensive, fee-paid training courses are available at National Instruments offices or at customer sites. Call for training schedules.

### For More Information

Contact National Instruments for Application Notes such as: "Using the TNT4882 in a MC68340 System"

"Factors to Consider When Clocking the TNT4882 at Frequencies Less than 40 MHz"

"Porting a 9914 GPIB Design to Use the TNT4882"

## **Ordering Information**

TNT4882-BQ

TNT4882 Developer Kit......776866-01 Includes 2 TNT4882 ASICs, PC AT evaluation board, ESP-488TL

source code software, and documentation.

###

## Part Number Legend

| а  |    | b    | С | d | е |

|----|----|------|---|---|---|

| TN | IT | 4882 |   | В | Q |

- a. Family name TNT = Single-chip, high-speed, GPIB Talker/Listener interface

- b. Device-number 4882 = IEEE 488.2 compatible

- c. Reserved

- d. Revision

- e. Package type Q = Quad flat pack

## www.natinst.com (512) 794-0100

U.S. Corporate Headquarters Fax (512) 683-9300 • info@natinst.com

Branch Offices: Australia 03 9879 5166 • Austria 0662 45 79 90 0 • Belgium 02 757 00 20 • Brazil 000 811 781 0559 • Canada 905 785 0085 China 86 21 6555 7838 • Denmark 45 76 26 00 • Finland 09 725 725 11 • France 01 48 14 24 24 • Germany 089 741 31 30 • Hong Kong 2645 3186 India 91805275406 • Israel 03 6120092 • Italy 02 413091 • Japan 03 5472 2970 • Korea 02 596 7456 • Mexico 001 800 010 0793 Netherlands 0348 433466 • New Zealand 09 914 0488 • Norway 32 27 73 00 • Singapore 2265886 • Spain 91 640 0085 • Sweden 08 587 895 00 Switzerland 056 200 51 51 • Taiwan 02 2377 1200 • U.K. 01635 523545