## Intel<sup>®</sup> StrongARM<sup>\*</sup> SA-1110 Microprocessor

**Specification Update**

April 2001

**Notice:** The SA-1110 may contain design defects or errors known as errata. Characterized errata that may cause the SA-1110's behavior to deviate from published specifications are documented in this specification update.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1110 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Other brands and names are the property of their respective owners.

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 10 |

| Summary Table of Changes     | 12 |

| Identification Information   | 19 |

| Errata                       | 20 |

| Specification Changes        | 33 |

| Specification Clarifications | 35 |

| Documentation Changes        | 36 |

## **Revision History**

| Date | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

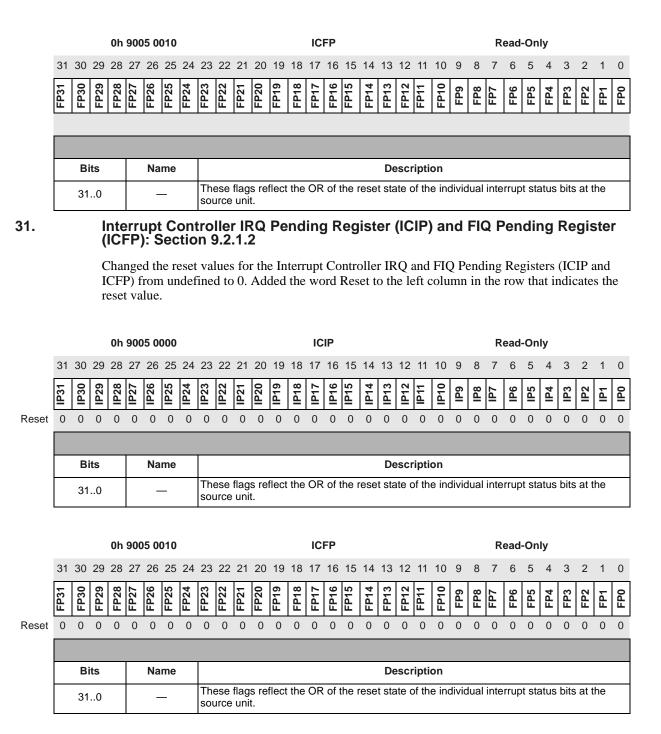

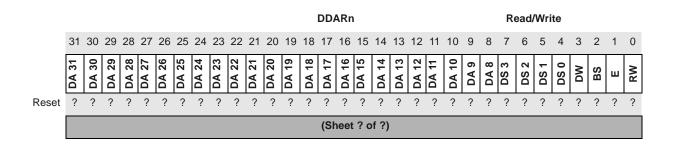

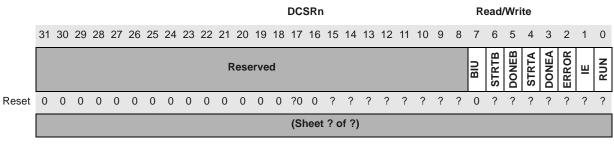

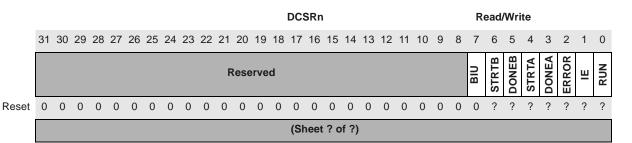

| Date | 022     | Description           Under Specification Change, modified item 5, "Power Supply Voltages and Currents: Section 12.3"<br>(page 33) to include the B5 stepping.           Under Documentation Changes, added item 11, "Memory Map: Section 2.4" (page 38), item 25,<br>"Data Aborts: Section 7.3" (page 41), item 26, "GPIO Pin Output Set Register (GPSR) and Pin<br>Output Clear Register (GPCR): Section 9.1.1.3" (page 41), item 29, "Interrupt Controller Pending<br>Register (ICPR): Section 9.2.1.1" (page 43), item 31, "Interrupt Controller IRQ Pending Register<br>(ICIP) and FIQ Pending Register (ICFP): Section 9.2.1.2" (page 44), item 33, "Real-Time Clock:<br>Section 9.3" (page 45), item 35, "RTC Alarm Register (RTAR): Section 9.3.2" (page 45), item 39,<br>"RTC Status Register (RTSR): Section 9.3.3" (page 46), item 42, "Transaction Summary: Section<br>10.1.5" (page 47), item 44, "MDCAS Registers with SDRAM and SMROM: Section 10.2.3.2" (page<br>47), item 45, "Static Memory Control Registers (MSC2 – 0): Section 10.2.4" (page 47), item 51,<br>"DMA Device Address Register (DDARn): Section 11.6.1.1" (page 49), item 54, "DMA Control/<br>Status Register (DCSRn): Section 11.6.1.2" (page 51), item 56, "DMA Buffer A Transfer Count<br>Register (DBTAn): Section 11.6.1.4" (page 51), item 58, "DMA Buffer A Transfer Count Register<br>(DBTBn): Section 11.6.1.6" (page 52), item 60, "Frame Buffer: Section 11.7.1.1.2" (page 56), item 75,<br>"Output FIFO Underrun Upper Panel Status (OUU) (read/write, maskable interrupt): Section<br>11.7.11.1" (page 56), item 73, "Base Address Update Flag: Section 11.7.1.1.2" (page 60), item<br>81, "USB Operation: Section 11.8.1" (page 61), item 82, "UDC Endpoint 2 Control/Status Register:<br>Section 11.8.9" (page 61), item 87, "4PPM Modulation: Section 11.0.2.1" (page 62), item 83, "CPU<br>and DMA Register Access Sizes: Secti90n 11.10.2.1" (page 62), item 39, "Transmit Enable<br>(TXE): Section 11.1.0.4.2" (page 63), item 94, "Receive Pin Polarity Select (RTP): Section<br>11.1.0.1.6" (page 64), 9 |

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | New Errata item 29, "USB Controller Endpoint 2 (IN) Transmits Incorrect Data" (page 32) has been added.<br>Modified the workaround for 27, "Incorrect Values Are Read from RTTR and RCNR Registers Immediately After They Are Written" (page 28).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |         | Under Specification Change, added item 4, "DC Operating Conditions: Section 12.2" (page 33), and item 5, "Power Supply Voltages and Currents: Section 12.3" (page 33).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

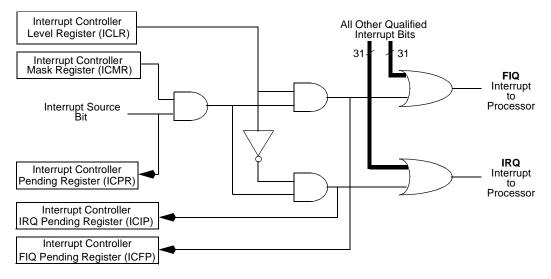

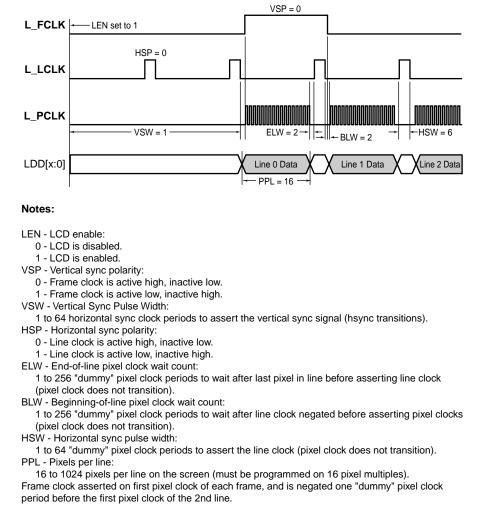

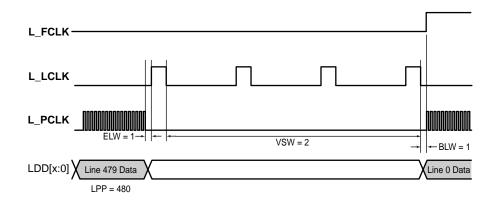

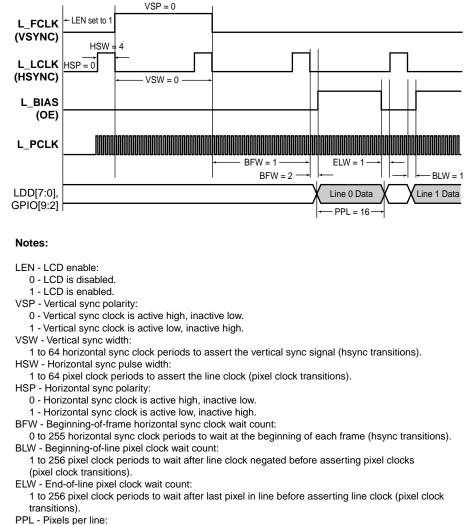

| 2/26/01  | 021     | Under Documentation Changes, added item 10, "Data Cache: Section 1.4.5" (page 38), item 12,<br>"Coprocessors: Section 3.3" (page 39), item 13, "Internal Coprocessor Instructions: Section 5.1" (page 39), item 14, "Register 7 – Cache Control Operations: Section 5.2.8" (page 39), item 15,<br>"Register 9 – Read-Buffer Operations: Section 5.2.10" (page 39), item 24, "Read Buffer: Section 6.4" (page 41), item 28, "Interrupt Controller: Section 9.2" (page 42), item 30, "Interrupt Controller FIQ Pending Register (ICCP): Section 9.2.1.2" (page 43), item 32, "Interrupt Controller Control Register (ICCR): Section 9.2.1.5" (page 44), item 34, "RTC Counter Register (RCNR): Section 9.3.1" (page 45), item 36, "RTC Status Register (RTSR): Section 9.3.3" (page 46), item 40, "RTC Trim Register (RTTR): Section 9.3.4" (page 46), item 47, "SDRAM Commands: Section 10.4.4" (page 48), item 59, "Frame Buffer: Section 11.7.1.2" (page 52), item 64, "Double-Pixel Data (DPD) Pin Mode: Section 11.7.3.9" (page 55), item 77, "LCD Controller Pin Timing Diagrams: Section 11.7.13" (page 57), item 78, "LCD Controller Pin Timing Diagrams: Section 11.7.13" (page 62), item 103, "SSP Transmit and Receive FIFOs: Section 11.9.3.1" (page 62), item 103, "SSP Transmit and Receive FIFOs: Section 11.1.2.7.3" (page 65), item 107, "PPC Pin State Register: Section 11.3.4" (page 67), item 110, "PPC Pin Flag Register: Section 11.1.3.7" (page 67), item 111, "DC Operating Conditions: Section 12.2" (page 67), item 112, "Power Supply Voltages and Currents: Section 12.3" (page 68), and item 115, "Package and Pinout: Section 14" (page 70)                                                                                                                                                                                                                                                                                                 |

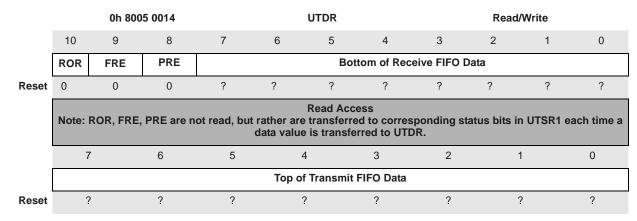

| 12/08/00 | 020     | New Errata item 28, "Incorrect Address Decode in USB Controller" (page 29) has been added.<br>Under Documentation Changes, added item 33, "Real-Time Clock: Section 9.3" (page 45), item 38,<br>"RTC Status Register (RTSR): Section 9.3.3" (page 46), item 43, "DRAM Refresh Control Register<br>(MDREFR): Section 10.2.2" (page 47), item 46, "SMROM Configuration Register (SMCNFG):<br>Section 10.3" (page 48), item 49, "DMA Device Address Register (DDARn): Section 11.6.1.1" (page<br>48), item 50, "DMA Device Address Register (DDARn): Section 11.6.1.1" (page 49), item 52, "DMA<br>Control/Status Register (DCSRn): Section 11.6.1.2" (page 50), item 53, "DMA Control/Status<br>Register (DCSRn): Section 11.6.1.2" (page 50), item 55, "DMA Control/Status<br>Register (DCSRn): Section 11.6.1.2" (page 50), item 55, "DMA Control/Status<br>Register (DDCSRn): Section 11.6.1.2" (page 50), item 55, "DMA Control/Status<br>Register (DDCSRn): Section 11.6.1.2" (page 50), item 55, "DMA Control/Status<br>Register (DDCSRn): Section 11.6.1.2" (page 50), item 55, "DMA Buffer A Transfer Count Register<br>(DBTAn): Section 11.6.1.4" (page 51), item 57, "DMA Buffer B Transfer Count Register (DBTBn):<br>Section 11.6.1.6" (page 52), item 66, "Palette DMA Request Delay (PDD): Section 11.7.3.10" (page<br>55), item 76, "LCD Controller Register Locations: Section 11.7.12" (page 57), item 83, "UDC<br>Endpoint Data Register: Section 11.8.10" (page 61), item 84, "UDC Data Register: Section 11.8.12"<br>(page 61), item 100, "UART Data Register: Section 11.11.6" (page 65), item 102, "SSP Transmit and<br>Receive FIFOs: Section 11.12.7.3" (page 65), item 104, "SSP Data Register: Section 11.12.11"<br>(page 66), item 105, "PPC Pin Direction Register: Section 11.13.3" (page 66), item 106, "PPC Pin<br>State Register: Section 11.13.4" (page 66), and item 108, "PPC Pin Assignment Register: Section<br>11.13.5.2" (page 67). |

| 10/20/00 | 019     | New Errata item 27, "Incorrect Values Are Read from RTTR and RCNR Registers Immediately After<br>They Are Written" (page 28) has been added.<br>New Specification Change item 3, "Modifications in SDRAM/SMROM Data Input Hold Time" (page<br>33) has been added.<br>Under Documentation Changes, added item 23, "Read Buffer: Section 6.4" (page 40), item 43,<br>"DRAM Refresh Control Register (MDREFR): Section 10.2.2" (page 47), item 46, "SMROM<br>Configuration Register (SMCNFG): Section 10.3" (page 48), item 59, "Frame Buffer: Section<br>11.7.1.2" (page 52), item 69, "Output Enable Polarity (OEP): Section 11.7.6.7" (page 56), item 74,<br>"Output FIFO Underrun Upper Panel Status (OUU) (read/write, maskable interrupt): Section<br>11.7.11.12" (page 57), item 76, "LCD Controller Register Locations: Section 11.7.12" (page 57), item<br>99, "Sample Clock GPIO: Section 11.11.3.5" (page 64), item 111, "DC Operating Conditions: Section<br>12.2" (page 67), item 113, "Timing Parameters: Section 13.6" (page 69), and item 118, "Boundary<br>Scan Interface Signals: Section 16.7" (page 71).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Date    | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |         | Under Errata item 21, "Failure of Synchronous Serial Port (SSP) Receiver Overrun Status Bit to<br>Generate Interrupt Request" (page 27) the workaround instructions have been modified. In Item<br>24, "Software Sleep Status Bit (PSSR:SSS) May Be Improperly Set After Sleep Wakeup" (page 28)<br>the "affected steppings" have been modified (affects all steppings). New items 25, "Improper<br>Operation of LCD Controller LCCR2 Register EFW (End of Frame Line Clock Wait Count)" (page<br>28) and 26, "Between Two Successive PCMCIA Accesses, Bus Arbiter Might Not Recognize<br>Pending, Highest-Priority, Bus Access Request From LCD Controller" (page 28) have been added.<br>Under Documentation Changes, removed documentation changes 1-6, 8-11, 13-20, 23-28, 30, 32,<br>34-36, 39-97 (having been incorporated into revision -003 of the developer's manual) respective to<br>Specification Update Revision 017.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |         | Under Documentation Changes, modified documentation change 21 (respective to revision 017) by removing the description for changing '9 bits' to '9 bytes' as this part of the modification was already implemented in revision -003 of the developer's manual. Modified documentation change 22 (respective to revision 017) by removing the description for changing bits 24 and 25 as this part of the modification is no longer required. The new descriptions of these changes are now documentation changes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9/12/00 | 018     | Under Documentation Changes, added item 16, "Register 14 – Debug Support (Breakpoints):<br>Section 5.2.13" (page 39) item 17, "Data Caches (Dcaches): Section 6.2" (page 39), item 18, "Writes<br>to a Bufferable and Noncacheable Location (B=1,C=0): Section 6.3.2.2" (page 40), item 20, "Writes to<br>a Non-Bufferable and Cacheable Location (B=0, C=1): Section 6.3.2.3" (page 40), item 20, "Writes to<br>a Non-Bufferable and Cacheable Location (B=0, C=1): Section 6.3.2.4" (page 40), item 21, "Read<br>Buffer (RB): Section 6.4" (page 40), item 22, "Read Buffer: Section 6.4" (page 40), item 41, "Sleep<br>Mode: Section 9.5.3" (page 46), item 48, "8-, 16-, and 32-Bit Data Bus Operation: Section 10.6.1"<br>(page 48), item 50, "DMA Device Address Register (DDARn): Section 11.6.1.1" (page 49), item 59,<br>"Frame Buffer: Section 11.7.1.2" (page 52), item 62, "Passive/Active Display Select (PAS): Section<br>11.7.3.7" (page 54), item 63, "Passive/Active Display Select (PAS): Section 11.7.3.7" (page 54), item<br>65, "Palette DMA Request Delay (PDD): Section 11.7.3.10" (page 55) item 67, "Beginning-of-Frame<br>Line Clock Wait Count (BFW): Section 11.7.5.4" (page 55), item 70, "DMA Channel 1 Current<br>Address Register: Section 11.7.9" (page 56), item 71, "Output FIFO Underrun Lower Panel Status<br>(OUL) (read only, maskable interrupt): Section 11.7.10" (page 56), item 74, "Output FIFO Underrun<br>Upper Panel Status (OUU) (read/write, maskable interrupt): Section 11.7.1.12" (page 57), item 74,<br>"Output FIFO Underrun Upper Panel Status (OUU) (read/write, maskable interrupt): Section<br>11.7.1.12" (page 57), item 76, "LCD Controller Register Locations: Section 13.6" (page 69), item 114,<br>"Timing Parameters: Section 13.6" (page 70), item 116, "Intel® StrongARM SA-1110 Device<br>Identification (ID) Code Register: Section 16.6.2" (page 71), and item 117, "Boundary-Scan Interface<br>Signals: Section 16.7" (page 71). |

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | Under Errata, changed the No Fix setting to Fix in the Status fields of Errata 13 — 16 and 18, established errata 17 as a No Fix, as well as adding the B4 step designator to the Affected Steppings fields for all forementioned. Also added two new errata (19 and 20) describing a failure to Reset UDC IN/OUT Data Packet Toggle Generation to DATA0/1 on Endpoints 1/2. And added errata describing the failure of the SSP bit to generate an interrupt request (21), describing the failure of the LCD Controller to operate correctly following reconfiguration events (22), and describing how a misaligned word access with a 16-bit data bus can generate incorrect data (23).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

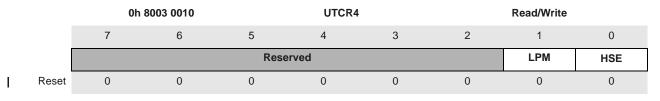

| 6/22/00  | 017     | Under Documentation Changes, added to documentation change 2 two tables to Section 13.1 describing output derating parameters for slow and fast output buffers, removed documentation changes 3—63 (having been incorporated into the revision 003 developer's manual) respective to Specification Update Revision 016. Also added updated information for the Reset Interrupt Mask, Receive Packet Error bit, Force Stall bit, and the UDC Control Register. Added information describing: Software Control of the UDC; a new section entitled "GPCLK Control Register 1"; changed section formally named "GPCLK Control Registers 1 and 2"; updated the table in the "GPCLK Register Locations" section. Made sentence corrections to the following sections: Serial Port 3 – UART; Baud Rate Divisor (BRD); Baud Rate Generation. Made general format corrections. Corrected bit assignment values to registers in Chapter 11. Rewrote sections 11.8.3, 11.8.3.4, 11.8.3.5, 11.8.3.6, 11.8.3.7, 11.8.3.3, 11.8.13.2, 11.8.13.13, 11.8.13.4, 11.8.13.5, 11.9, 9.3.4. Restructured Section 10.4.1. Added a note as appropriate in Chapters 9 and 11 to identify the use of a question mark as a value designator in register Reset fields. Added new section for GPCLK Register 1. Added new section describing software control of the UDC register. Rewrote Section 9.5.2.2, "exit Idle Mode." Added new data for the Force Stall bit.Added new output derating tables to Chapter 13. Updated GPCLK register locations table. Changed "899.78 MHz" to "900 Hz" as needed in Section 11.9. Updated section for GPCLK registers 1 and 2. Corrected baud rate divisor descriptions. Restructured Section 13.6. Corrected Figure 10-1. See Documentation Changes 41 through 97 for details. |

| 4/6/00   | 016     | Under Documentation Changes, added notes describing use definition of register reset value, listed in documentation changes 66–95. Corrected Transaction Formats figure (30) and corrected text and figure for Packet Formats (31). Added table footnote for GPIO functions and corrected USB web site listing. Corrected Figure 11-17 figure title and text located in paragraph above Figure 11-17. Corrected bit definitions for the MCCR0 register table. Corrected text in sections 11.8.3.8 and 11.8.12. Updated Table 12-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | Under Errata, added 5 errata documenting register reads/writes following SDRAM/SDROM reads<br>and sleep requests and SDRAM refresh issues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1/25/00  | 015     | Under Documentation Changes, removed documentation changes #63 — #99 (referencing the 014 specification update) from the specification update and applied them to the developer's manual; added two changes documenting a change in the exit idle mode process (Chapter 9) and a change in the register summary table (Appendix A).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |         | Under Specification Changes, added one line to Specification Changes table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1/11/00  | 014     | Under Documentation Changes, added 38 documentation changes removing all references to SDLC, substituting SDLC information with GPCLK information. Made four changes substituting RDN+1 with RDF+1. Changed one line in the parameters definition list in section 10.5.8 and added one footnote for Figure 10-18. Also added GPCLKR0 register to Section 11.9.3.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         | Under Errata, added one errata documenting UDC work-around procedure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12/07/99 | 013     | Under Errata, added nine errata; under Documentation Changes, changed output signals listed in Table 13-2; changes made to Section 10.1.7, Section 10.2.1, Section 10.2.2, Section 10.2.3, Section 10.2.4, Section 10.2.5, Section 10.3, Section 10.4.6, Section 10.5.1, Section 10.5.11, Section 10.7, Section 10.7.1, and Section 10.7.2; changed Section 13.6.SDLC feature changed from an errata to a specification change.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11/18/99 | 012     | Under Documentation Changes, changed ID code and added stepping information in section 5.2.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11/15/99 | 011     | Under Errata, added two errata; under Documentation Changes, changed title of section 13.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11/05/99 | 010     | Under Documentation Changes, added sentence to end of first paragraph in section 9.5.2.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11/03/99 | 009     | Under Documentation Changes, changed signal description of GPIO pin 25 in table in section 9.1.2; added note to end of section 11.11.6; deleted note to bit 3 of the RCSR register in section 9.6.1.2; revised bit 0 description of USB Device Controller (UDC) CR register in section 11.8.3.8; replaced section 11.10.2.3; corrected typo in table 9-3 title; changed sentence in section 10.8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/08/99 | 008     | Under Errata, added one errata; under Documentation Changes, added paragraph to section 16.6.3; added boundary-scan signals and pins table 16-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 09/15/99 | 007     | Under Documentation Changes, added footnote to GPIO Alternate Functions Table in Section 9.1.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 08/19/99 | 006     | Under Documentation Changes, changed settings for serial port 2 and serial port 4 in Table 11-6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 07/22/99 | 005     | Under Documentation Changes, changed code example for section 6.2.3; changed last sentence of section 9.5.3; added output signals to table 13-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 06/28/99 | 004     | Under Documentation Changes, removed section 16.8; changed Test Unit Control Register's description of bit 10; added change to Section 9.5.7.7; changed Figure 10-6; added change to section 10.5.1; added change to section 10.1; added change to section 10.2.2.and description of MDREFR:EAPD and MDREFR:KAPD bits; added step #8 to section 10.7.1; removed the SA-1110 Tool Chains and Operating Systems Table from the brief datasheet and the developer's manual; added change to section 9.5.6; added change to section 11.13.1; added change to section 11.13.6; added change to section 10.5.5. |

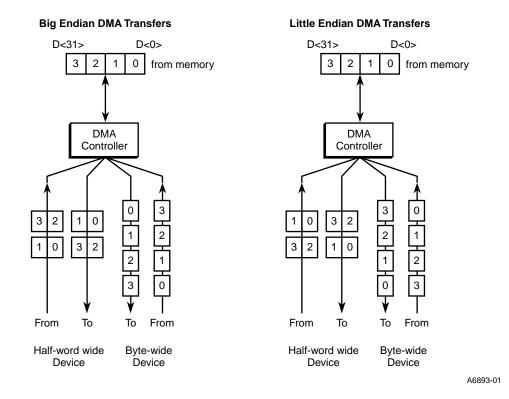

| 05/18/99 | 003     | Under Documentation Changes, added changes to the PPSR and PSDR register drawing graphics; added changes to the OS Timer Interrupt Enable register; added change to the Big and Little Endian DMA Transfers graphic; corrected peripheral pin assignments; changed 15 timing diagrams; changed bit 31 description in the DRAM Refresh Control Register; added changes to section 10.4.7; added changes to section 10.7.1; added changes to section 10.8.                                                                                                                                                  |

| 04/19/99 | 002     | Under Document Changes, added changes to section 1.1; section 9.1.2.1; section 3.1; section 10.2.4; and section 10.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 03/26/99 | 001     | This is the new specification update document. It contains all identified errata published prior to this date.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Preface

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

### **Affected Documents/Related Documents**

| Title                                                                               | Order      |

|-------------------------------------------------------------------------------------|------------|

| Intel <sup>®</sup> StrongARM <sup>*</sup> SA-1110 Microprocessor Developer's Manual | 278240-003 |

### Nomenclature

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

## Summary Table of Changes

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the SA-1110 microprocessor. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **Codes Used in Summary Table**

#### Stepping

|        | X:                       | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|--------|--------------------------|---------------------------------------------------------------------------------------------------------------|

|        | (No mark) or (Blank box) | : This erratum is fixed in listed stepping or specification change does not apply to listed stepping.         |

| Page   |                          |                                                                                                               |

|        | (Page):                  | Page location of item in this document.                                                                       |

| Status |                          |                                                                                                               |

|        | Doc:                     | Document change or update will be implemented.                                                                |

|        | Fix:                     | This erratum s intended to be fixed in a future step of the component.                                        |

|        | Fixed:                   | This erratum has been previously fixed.                                                                       |

|        | No Fix:                  | There are no plans to fix this erratum.                                                                       |

|        | Eval:                    | Plans to fix this erratum are under evaluation.                                                               |

| Daw    |                          |                                                                                                               |

#### Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### Errata (Sheet 1 of 2)

|   | No  |    |    | Step | pings |    |    | Dama | Chatura | FRRATA                                                                                                                                                                                             |

|---|-----|----|----|------|-------|----|----|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I | No. | A0 | В0 | B1   | B2    | B4 | B5 | Page | Status  | ERRATA                                                                                                                                                                                             |

| I | 1   | х  | х  | х    | х     | х  | х  | 20   | No Fix  | Incorrect Sign-Extended Value in Register After a Read Buffer Allocate                                                                                                                             |

| I | 2   | Х  | Х  | Х    | Х     | Х  | Х  | 20   | No Fix  | LCD Ghost Lines                                                                                                                                                                                    |

| I | 3   | Х  |    |      |       |    |    | 20   | Fixed   | High Current on VDDX During Reset                                                                                                                                                                  |

| I | 4   | Х  |    |      |       |    |    | 20   | Fixed   | High Current on VDDX During Sleep                                                                                                                                                                  |

| I | 5   | Х  |    |      |       |    |    | 20   | Fixed   | LCD State Machine Throughput Fails Using<br>SDRAM at Full-Memory Clock Frequency                                                                                                                   |

| I | 6   | х  |    |      |       |    |    | 21   | Fixed   | USB Stalls When More Than One USB Client Is<br>Present                                                                                                                                             |

| I | 7   | Х  |    |      |       |    |    | 21   | Fixed   | SDRAM Auto-Power-Up Failure                                                                                                                                                                        |

| I | 8   | х  |    |      |       |    |    | 21   | Fixed   | SDRAM RAS Precharge Counter May Not Work<br>in the Presence of SMROM                                                                                                                               |

| I | 9   | х  | Х  |      |       |    |    | 21   | Fixed   | DRAM Refresh Corrupting ROM/Flash Burst of 4/<br>8 Timing                                                                                                                                          |

| I | 10  | х  | х  | х    |       |    |    | 22   | Fixed   | Data Contention Caused by Hardware, Software,<br>or Watchdog Reset During SDRAM/SMROM<br>Reads                                                                                                     |

| I | 11  | х  | х  | х    |       |    |    | 23   | Fixed   | Erroneous SMROM Precharge All (PALL)<br>Command with Mode Register Set (MRS)<br>Command After Hardware, Software, Watchdog,<br>or Sleep Reset                                                      |

| T | 12  | х  | Х  | Х    |       |    |    | 23   | Fixed   | UDC Not Responding to IN Packet After<br>Receiving an SOF Packet                                                                                                                                   |

| I | 13  | х  | Х  | Х    |       |    |    | 23   | Fixed   | Corruption of Internal Register Reads/Writes<br>Following SDRAM/SDROM Reads                                                                                                                        |

| I | 14  | х  | х  | х    | х     |    |    | 24   | Fixed   | Failure on Sleep Request During Variable<br>Latency I/O to Perform SDRAM Self-Refresh and<br>Enter Sleep                                                                                           |

| I | 15  | х  | х  | х    | х     |    |    | 24   | Fixed   | Failure on Sleep Request During CBR Refreshes<br>to Perform SDRAM Self-Refresh Prior to Entering<br>Sleep                                                                                          |

| I | 16  |    |    |      | х     |    |    | 25   | Fixed   | Erroneous SDRAM Power-Down-Exit and<br>Power-Down Following Self-Refresh and Sleep<br>Entry                                                                                                        |

| I | 17  | х  | х  | х    | х     | х  | х  | 26   | No Fix  | Corruption of Internal Register Reads/Writes<br>Following Reads from SDRAM on 16-bit Data<br>Busses at Full Memory Clock Frequency                                                                 |

| I | 18  | х  | х  | х    | х     |    |    | 26   | Fixed   | Failure on Sleep Request During SDRAM Read/<br>Write Bursts to Precharge SDRAM Row Prior to<br>Performing SDRAM Self-Refresh and Entering<br>Sleep                                                 |

| I | 19  | х  | х  | х    | х     |    |    | 26   | Fixed   | Failure to Reset UDC OUT Data Packet Toggle<br>Checking to DATA0 on Endpoint 1 After a<br>Sequence of Setting/Clearing Force Stall Bit<br>(UDCCS1:FST) and Clearing Sent Stall Bit<br>(UDCCS1:SST) |

### Errata (Sheet 2 of 2)

|    | No. |    |    | Stepp | oings |    |    | Page | Status | ERRATA                                                                                                                                                                                              |

|----|-----|----|----|-------|-------|----|----|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | NO. | A0 | В0 | B1    | B2    | B4 | B5 | Faye | Status | ERRATA                                                                                                                                                                                              |

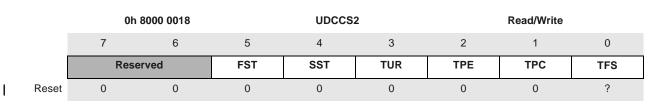

| I  | 20  | x  | x  | x     | х     |    |    | 27   | Fixed  | Failure to Reset UDC IN Data Packet Toggle<br>Generation to DATA0 on Endpoint 2 After a<br>Sequence of Setting/Clearing Force Stall Bit<br>(UDCCS2:FST) and Clearing Sent Stall Bit<br>(UDCCS2:SST) |

| I  | 21  | х  | х  | х     | х     | х  | х  | 27   | Eval   | Failure of Synchronous Serial Port (SSP)<br>Receiver Overrun Status Bit to Generate<br>Interrupt Request                                                                                            |

| I  | 22  | Х  | х  | х     | Х     | Х  | х  | 27   | No Fix | LCD Controller Fails to Operate Correctly<br>Following Reconfiguration                                                                                                                              |

| I  | 23  | Х  | х  | х     | Х     | Х  | х  | 27   | No Fix | Misaligned Word Accesses with 16-Bit Data Bus<br>May Produce Incorrect Data                                                                                                                         |

| I  | 24  | х  | х  | х     | Х     | х  | х  | 28   | No Fix | Software Sleep Status Bit (PSSR:SSS) May Be<br>Improperly Set After Sleep Wakeup                                                                                                                    |

| I  | 25  | х  | х  | х     | х     | х  | х  | 28   | No Fix | Improper Operation of LCD Controller LCCR2<br>Register EFW (End of Frame Line Clock Wait<br>Count)                                                                                                  |

| I  | 26  | х  | х  | х     | х     | х  | х  | 28   | No Fix | Between Two Successive PCMCIA Accesses,<br>Bus Arbiter Might Not Recognize Pending,<br>Highest-Priority, Bus Access Request From LCD<br>Controller                                                  |

| I  | 27  | х  | х  | х     | х     | х  | х  | 28   | No Fix | Incorrect Values Are Read from RTTR and RCNR<br>Registers Immediately After They Are Written                                                                                                        |

| I. | 28  | Х  | Х  | Х     | Х     | Х  |    | 29   | Fixed  | Incorrect Address Decode in USB Controller                                                                                                                                                          |

| I  | 29  | х  | х  | х     | Х     | Х  |    | 32   | Fixed  | USB Controller Endpoint 2 (IN) Transmits<br>Incorrect Data                                                                                                                                          |

### **Specification Changes**

|     | No. | Steppings |    |    |    |    |    |      | Ctatura | Presidentian Obernan                                 |

|-----|-----|-----------|----|----|----|----|----|------|---------|------------------------------------------------------|

| I   | NO. | A0        | B0 | B1 | B2 | B4 | B5 | Page | Status  | Specification Changes                                |

| I I | 1   | Х         | Х  | Х  | Х  | Х  | Х  | 33   | Eval    | SDLC Feature                                         |

| 1   | 2   | Х         | Х  | Х  | Х  | Х  | Х  | 33   | No Fix  | SDLC Feature Not Supported                           |

| I   | 3   | х         | х  | х  | х  | х  | Х  | 33   | No Fix  | Modifications in SDRAM/SMROM Data Input<br>Hold Time |

| I   | 4   | Х         | Х  | Х  | Х  | Х  | Х  | 33   | No Fix  | DC Operating Conditions: Section 12.2                |

| I   | 5   | х         | х  | х  | х  | х  | х  | 33   | No Fix  | Power Supply Voltages and Currents: Section 12.3     |

I

I

### **Specification Clarifications**

| No. |    | Steppings |    |    |    |    |      | Page Status | Specification Clarifications                         |