**CD1283**

#### IEEE 1284-Compatible Parallel Interface

# Datasheet

May 2001

# **Product Features**

#### Parallel Port (Peripheral-side)

High-speed, bidirectional, multi-protocol parallel port:

- Hardware implementation of all modes of the IEEE STD (Standard) 1284 specification (including automatic negotiation)

- -Centronics<sup>®</sup>-compatible mode

- -Reverse Byte mode

- -Reverse Nibble mode

- ECP (extended capabilities port) mode with run-length encoding/decoding

- -EPP (enhanced parallel port) mode

- —Up to 2-Mbytes/sec. transfer rate in ECP and EPP modes

- 64-byte parallel FIFO with DMA interface

- —64-byte FIFO can accommodate up to 4 Kbytes of compressed data with RLE (run-length encoded) compression enabled

- Supports peripheral-side operation

- Data and control input/output pads support IEEE STD1284 level-2 interface specification

- CPU bus interface

—High-speed slave DMA handshake interface

- -Three clocks per word DMA transfers

- -On-the-fly data compression using RLE (run-length encoded) encoding and decoding

- 8/16-bit data interface

- -BYTESWAP input provides easy interface to both Big- and Little-Endian systems

- Vectored interrupts simplify interrupt service routines

#### General

- System clock up to 25 MHz

- CMOS technology enables high speed and low power

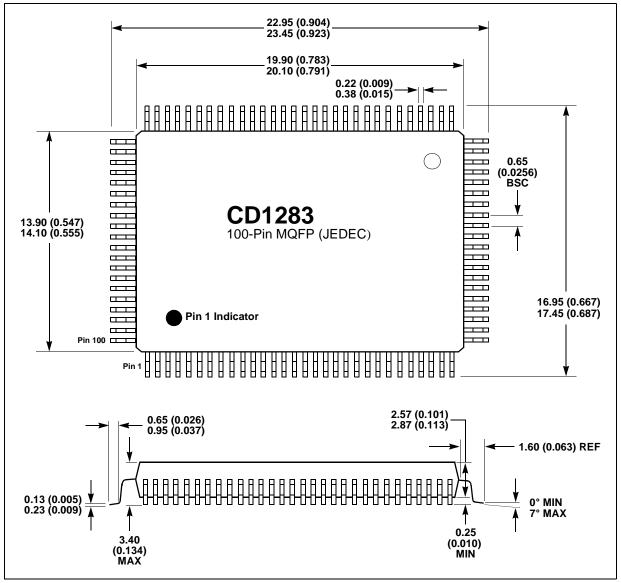

- Available in a 100-pin MQFP package

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The CD1283 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 Contents

| 1.0 | Ove        | rview                                                      | 9                                                                          |

|-----|------------|------------------------------------------------------------|----------------------------------------------------------------------------|

|     | 1.1        | Advantages                                                 | 9                                                                          |

| 2.0 | Con        | ventions                                                   | 11                                                                         |

| 3.0 | Pin l      | Information                                                | 13                                                                         |

|     | 3.1        | Pin Diagram                                                | 13                                                                         |

|     | 3.2        | Pin List                                                   |                                                                            |

|     | 3.3        | Pin Descriptions                                           | 16                                                                         |

| 4.0 | Reg        | ister Summary                                              | 19                                                                         |

|     | 4.1        | Register Summary Tables                                    | 19                                                                         |

| 5.0 | Fund       | ctional Description                                        | 22                                                                         |

|     | 5.1        | Device Architecture                                        |                                                                            |

|     | 5.2        | CPU Interface                                              |                                                                            |

|     | -          | 5.2.1 Read Cycles                                          |                                                                            |

|     |            | 5.2.2 Write Cycles                                         | 24                                                                         |

|     |            | 5.2.3 Service-Acknowledge Cycles                           | 24                                                                         |

|     |            | 5.2.4 DMA Cycles                                           |                                                                            |

|     |            | 5.2.5 Interrupts                                           |                                                                            |

|     |            | 5.2.6 DMAREQ* as Interrupt Source                          |                                                                            |

|     |            | 5.2.7 Daisy-Chain Configurations                           | 11<br>14<br>14<br>16<br>16<br>16<br>16<br>16<br>16<br>16<br>16<br>16<br>16 |

|     | 5.3        | Parallel Port Service Requests                             |                                                                            |

|     |            | 5.3.1 Hardware-Activated Acknowledge                       |                                                                            |

|     | <b>F</b> 4 | 5.3.2 Software-Activated Acknowledge                       |                                                                            |

|     | 5.4        | Parallel Port FIFO and Data Pipeline                       |                                                                            |

|     |            | 5.4.1 IEEE Standard 1284 Protocols<br>5.4.2 Bus Interface  |                                                                            |

|     |            | 5.4.2 Bus interface                                        |                                                                            |

|     |            | 5.4.4 Receive Direction                                    |                                                                            |

|     |            | 5.4.5 Receiving Compressed Data                            |                                                                            |

|     |            | 5.4.6 Stale Data (Stale, OneChar, and Timeout Status Bits) |                                                                            |

|     |            | 5.4.7 Transmit Direction                                   |                                                                            |

|     | 5.5        | Parallel Port Overview                                     |                                                                            |

|     | 0.0        | 5.5.1 Terminology                                          |                                                                            |

|     |            | 5.5.2 Signal Names                                         |                                                                            |

|     |            | 5.5.3 State Machine                                        | 07                                                                         |

|     |            | 5.5.4 Configuration                                        |                                                                            |

|     |            | 5.5.5 Interrupts                                           |                                                                            |

|     |            | 5.5.6 Manual Mode                                          |                                                                            |

|     |            | 5.5.7 Control Signals                                      |                                                                            |

|     |            | 5.5.8 Parallel Port Interface to the FIFO                  |                                                                            |

|     |            | 5.5.9 IEEE 1284-Protocol Negotiations                      |                                                                            |

|     |            | 5.5.10 Data Transfers                                      |                                                                            |

|     |            | 5.5.11 Compatibility Mode Status                           |                                                                            |

|     | 5.6        | IEEE 1284 Parallel Protocol Support                        | 40                                                                         |

|     |      | 5.6.1 Compatibility Mode                                      | 40 |

|-----|------|---------------------------------------------------------------|----|

|     |      | 5.6.2 Reverse-Nibble and Reverse-Byte Modes                   | 40 |

|     |      | 5.6.3 ID Request                                              | 41 |

|     |      | 5.6.4 ECP Mode                                                | 41 |

|     |      | 5.6.5 EPP Mode                                                | 41 |

|     | 5.7  | Protocol Timing                                               | 41 |

|     | 5.8  | General-Purpose I/O Port                                      |    |

|     | 5.9  | Parallel Port Interface                                       |    |

|     | 5.10 | Hardware Configurations                                       |    |

|     |      | 5.10.1 Interfacing to an Intel, Microprocessor-Based System   |    |

|     |      | 5.10.2 Interfacing to a Motorola, Microprocessor-Based System | 46 |

| 6.0 | Prog | ramming                                                       | 47 |

|     | 6.1  | Overview                                                      | 47 |

|     | 6.2  | Initialization                                                |    |

|     | 0.2  | 6.2.1 Device Reset                                            |    |

|     |      | 6.2.2 Service Acknowledge Handling                            |    |

|     | 6.3  | ASCII Code Tables                                             |    |

| 7.0 | Deta | iled Register Descriptions                                    | 53 |

| 1.0 | 7.1  | Global Registers                                              |    |

|     | 7.1  | 7.1.1 Access Enable Register                                  |    |

|     |      | 7.1.2 Global Firmware Revision Code Register                  |    |

|     |      | 7.1.3 General-Purpose I/O Direction Register                  |    |

|     |      | 7.1.4 General-Purpose I/O Register                            |    |

|     |      | 7.1.5 Parallel Interrupt Register                             |    |

|     |      | 7.1.6 Prescaler Period Register                               |    |

|     |      | 7.1.7 Service Request Register                                |    |

|     | 7.2  | Virtual Registers                                             |    |

|     |      | 7.2.1 End-of-Service Request Register                         |    |

|     |      | 7.2.2 Parallel Interrupt Vector Register                      |    |

|     | 7.3  | Parallel Pipeline Registers                                   |    |

|     |      | 7.3.1 Data Error Register                                     |    |

|     |      | 7.3.2 DMA Buffer Data Register                                |    |

|     |      | 7.3.3 Holding Register Status Register                        |    |

|     |      | 7.3.4 Host Timeout Value Register                             |    |

|     |      | 7.3.5 Local Interrupt Vector Register                         | 60 |

|     |      | 7.3.6 Parallel Auxiliary Control Register                     | 61 |

|     |      | 7.3.7 Parallel Channel Reset Register                         | 61 |

|     |      | 7.3.8 Parallel FIFO Control Register                          | 62 |

|     |      | 7.3.9 Parallel FIFO Empty Pointer Register                    | 63 |

|     |      | 7.3.10 Parallel FIFO Fill Pointer Register                    | 63 |

|     |      | 7.3.11 Parallel FIFO Holding Registers                        | 63 |

|     |      | 7.3.12 Parallel FIFO Quantity Register                        |    |

|     |      | 7.3.13 Parallel FIFO Status Register                          |    |

|     |      | 7.3.14 Parallel FIFO Threshold Register                       |    |

|     |      | 7.3.15 Run-Length Count Register                              |    |

|     |      | 7.3.16 Stale Data Timer Count Register                        |    |

|     |      | 7.3.17 Stale Data Timer Period Register                       |    |

|     | 7.4  | Parallel Port Registers                                       | 67 |

|       |       | 7.4.1     | EPP Address Register                       | 67 |

|-------|-------|-----------|--------------------------------------------|----|

|       |       | 7.4.2     | Input Value Register                       | 67 |

|       |       | 7.4.3     | Manual Data Register                       | 68 |

|       |       | 7.4.4     | Negotiation Enable Register                | 68 |

|       |       | 7.4.5     | Negotiation Status Register                | 69 |

|       |       | 7.4.6     | Ones Detect Register                       | 70 |

|       |       | 7.4.7     | Output Value Register                      |    |

|       |       | 7.4.8     | Parallel Channel Interrupt Enable Register |    |

|       |       | 7.4.9     | Parallel Channel Interrupt Status Register |    |

|       |       | 7.4.10    | Parallel Configuration Register            |    |

|       |       | 7.4.11    | Special Command Register                   |    |

|       |       | 7.4.12    | Short Pulse Register                       |    |

|       |       | 7.4.13    | 5 5                                        |    |

|       |       |           | Zeros Detect Register                      |    |

|       | 7.5   |           | Register                                   |    |

|       |       | 7.5.1     | Reset Command Register                     | 74 |

| 8.0   | Elect | trical Sp | pecifications                              | 76 |

|       | 8.1   | Absolut   | e Maximum Ratings                          |    |

|       | 8.2   | Recom     | mended Operating Conditions                | 76 |

|       | 8.3   | AC Cha    | aracteristics                              | 78 |

|       |       | 8.3.1     | Asynchronous Timing                        | 78 |

|       |       | 8.3.2     | Synchronous Timing                         | 84 |

| 9.0   | Pack  | age Dir   | nensions                                   | 90 |

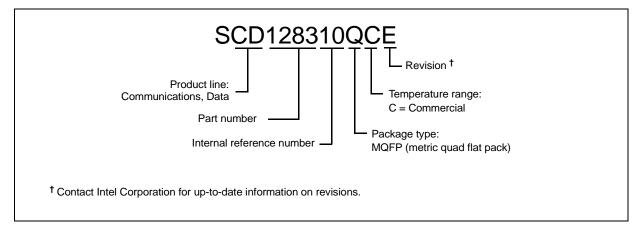

| 10.0  | Orde  | ering Inf | ormation                                   | 91 |

| Index |       |           |                                            |    |

| Figures |    |                                                                 |    |

|---------|----|-----------------------------------------------------------------|----|

| •       | 1  | Functional Block Diagram                                        | 10 |

|         | 2  | Functional Block Diagram                                        | 23 |

|         | 3  | Internal Address Generation                                     |    |

|         | 4  | CD1283 Daisy-Chain Configuration                                | 26 |

|         | 5  | Interrupt Generation Logic                                      |    |

|         | 6  | Control Signal Generation                                       |    |

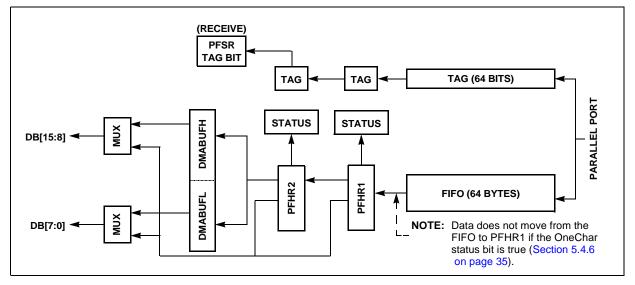

|         | 7  | FIFO Data Path Functional Diagram – Receive                     | 37 |

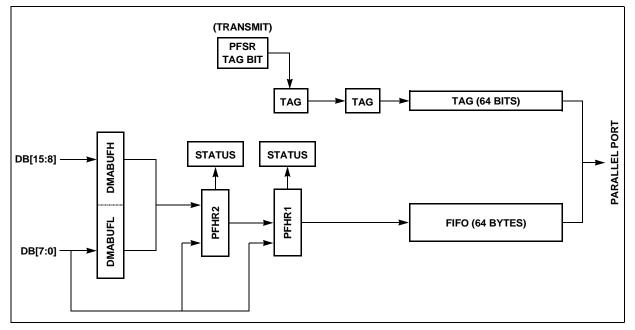

|         | 8  | FIFO Data Path Functional Diagram: Transmit                     | 38 |

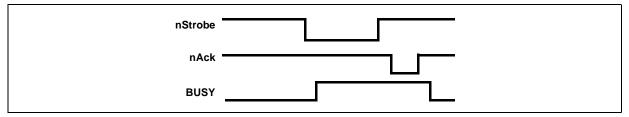

|         | 9  | Supported Compatibility Mode Timing                             | 40 |

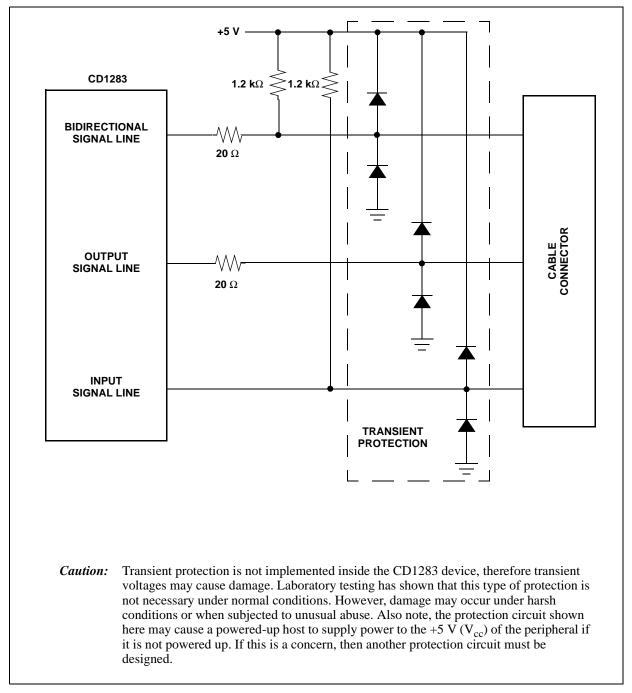

|         | 10 | Cable Connection                                                |    |

|         | 11 | External Buffer Control                                         | 44 |

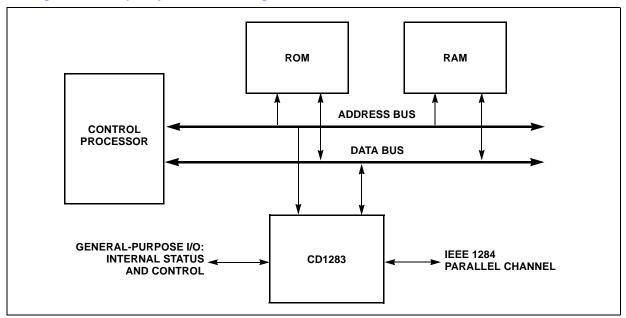

|         | 12 | Sample System Block Diagram                                     | 44 |

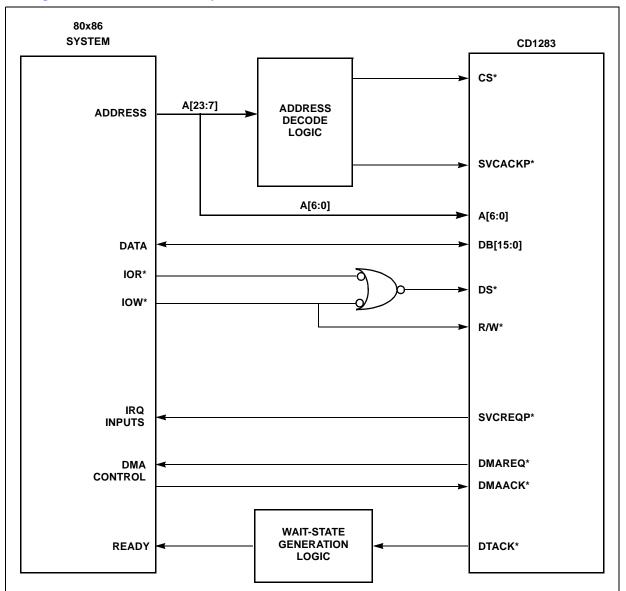

|         | 13 | Intel, 80x86 Family Interface                                   | 45 |

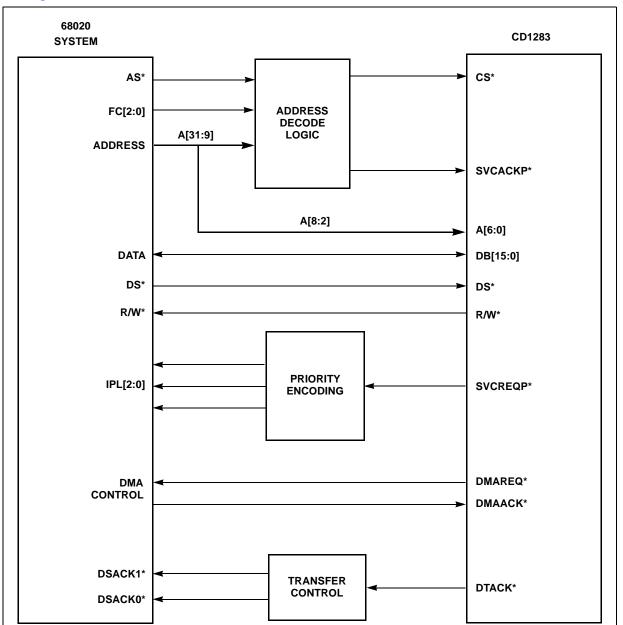

|         | 14 | Motorola, 68020 Interface                                       | 46 |

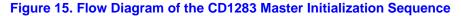

|         | 15 | Flow Diagram of the CD1283 Master Initialization Sequence       | 48 |

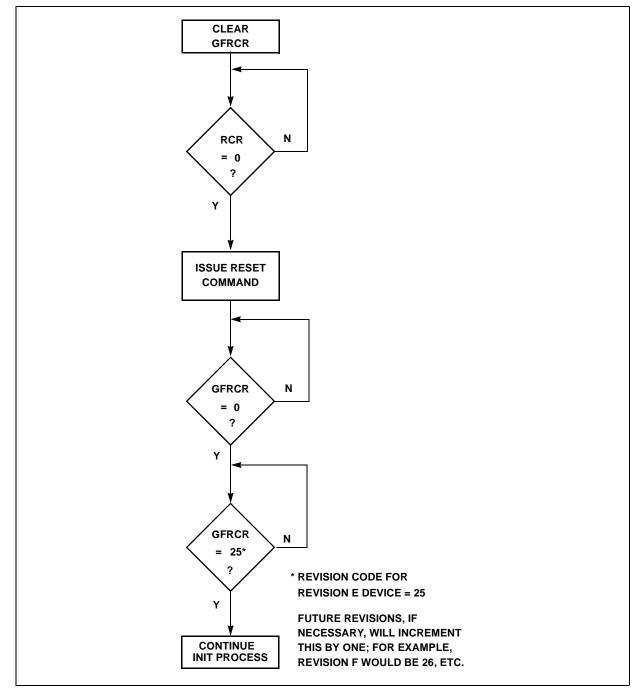

|         | 16 | Polling Flow Chart                                              | 51 |

|         | 17 | Reset Timing                                                    | 79 |

|         | 18 | Clock Timing                                                    | 80 |

|         | 19 | Asynchronous Read Cycle Timing                                  | 80 |

|         | 20 | Asynchronous Write Cycle Timing                                 | 81 |

|         | 21 | Asynchronous Service Acknowledge Cycle Timing                   | 82 |

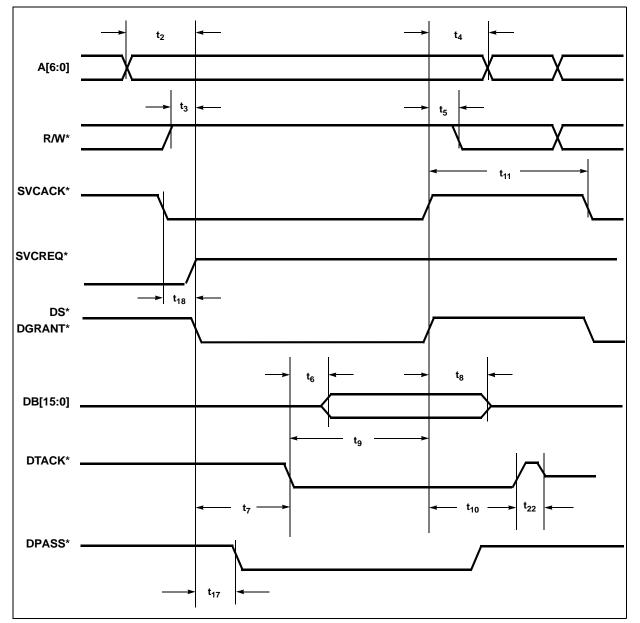

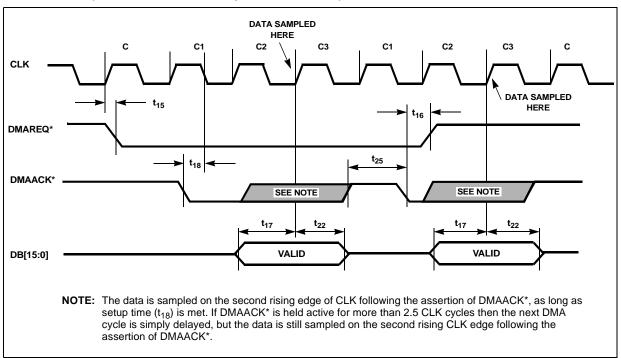

|         | 22 | Asynchronous DMA Read Cycle Timing                              |    |

|         | 23 | Asynchronous DMA Read Cycle Timing (Two Back-to-Back DMA Reads) | 83 |

|         | 24 | Asynchronous DMA Write Cycle Timing                             |    |

|         | 25 | Asynchronous DMA Write Cycle Timing                             | 84 |

|         | 26 | Synchronous Read Cycle Timing                                   | 86 |

|         | 27 | Synchronous Write Cycle Timing                                  | 87 |

|         | 28 | Synchronous Service Acknowledge Cycle Timing                    |    |

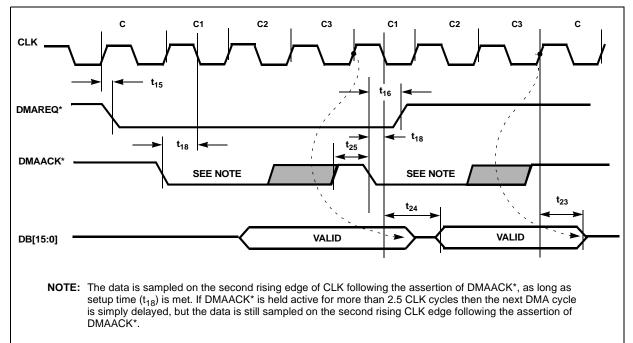

|         | 29 | Synchronous DMA Write Cycle Timing                              |    |

|         |    | (Two Back-to-Back 3-Cycle DMA Writes)                           | 89 |

|         | 30 | Synchronous DMA Read Cycle Timing                               |    |

|         |    | (Two Back-to-Back 3-Cycle DMA Reads)                            | 89 |

# **Tables**

| 1  | Global Registers                             | 19 |

|----|----------------------------------------------|----|

| 2  | Virtual Registers                            | 20 |

| 3  | Parallel Pipeline Registers                  | 20 |

| 4  | Parallel Port Registers                      |    |

| 5  | Special Register                             | 21 |

| 6  | LIVR[2:0] Encoding                           |    |

| 7  | System Clock Setup                           |    |

| 8  | Hexadecimal — Character                      | 51 |

| 9  | Decimal — Character                          | 52 |

| 10 | PIVR[2:0] Encoding                           | 56 |

| 11 | SPR Binary Values to Set 500-ns Pulse Widths |    |

| 12 | Asynchronous Timing Reference Parameters     |    |

| 13 | Synchronous Timing Reference Parameters      |    |

|    |                                              |    |

# **Revision History**

| Revision | Date | Description      |  |  |

|----------|------|------------------|--|--|

| 1.0      | 4/01 | Initial release. |  |  |

# 1.0 Overview

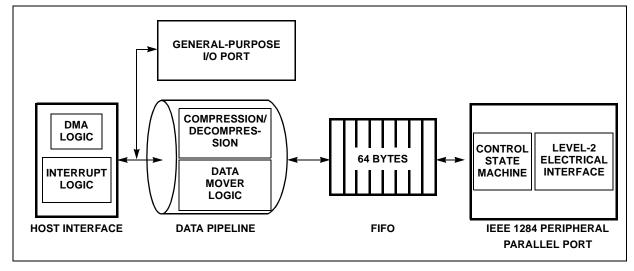

The CD1283 is a multi-function interface controller for printers, scanners, tape-drives, set-top boxes, data acquisition, and other applications that require high-speed, bidirectional, parallel communication with a host computer. All modes of the *IEEE STD 1284 Standard Signaling Method for Bidirectional Parallel Peripheral Interface for Personal Computers* specification are supported, including ECP, EPP, Reverse Byte, Reverse Nibble, and Compatible. With full support of this standard, the CD1283 provides compatibility with all types of host parallel ports, including older Centronics<sup>®</sup>, IBM<sup>®</sup> PS/2<sup>®</sup> bidirectional, and the latest IEEE 1284-compliant ports.

The dedicated state-machine design provides the fastest possible response times to all host signal changes, with 100% guaranteed compliance to all IEEE 1284 timing, protocol, and signaling requirements. The CD1283 device, operating at 25 MHz, has signal response times to support 2 Mbytes/sec. transfers, provided that a comparably fast host parallel port is used. This performance headroom guarantees that the faster data rates of future host parallel port implementations will be supported by peripheral applications using the CD1283.

In addition to the dedicated state machine, the CD1283 provides slave DMA support, and a 64-byte FIFO to allow maximum total throughput performance. Interrupts are generated based on status changes of the parallel port. Note, however that interrupts are not generated by FIFO threshold, or FIFO full/empty conditions. The DMA request signal can be used to generate interrupts as long as hardware and software implementation is handled correctly. If maximum performance is not a requirement, the device can be monitored and controlled by polling its detailed status registers.

Another unique feature of the CD128X series of devices is the dedicated hardware for RLE compression/decompression in ECP mode. Special logic is used to perform the ECP-RLE compression/decompression 'on-the-fly' while data is moved to and from the FIFO. All of these capabilities above and beyond the requirements of the IEEE 1284 specification permit the use of a less expensive microprocessor by reducing the required CPU bandwidth needed for the parallel port.

To aid in the development of hardware and software, an evaluation kit — complete with application notes and programmer's guide — is provided along with software examples and evaluation board schematics. The ISA add-in card is designed to demonstrate the capabilities of the CD128X family of devices, and enables software developers to begin testing code while the system hardware is still in development.

# 1.1 Advantages

### **Unique Features**

- Supports IEEE STD 1284 specification

- Hardware support of IEEE STD 1284 timings

- 64-byte FIFO

- Parallel port signals provide level-2 drive characteristics

- DMA channel

- ECP compression/decompression in hardware

### **Benefits**

- Multi-protocol bidirectional port for a wide range of applications.

- Up to 2 Mbytes/sec. transfer rate

- Provides future connectivity with new host systems

- Reduces software complexity and guarantees specification compliance.

- High throughput with reduced load on host CPU.

- Direct connection to printer cable; reduces chip count.

- Reduces host interface overhead. High-speed data movement between memory and parallel port.

- Reduces software complexity and increases throughput of compressed-data tranfers.

#### Figure 1. Functional Block Diagram

# 2.0 Conventions

intel

# **Abbreviations**

| Symbol | Units of Measure                 |  |

|--------|----------------------------------|--|

| °C     | degree Celsius                   |  |

| Hz     | hertz (cycles per second)        |  |

| Kbyte  | kilobyte (1,024 bytes)           |  |

| kHz    | kilohertz                        |  |

| kΩ     | kilohm                           |  |

| Mbyte  | megabyte (1,048,576 bytes)       |  |

| MHz    | megahertz (1,000 kilohertz)      |  |

| μF     | microfarad                       |  |

| μs     | microsecond (1,000 nanoseconds)  |  |

| mA     | milliampere                      |  |

| ms     | millisecond (1,000 microseconds) |  |

| ns     | nanosecond                       |  |

| рV     | picovolt                         |  |

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'N/C' indicates a pin that is a 'no connect'.

## Acronyms

| Acronym | Definition                                               |

|---------|----------------------------------------------------------|

| AC      | alternating current                                      |

| BIOS    | basic input/output system                                |

| CISC    | complex instruction set computer                         |

| CMOS    | complementary metal-oxide semiconductor                  |

| DC      | direct current                                           |

| DMA     | direct-memory access                                     |

| DRAM    | dynamic random-access memory                             |

| ECP     | extended capibilities port                               |

| EPP     | enhanced parallel port                                   |

| FIFO    | first in/first out                                       |

| GPIO    | general-purpose IO                                       |

| HCMOS   | high-performance complementary metal-oxide semiconductor |

| HDLC    | high-level data link control                             |

| Acronym | Definition (Continued)         |

|---------|--------------------------------|

| IC      | integrated circuit             |

| IDC     | instruction and data cache     |

| ISA     | industry standard architecture |

| LSB     | least-significant bit          |

| MPU     | microprocessing unit           |

| MSB     | most-significant bit           |

| PIO     | programmed I/O                 |

| PPP     | point-to-point protocol        |

| MQFP    | metric quad-flat pack          |

| RAM     | random-access memory           |

| RLE     | run-length encoded             |

| R/W     | read/write                     |

| SDLC    | synchronous data link control  |

| SRAM    | static random-access memory    |

| SWI     | software interrupt instruction |

| TLB     | translation look-aside buffer  |

| ТТВ     | translation table base         |

| TTL     | transitor-transitor logic      |

| VRAM    | video random-access memory     |

| WB      | write buffer                   |

# 3.0 Pin Information

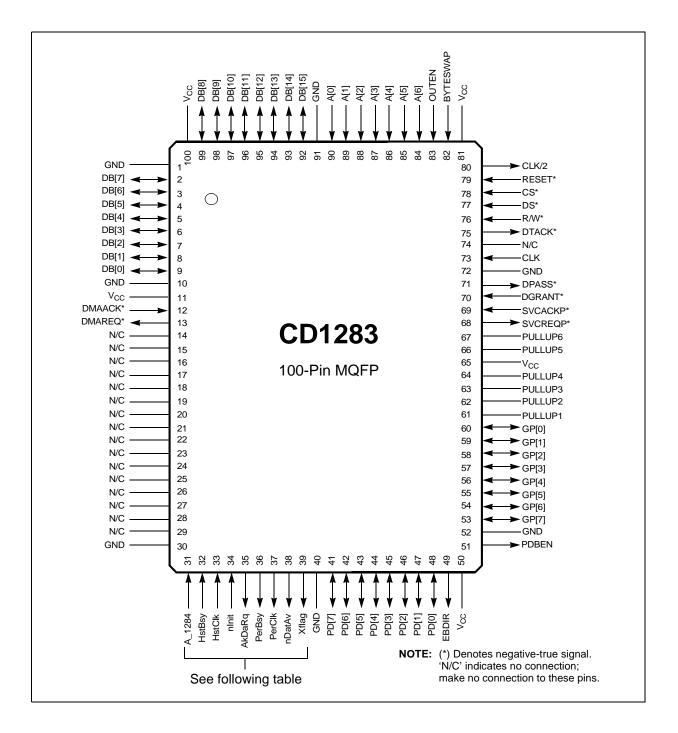

# 3.1 Pin Diagram

| Pin<br>Names | Compati-<br>bility | Reverse<br>Nibble<br>Mode | Reverse<br>Byte<br>Mode | ECP Mode | EPP<br>Mode |

|--------------|--------------------|---------------------------|-------------------------|----------|-------------|

|              |                    | Inp                       | uts                     |          |             |

| A_1284       | SLCTIN*            | A_1284                    | A_1284                  | A_1284   | nAStrb      |

| HstBsy       | AUTOFD*            | HstBsy                    | HstBsy                  | HstAck   | nDStrb      |

| HstClk       | STROBE*            | HstClk                    | HstClk                  | HstClk   | nWrite      |

| nInit        | INIT*              | nInit                     | nInit                   | nRevReq  | nlnit       |

|              |                    | Out                       | outs                    |          |             |

| AkDaR<br>q   | PError             | AkDaRq                    | AkDaRq                  | nAkRev   | USER1       |

| PerBsy       | BUSY               | PerBsy                    | PerBsy                  | PerAck   | nWait       |

| PerClk       | ACK*               | PerClk                    | PerClk                  | PerClk   | Intr        |

| nDatAv       | FAULT*             | nDatAv                    | nDatAv                  | nPerReq  | USER2       |

| XFlag        | SELECT             | XFlag                     | XFlag                   | XFlag    | USER3       |

# 3.2 Pin List

The following naming conventions are used in the pin-assignment tables:

- (\*) after a name indicates that the signal is active-low

- 'I' indicates the pin is input-only

- 'O' indicates the pin is output-only

- 'I/O' indicates the pin is bidirectional

- 'OD' indicates an open-drain output that the user must tie to  $V_{CC}$  through a pull-up resistor (usually about 1 k\Omega)

- 'TS' indicates tristate

- 'PU' indicates pull-up, which must also be tied to  $V_{CC}$  through a 1-k $\Omega$  resistor (note that all six PU pins can be wire-OR'ed through the same pull-up resistor)

- 'AR' indicates active release (pin drives high and releases to OD)

- a '-' indicates ascending pin numbers

- a ':' indicates descending pin numbers

| Pin Name | Туре | Number<br>of Pins | Pin<br>Numbers | Reset<br>State |

|----------|------|-------------------|----------------|----------------|

| A[6:0]   | I    | 7                 | 84–90          |                |

| BYTESWAP | I    | 1                 | 82             |                |

| CLK      | I    | 1                 | 73             |                |

| CLK/2    | 0    | 1                 | 80             | n/a            |

| CS*      | I    | 1                 | 78             |                |

| Pin Name        | Туре | Number<br>of Pins | Pin<br>Numbers               | Reset<br>State |

|-----------------|------|-------------------|------------------------------|----------------|

| DB[15:0]        | I/O  | 16                | 92–99, 2–9                   | TS             |

| DS*             | I    | 1                 | 77                           |                |

| DTACK*          | AR   | 1                 | 75                           | TS             |

| OUTEN           | I    | 1                 | 83                           |                |

| RESET*          | I    | 1                 | 79                           |                |

| R/W*            | I    | 1                 | 76                           |                |

| DMAREQ*         | 0    | 1                 | 13                           | High           |

| DMAACK*         | I    | 1                 | 12                           |                |

| SVCREQP*        | OD   | 1                 | 68                           | High           |

| SVCACKP*        | I    | 1                 | 69                           |                |

| DGRANT*         | I    | 1                 | 70                           |                |

| DPASS*          | 0    | 1                 | 71                           | High           |

| PD[7:0]         | I/O  | 8                 | 41–48                        | TS             |

| GP[7:0]         | I/O  | 8                 | 53–60                        | TS             |

| A_1284          | I    | 1                 | 31                           |                |

| nInit           | I    | 1                 | 34                           |                |

| HstBsy          | I    | 1                 | 32                           |                |

| HstClk          | I    | 1                 | 33                           |                |

| PerBsy          | 0    | 1                 | 36                           | Low            |

| PerClk          | 0    | 1                 | 37                           | High           |

| AkDaRq          | 0    | 1                 | 35                           | Low            |

| Xflag           | 0    | 1                 | 39                           | Low            |

| nDatAv          | 0    | 1                 | 38                           | High           |

| EBDIR           | 0    | 1                 | 49                           | High           |

| PDBEN           | 0    | 1                 | 51                           | Low            |

| GND             | I    | 7                 | 1, 10, 30, 40,<br>52, 72, 91 |                |

| PULLUP1         | PU   | 1                 | 61                           |                |

| PULLUP2         | PU   | 1                 | 62                           |                |

| PULLUP3         | PU   | 1                 | 63                           |                |

| PULLUP4         | PU   | 1                 | 64                           |                |

| PULLUP5         | PU   | 1                 | 66                           |                |

| PULLUP6         | PU   | 1                 | 67                           |                |

| V <sub>CC</sub> | I    | 5                 | 11, 50, 65,<br>81, 100       |                |

# 3.3 Pin Descriptions

| Symbol   | Pin No.    | Туре | Description (Sheet 1 of 3)                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|----------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A[6:0]   | 84–90      | I    | <b>ADDRESS BUS:</b> Together with CS* or one of the SVCACK* inputs and DS*, this input selects an on-chip register for a read or write operation or an acknowledgment to a service request.                                                                                                                                                                                                                                    |  |  |  |  |

|          |            |      | <b>BYTESWAP:</b> This input determines the byte order for 2-byte DMA transfers and for writes to the DMABUF register.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| BYTESWAP | 82         | I    | If BYTESWAP is set to '1', Data Bus bits 15:8 are driven with the byte transferred first<br>on the parallel port bus. Data Bus bits 7:0 are driven with the byte transferred second<br>on the parallel port bus. If BYTESWAP is set to '0', the data order is reversed, bits 7:0<br>are driven with the first byte transferred, and bits 15:8 are driven with the second byte<br>transferred.                                  |  |  |  |  |

| CLK      | 73         | I    | <b>SYSTEM CLOCK:</b> This input has a 25 MHz maximum; 16 MHz is the recommended minimum for satisfactory device performance.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| CLK/2    | 80         | 0    | <b>SYSTEM CLOCK DIVIDED BY TWO OUTPUT:</b> This signal is equivalent to the internal operating clock of the device.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CS*      | 78         | I    | ACTIVE-LOW CHIP SELECT: When active, the input CS* in conjunction with DS initiates a I/O cycle with the CD1283. CS* must be set to '1' during DMA read/wr operations.                                                                                                                                                                                                                                                         |  |  |  |  |

| DB[15:0] | 92–99, 2–9 | I/O  | <b>BIDIRECTIONAL DATA BUS [15:0]:</b> Only DMA transfers and writes to the DMA Buffer register are true 16-bit operations. During all register writes other than to the DMA Buffer register, only bits 7:0 are written to the addressed register. Register reads duplicate the register contents on both the lower byte, bits 7:0, and upper byte, bits 15:8.                                                                  |  |  |  |  |

| DS*      | 77         | I    | <b>ACTIVE-LOW DATA STROBE:</b> During an active I/O cycle, the input DS* strobes dat into on-chip registers on write cycles or enables data onto the data bus during read cycles. DS* is ignored during DMA operations.                                                                                                                                                                                                        |  |  |  |  |

| DTACK*   | 75         | AR   | ACTIVE-LOW DATA TRANSFER ACKNOWLEDGE: This output indicates: when the device has completed the requested I/O operation, and when the cycle may finish. This signal can be used to implement wait-state insertion for the local CPU. It is an Active Release output, driving to logic '1' then releasing to OD. DTACK* must be tied to external V <sub>CC</sub> with a pull-up resistor. DTACK* is not activated on DMA cycles. |  |  |  |  |

| OUTEN    | 83         | I    | <b>OUTPUT ENABLE:</b> This pin must be set to '1' to enable output pin functions. When OUTEN is set to '0', it forces all pins that can act as outputs to remain in a tristate condition.                                                                                                                                                                                                                                      |  |  |  |  |

|          |            |      | OUTEN is used as a test input and is not normally used in an end application. User designs should tie this pin to $V_{CC}$ through a pull-up resistor.                                                                                                                                                                                                                                                                         |  |  |  |  |

| RESET*   | 79         | Ι    | <b>ACTIVE-LOW RESET INPUT:</b> Initializes the device to the default condition. All internal registers are set to their reset condition and all transfer operations are set to the default state.                                                                                                                                                                                                                              |  |  |  |  |

| R/W*     | 76         | I    | <b>READ/WRITE*:</b> This pin must be set to '1' for a register read operation and set to '0' for a register write operation. This input is ignored for DMA operations.                                                                                                                                                                                                                                                         |  |  |  |  |

| DMAREQ*  | 13         | 0    | ACTIVE-LOW DMA REQUEST: When the internal control bit DMAen is set, the output DMAREQ* is asserted whenever internal FIFO conditions warrant a DMA transfer. DMAREQ* is deasserted on the falling edge of DMAACK* when DMA transfers must not continue past the current transfer.                                                                                                                                              |  |  |  |  |

| DMAACK*  | 12         | Ι    | <b>ACTIVE-LOW DMA ACKNOWLEDGE:</b> This signal must never be asserted unless in response to a DMAREQ* from the device. DMAACK* is the only bus handshake signal recognized during a DMA transfer. (CS* must be high whenever DMAACK* is asserted.) The direction of the DMA transfer is determined by the internal control bit DMAdir.                                                                                         |  |  |  |  |

| Symbol   | Pin No.      | Туре          | Description (Sheet 2 of 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SVCREQP* | 68           | OD            | <b>ACTIVE-LOW SERVICE REQUEST PARALLEL:</b> This is an open-drain output and must be tied to external V <sub>CC</sub> through a pull-up resistor. Note that this output is only activated by certain conditions on the parallel port (such as, negotiation changes, direction changes, etc.). SVCREQP* is not activated by FIFO threshold, or FIFO full/empty conditions (refer to Chapter 5.0 for information on how to use DMAREQ* to implement a fully interrupt-driven system). |

| SVCACKP* | 69           | I             | <b>ACTIVE-LOW SERVICE ACKNOWLEDGE PARALLEL:</b> This input must not be driven active except in response to a parallel service request presented by the device.                                                                                                                                                                                                                                                                                                                      |

| DGRANT*  | 70           | I             | <b>ACTIVE-LOW DAISY GRANT:</b> This input is driven active during service acknowledge cycles to enable the daisy-chain function. This input, when qualified with DS* and a valid service acknowledge (SVCACKP*), activates the service acknowledge cycle.                                                                                                                                                                                                                           |

| DPASS*   | 71           | ο             | ACTIVE-LOW DAISY PASS: This output is driven active during service acknowledge cycles to enable the next device in the daisy-chain. It is driven active when no valid service request exists and the service acknowledge input is active. In multiple CD1283 designs, this signal is normally connected to the DGRANT* input of the next device in the chain.                                                                                                                       |

| PD[7:0]  | 41–48        | I/O           | <b>PARALLEL PORT DATA LINES [7:0]:</b> Bidirectional, depending on the protocol being used, these signals are used to transfer data over the interface between the master and slave.                                                                                                                                                                                                                                                                                                |

| GP[7:0]  | 53–60        | I/O           | <b>GENERAL-PURPOSE I/O [7:0]:</b> General-purpose input/output port data lines. These signals are individually direction-programmable, acting as inputs or outputs. The direction of each signal is controlled by the corresponding bit in the GPDIR register. Control/status of the actual signals is provided through the GPIO register.                                                                                                                                          |

| A_1284   | 31           | I             | ACTIVE-HIGH 1284 ACTIVE INPUT: (SLCTIN* in Compatibility mode).                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nlnit    | 34           | I             | ACTIVE-LOW INIT SIGNAL: (INIT* in Compatibility mode).                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HstBsy   | 32           | I             | ACTIVE-HIGH HOST BUSY SIGNAL: (AUTOFD* in Compatibility mode).                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HstClk   | 33           | I             | ACTIVE-LOW HOST CLOCK SIGNAL: (STROBE* in Compatibility mode).                                                                                                                                                                                                                                                                                                                                                                                                                      |

| inputs   | to the CD128 | 3. Their fund | ake signals are driven by the master in an IEEE Std 1284 interface, and as such are ctions depend on the transfer protocol selected. Refer to the IEEE Std 1284-1994 . (See Chapter 10.0 for ordering information.)                                                                                                                                                                                                                                                                 |

| PerClk   | 37           | 0             | ACTIVE-LOW PERIPHERAL CLOCK: (ACK* in Compatibility mode)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PerBsy   | 36           | 0             | ACTIVE-HIGH PERIPHERAL BUSY: (BUSY in Compatibility mode)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AkDaRq   | 35           | 0             | ACKNOWLEDGE DATA REQUEST: (PERROR* in Compatibility mode)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Xflag    | 39           | 0             | EXTENSIBILITY FLAG: (SELECT in Compatibility mode)                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| nDatAv   | 38           | 0             | ACTIVE-LOW DATA AVAILABLE SIGNAL: (FAULT* in Compatibility mode)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Symbol                                                                                                                                                                                                                                                                                                                                    | Pin No. | Туре | Description (Sheet 3 of 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <b>NOTE:</b> The above five parallel handshake signals are driven by the slave in an IEEE Std 1284 interface, and as such are outputs from the CD1283. Their functions depend on the transfer protocol selected. Refer to the IEEE Std 1284-199 document for protocol functions. (See Section 5.4.1 on page 33 for ordering information.) |         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

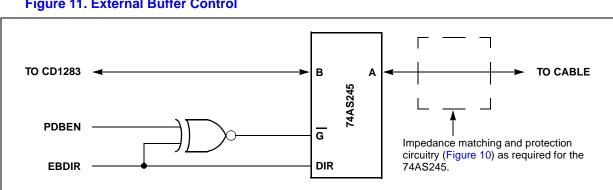

| EBDIR                                                                                                                                                                                                                                                                                                                                     | 49      | 0    | <b>EXTERNAL BUFFER DIRECTION:</b> This signal is controlled by the internal parallel port control state machine and can be used to control the direction of an external buffer connected to the Parallel Port data bus. An external buffer might be desirable in applications that require higher drive capacity than that provided by the CD1283. EBDIR can be used in conjunction with PDBEN to control this buffer. EBDIR is a logic '0' when the parallel data bus is in an output mode, and a logic '1' when in an input mode. It can be connected directly to the direction control input of a 74245-type device.                                                          |  |  |  |  |  |  |

| PDBEN                                                                                                                                                                                                                                                                                                                                     | 51      | 0    | <b>PARALLEL DATA BUS ENABLE:</b> This signal can control a buffer on the Parallel Port data lines in applications requiring more signal-drive capability than provided by the CD1283. PDBEN is controlled by the internal Parallel Port control state machine. When low, the parallel port data bus is not driving; when high, the port is in output mode and is actively driving. PDBEN will toggle between the on and off states during output modes and is only active (high) while the data bus pins are in the active driving state. PDBEN can be logically connected to the enable control of 74245 (or equivalent) bidirectional buffers (see Section 5.9 and Figure 11). |  |  |  |  |  |  |

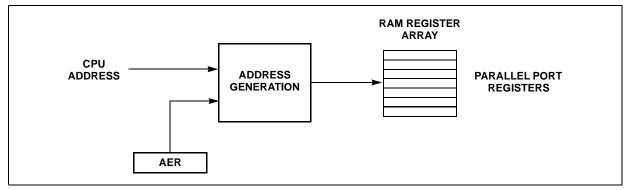

# 4.0 Register Summary

Local CPU communication with the CD1283 occurs through a register set. Within this register set, there are four types of registers:

- Global, common to all functions of the device

- Parallel pipeline

- Parallel port

- Service-acknowledge accessible

Global registers are always available to the CPU and their addresses are not affected by the contents of the AER (this register is provided to maintain compatibility with the CD1284).

*Note:* AER must be set to '00h' and must not be changed (except to access RCR), or access to many registers will not work properly!

The following tables define the register names, read and write access modes, internal address offsets, and bit definitions. A detailed description of each register, its contents and functions can be found in Chapter 7.0 The address offset defined is the binary value that should be applied to the address inputs (A[6:0]) during I/O cycles.

Note that the addresses are shown relative to the CD1283 definition of address lines. In 16- and 32bit systems, it is a common practice to connect 8-bit peripherals to only one byte lane. Thus, in 16bit systems, the CD1283 appears at every other address (for example, the CD1283 A[0] input is connected to CPU A[1]). In 32-bit systems, the CD1283 appears at every fourth address (CD1283 A[0] is connected to CPU A[2]). In either of these cases, the address used by the programmer will be different than what is shown in the tables. For instance, in a 16-bit Motorola<sup>®</sup> 68000-based system, the CD1283 is placed on data lines D[7:0], which are at odd addresses in the Motorola scheme of addressing. The CD1283 A[0] input is connected with A[1] of the 68000, A[1] with A[2], and so on. Thus, the CD1283 address 0x40 becomes 0x81 to the programmer. It is leftshifted one bit and A[0] must be '1' for low-byte (D[7:0]) accesses.

# 4.1 Register Summary Tables

| Name  | Hex | Bit 7  | Bit 6                  | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------|-----|--------|------------------------|----------|--------|--------|--------|--------|--------|------|

| AER   | 68  | Poll   | Poll                   | Poll     | Poll   | Poll   | 0      | 0      | 0      | 53   |

| GFRCR | 4F  |        | Firmware Revision Code |          |        |        |        |        |        | 53   |

| GPDIR | 71  | Dir 7  | Dir 6                  | Dir 5    | Dir 4  | Dir 3  | Dir 2  | Dir 1  | Dir 0  | 54   |

| GPIO  | 70  | Data 7 | Data 6                 | Data 5   | Data 4 | Data 3 | Data 2 | Data 1 | Data 0 | 54   |

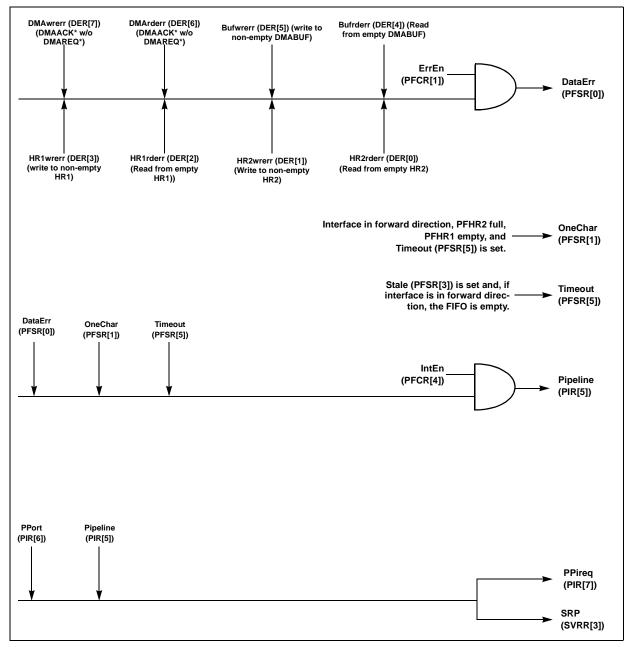

| PIR   | 61  | PPIreq | PPort                  | Pipeline | 0      | 0      | 0      | 0      | 0      | 54   |

| PPR   | 7E  |        | Binary Value           |          |        |        |        |        |        | 55   |

| SVRR  | 67  | DMAREQ | n/u                    | n/u      | n/u    | SRP    | n/u    | n/u    | n/u    | 55   |

#### Table 1. Global Registers

#### Table 2. Virtual Registers

| Name  | Hex | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|------|

| EOSRR | 60  | Χ†    | Х     | Х     | Х     | Х     | Х     | Х     | Х     | 56   |

| PIVR  | 40  | Х     | Х     | Х     | Х     | Х     | IT2   | IT1   | IT0   | 56   |

† 'X' indicates 'don't care'.

# Table 3. Parallel Pipeline Registers

| Name                     | Hex | Bit 7    | Bit 6    | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0    | Page |

|--------------------------|-----|----------|----------|-------------|---------------|--------------|--------------|--------------|----------|------|

| DER                      | 33  | DMAwrerr | DMArderr | Bufwrerr    | Bufrderr      | HR1wrerr     | HR1rderr     | HR2wrerr     | HR2rderr | 57   |

| DMABUF<br>(High<br>byte) | 30  | 15       | 14       | 13          | 12            | 11           | 10           | 9            | 8        | 58   |

| DMABUF<br>(Low byte)     | 30  | 7        | 6        | 5           | 4             | 3            | 2            | 1            | 0        | 58   |

| HRSR                     | 34  | HR1full  | HR1tag   | HR2full     | HR2tag        | DMAfull      | DMAempty     | DMAact       | Ctnot0   | 58   |

| HTVR                     | 24  | HTVR[7]  | HTVR[6]  | HTVR[5]     | HTVR[4]       | HTVR[3]      | HTVR[2]      | HTVR[1]      | HTVR[0]  | 59   |

| LIVR                     | 18  |          | Use      | r-Defined E | Bits          |              | IT2          | IT1          | IT0      | 60   |

| PACR                     | 3F  | ShrtTen  | ShrtStal | StaleOff    | FIFOlock      | ClearTO      | 0            | AsyncDM<br>A | 0        | 61   |

| PCRR                     | 6C  | 0        | 0        | 0           | 0             | 0            | 0            | 0            | PChReset | 61   |

| PFCR                     | 31  | FIFOres  | DMAen    | DMAdir      | IntEn         | RLEen        | setTAG       | ErrEn        | DMAbufWe | 62   |

| PFEP                     | 39  | 0        | 0        |             | (             | 6-Bit Binary | FIFO Pointer | Value        |          | 63   |

| PFFP                     | 38  | 0        | 0        |             | (             | 6-Bit Binary | FIFO Pointer | Value        |          | 63   |

| PFHR1                    | 35  |          |          |             | 8-Bit Cl      | naracter Dat | а            |              |          | 63   |

| PFHR2                    | 36  |          |          |             | 8-Bit Cl      | naracter Dat | а            |              |          | 63   |

| PFQR                     | ЗA  |          |          | Data or \$  | Space Avail   | able in FIFC | ) — Max 0x40 |              |          | 64   |

| PFSR                     | 32  | FFfull   | FFempty  | Timeout     | HRtag         | HRdata       | Stale        | OneChar      | DataErr  | 64   |

| PFTR                     | 3B  | 0        |          |             | DN            | A Transfer   | Threshold    |              |          | 65   |

| RLCR                     | 37  | 0        |          |             | 7-Bit         | Unsigned B   | inary Count  |              |          | 66   |

| SDTCR                    | 3D  |          |          |             | 8-Bit Stale I | Data Timer ( | Count        |              |          | 66   |

| SDTPR                    | 3C  |          |          | 8           | -Bit Stale D  | ata Timeout  | Value        |              |          | 67   |

#### Table 4. Parallel Port Registers (Sheet 1 of 2)

| Name | Hex | Bit 7 | Bit 6                                                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Page |

|------|-----|-------|----------------------------------------------------------|-------|-------|-------|-------|--------|--------|------|

| EAR  | 25  |       | 8-Bit Binary Value                                       |       |       |       |       |        |        |      |

| IVR  | 2E  | 0     | 0                                                        | 0     | 0     | A1284 | nInit | HstBsy | HstClk | 67   |

| MDR  | 21  |       | 8-Bit Binary Data                                        |       |       |       |       |        |        |      |

| NER  | 28  | 0     | RID                                                      | 0     | EPP   | RLE   | ECP   | RVB    | RVN    | 68   |

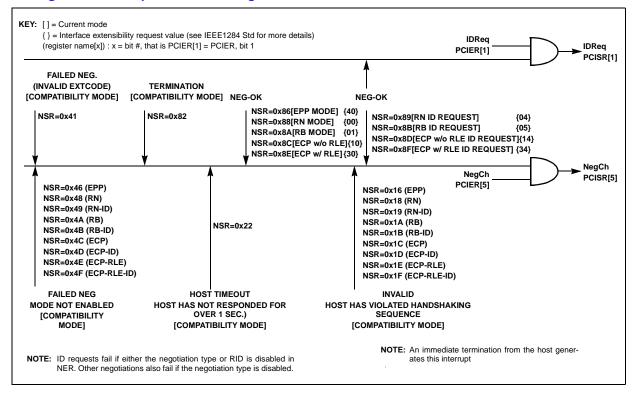

| NSR  | 29  | NegOK | legOK NegFl HostTO Invalid 4-Bit Negotiation Result Code |       |       |       |       |        |        | 69   |

| Name  | Hex | Bit 7              | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2      | Bit 1  | Bit 0  | Page |

|-------|-----|--------------------|--------|--------|--------|------------|------------|--------|--------|------|

| ODR   | 2D  | 0                  | 0      | 0      | 0      | A1284      | nInit      | HstBsy | HstClk | 70   |

| OVR   | 2B  | PerBsy             | PerClk | AkDaRq | xFlag  | nDatAv     | 0          | 0      | 0      | 70   |

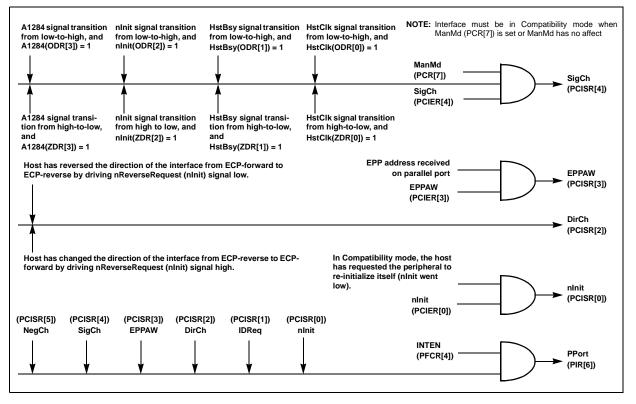

| PCIER | 22  | 0                  | 0      | NegCh  | SigCh  | EPPAW      | DirCh      | IDReq  | nINIT  | 71   |

| PCISR | 23  | 0                  | 0      | NegCh  | SigCh  | EPPAW      | DirCh      | IDReq  | nINIT  | 71   |

| PCR   | 20  | ManMd              | E1284  | ETxfr  | lg_SEL | HTmrTst[1] | HTmrTst[0] | MMDir  | ManOE  | 71   |

| SCR   | 2A  | 0                  | 0      | 0      | 0      | ClrPs      | SetPs      | EPIrq  | RevRq  | 72   |

| SPR   | 26  | 8-Bit Binary Value |        |        |        |            |            |        |        |      |

| SSR   | 2F  | 0                  | 0      | 0      | 0      | A1284      | nInit      | HstBsy | HstClk | 74   |

| ZDR   | 2C  | 0                  | 0      | 0      | 0      | A1284      | nInit      | HstBsy | HstClk | 74   |

# Table 4. Parallel Port Registers (Sheet 2 of 2)

# Table 5. Special Register

| Name | Hex | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|------|-----|-------|-------|-------|-------|-------|-------|-------|-------|------|

| RCR  | 05  | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 74   |

# 5.0 Functional Description

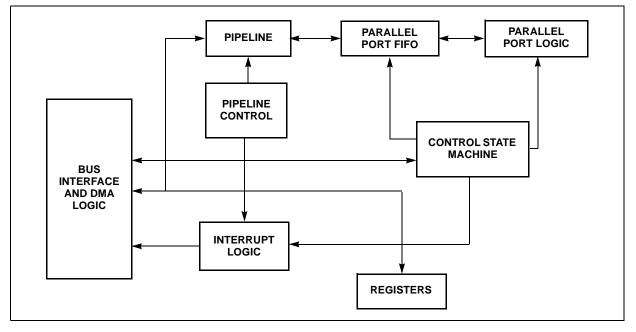

# 5.1 Device Architecture

The CD1283 consists of dedicated logic tailored to the function of sending and receiving parallel data. The device implements an IEEE 1284-compliant parallel port with a specialized data pipeline designed for high-speed transfers.

To maintain binary compatibility with the CD1284, much of the architectural layout has been duplicated. Therefore, access to the register set of the parallel channel is only possible after loading the AER with the CD1284 occupied parallel port address — namely channel 0. For all channel-specific accesses, the CPU first loads the AER with a pointer to channel 0. Thereafter, all read and write operations occur through the parallel channel.

The parallel channel is comprised of a FIFO and DMA data interface, as well as a high-speed state machine to manage all modes defined in the IEEE Std 1284-1994 specification, *Standard Signaling Method for a Bidirectional Parallel Peripheral Interface for Personal Computers*. The parallel port performs the slave or peripheral function of the IEEE Std 1284 interface, and can accept negotiations into any or all of the IEEE defined modes.

# 5.2 CPU Interface

The CPU interface is comprised of a 7-bit address bus, 8-bit bidirectional data bus, 16-bit DMA port, and control inputs to identify the type of I/O cycle occurring. The signaling and basic timing match that of the Motorola<sup>®</sup> 68000 family. With the addition of minimal glue logic, the interface will work with nearly any CPU. A special input is provided to swap the bytes on the data bus to reduce the necessary logic needed with Intel<sup>®</sup>-style CPUs.

The interface is completely compatible with the CD1284. Therefore, a CD1283 can be inserted into a system in instead of a CD1284 and the parallel port operates without any modifications to the CPU interface, parallel port hardware or software.

In most cases, when the CPU reads or writes an internal CD1283 location, it accesses a location in a RAM array to serve as a bank of registers. However, some locations are mapped to actual hardware resources. For example, when a hard output signal is required (such as a service-request output in the SVRR) or a read of the actual state of an input is necessary (such as a parallel port handshake signal in the IVR).

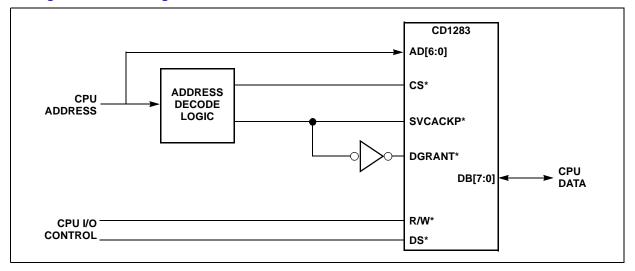

**Figure 3. Internal Address Generation**

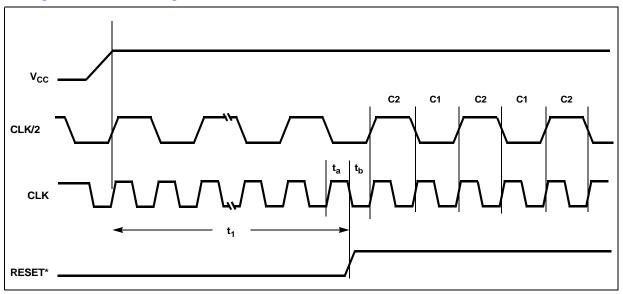

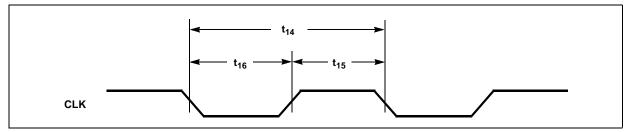

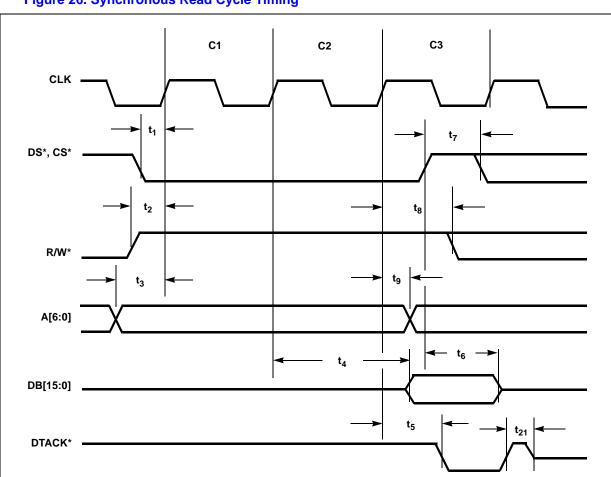

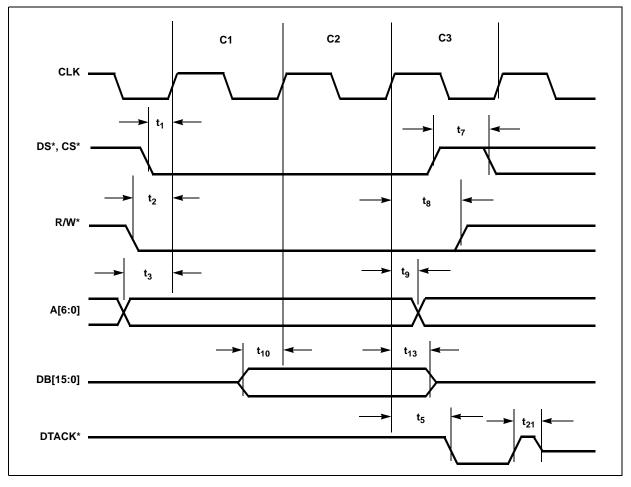

The CD1283 is a synchronous device. All internal operations occur on edges and levels (phases) of the internal clock. The internal clock is generated by dividing the external (system) clock by two. When the CPU performs an I/O cycle with the CD1283, it strobes; address and data are sampled on the rising edges of the internal clock. As illustrated in Chapter 8.0, external control signals must meet setup times with respect to system clock edges. Once a cycle starts, the sequence of events is locked to the CD1283 clock, with events (address setup, write data setup, and read data available) occurring at predictable times.

It is not necessary to design a synchronous interface to the CD1283. In an asynchronous design, the DTACK\* (Data Transfer Acknowledge) signal indicates that the CD1283 has completed the requested data transfer for all I/O cycles except DMA. DTACK\* can be an input to wait-state generation logic that pauses the CPU until the operation is complete. If the CS\* and DS\* strobes (Chip Select and Data Strobe) do not meet the minimum setup time with respect to the system clock edge, the CD1283 does not detect the I/O request, and the cycle delays for two full-system clock cycles, meeting the setup time. The I/O cycle commences and follows the predictable timing with DTACK\* signaling the end.

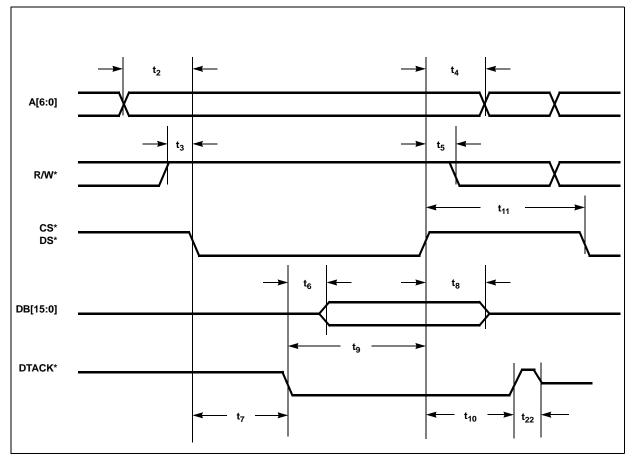

### 5.2.1 Read Cycles

Read cycles are initiated when both the CS\* and DS\* inputs are activated and the R/W\* (read/ write) input is high. All strobes and address inputs must meet the setup times as specified in Chapter 8.0. Both the CS\* and DS\* signals must be valid for a cycle to start. Cycle times are measured from whichever of the two signals goes active last. The CD1283 signals the completion of the read cycle (placing the data from the addressed register on the data bus pins) by activating DTACK\*. The read cycle terminates when the CPU removes CS\* and DS\*.

### 5.2.2 Write Cycles

Write cycle timing and strobe activity is nearly identical to read cycles except that the R/W\* signal must be held low. Write data, strobes, and address inputs must meet setup and hold times as specified in Chapter 8.0. DTACK\* indicates that the cycle is complete and the CD1283 has accepted the data. Removing both CS\* and DS\* terminates the cycle.

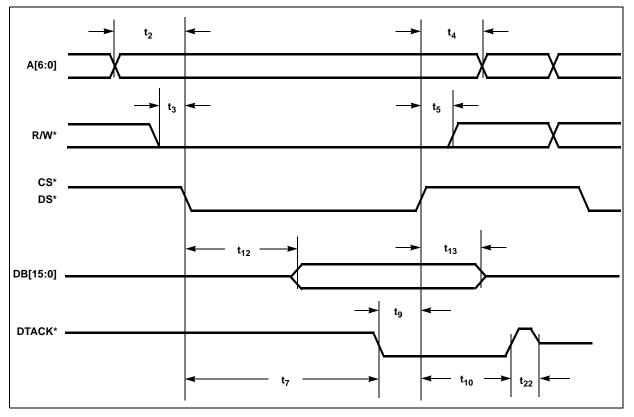

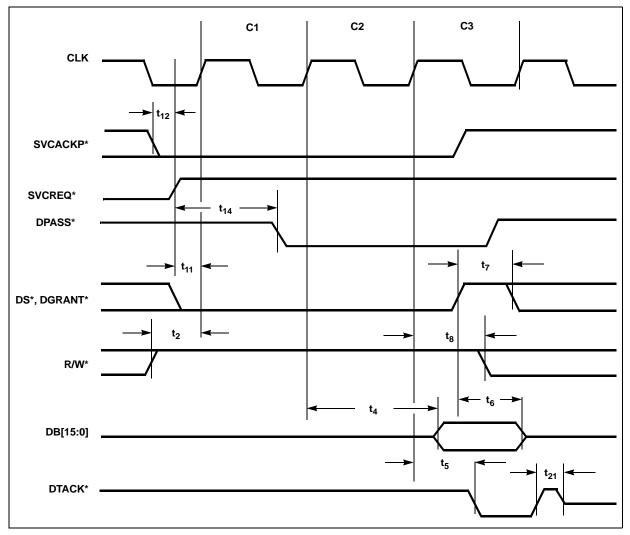

### 5.2.3 Service-Acknowledge Cycles

Service-acknowledge cycles are a special-case read cycle. Timing is basically the same as a normal read cycle, but the SVCACKP\* input is activated instead of the CS\* input (a slightly longer setup time is required on the SVCACKP\* input than on the CS\* input). The data that the CD1283 provides during the read cycle is the contents of the PIVR. As with read and write cycles, DTACK\* indicates the end of the cycle and removing DS\* and SVCACK\* terminates the cycle.

*Note:* With regard to timing and service-acknowledge cycles, when the CPU completes the service routine and writes to the EOSRR, a subsequent I/O cycle, if started immediately, is delayed approximately 1 μs by delaying DTACK\*. This is due to the time required by the internal processor to complete activities associated with the service-acknowledge cycle.

These activities are primarily interrupt-logic updates and restoration of the environment prior to the service-request/service-acknowledge procedure. These must be completed before any internal registers are modified by the CPU.

If the CPU attempts an access before the internal procedures are complete, the CD1283 will hold off the cycle until it is ready. In system designs that monitor DTACK\*, this is not a problem; the cycle is extended until DTACK\* becomes active, and the delay is automatically met. If a system design does not monitor DTACK\*, a mechanism must be provided to introduce the required delay.

Warning: Failure to observe the above delay requirement can cause device malfunction.

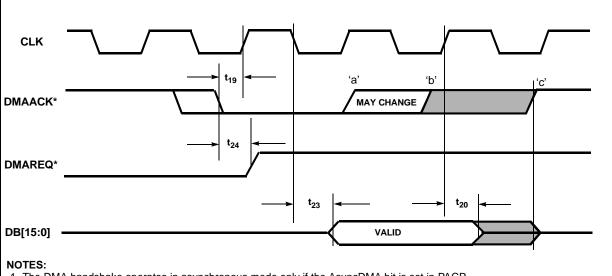

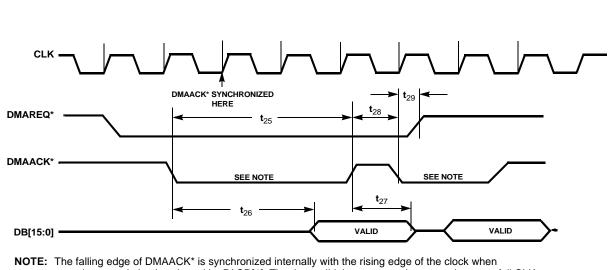

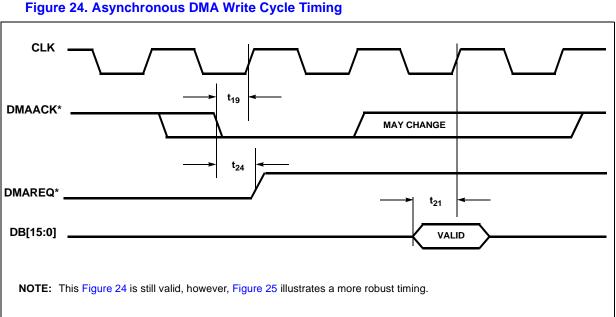

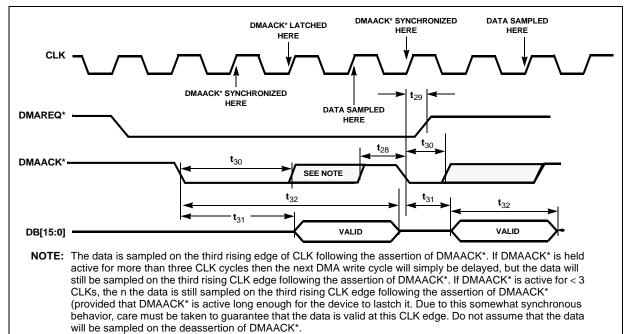

### 5.2.4 DMA Cycles

The CD1283 provides a bidirectional, 16-bit DMA interface to the parallel port. This is the only direct-data interface to the port; other 8-bit register accesses make use of the normal CPU interface, as previously described.

The handshake between the CD1283 and the DMA circuitry uses two signals: DMAREQ\* and DMAACK\*. The address bus is ignored during DMA transfers. When internal conditions warrant a DMA transfer (as when the FIFO falls below the programmed threshold in the forward direction or rises above the threshold in the reverse direction) and DMA transfers are enabled through the PFCR, the device requests DMA service by driving DMAREQ\* low. DMAREQ\* remains active until the FIFO has less than two empty byte locations remaining (forward direction) or until the

FIFO has less than 2 bytes remaining (reverse direction). In the forward direction, the DMA controller logic responds by placing data on the 16-bit data bus and driving the DMAACK\* input low. This cycle is repeated until the FIFO has less than two empty byte locations remaining or there is no more data to send. In the reverse direction, the CD1283 responds to the active DMAACK\* signal by driving the contents of the DMABUF register onto the data bus.

Odd-byte transfers in the reverse direction are handled on an interrupt basis. When the number of bytes in the FIFO is odd, all bytes except the last are transferred through a number of 16-bit DMA cycles (two bytes per cycle). The odd byte remaining is held in PFHR1 and an interrupt generated when the stale data timer expires. Status indicating that PFHR1 contains data is indicated in the PFSR. The CPU interrupt service routine must manually remove the remaining byte from the interface. In the forward direction, an odd remaining byte can be directly written to the PFHR1 once the last DMA cycle is complete.

One additional input signal determines the endian format (whether the least-significant byte is on data bits 7:0 or 15:8) of the 16-bit DMA buffer. BYTESWAP selects whether the lower or upper byte of the DMA buffer moves into the FIFO data pipeline first in the forward direction, or from the FIFO data pipeline to the DMA buffer first in the reverse direction. If BYTESWAP is low, then the least-significant byte (DB[7:0]) immediately moves into or out of the data pipeline. If BYTESWAP is high, the opposite occurs (DB[15:8] move into or out of the pipeline first).

The effective duration of the DMA transfer block (burst) is determined by the threshold value in the PFTR. Regardless of where the port is moving data when this threshold is reached (exceeded in receive; less than in transmit), a DMA cycle begins and remains active until the FIFO has less than 2 bytes remaining (receive) or has less than two empty byte locations remaining (transmit).

The SVRR provides can determine if a DMA cycle is being requested. SVRR[7] is true if a DMA cycle is currently being requested. This status indication is provided as a general system status.

Refer to Chapter 8.0 for detailed information on DMA cycle options and timing values.

## 5.2.5 Interrupts

The term interrupt is a generalized description of the method where the CD1283 gains the attention of the CPU. Interrupt is used interchangeably with 'service request' as the two are the same function. Interrupt often describes an unconditional response on the part of the CPU. Whether or not this is the case, the source is still the same — a service request from the CD1283. The hardware signal generated by the CD1283 (SVCREQP\*) can be connected to the CPU interrupt input to start an interrupt service routine. The service routine can then begin servicing the request from the CD1283 by starting an acknowledge sequence.

### 5.2.6 DMAREQ\* as Interrupt Source

Interrupts are not generated by FIFO threshold conditions; therefore, if the system design requires data to move through interrupts, connect DMAREQ\* directly to a CPU interrupt input or logically OR it into the same CPU interrupt input as SVCREQP\*. If DMAREQ\* is used to generate interrupts, the following are required:

- 1. A 16-bit data interface must be implemented to support 16-bit reads of the DMABUF register.

- 2. The DMA threshold value in the PFTR must be initialized.

- 3. The DMAREQ\* remains active until the FIFO is nearly empty (Rx) or nearly full (Tx), followed by the toggling of DMAen if data is moved to/from the FIFO through PIO (refer to

Section 5.2.4). However, the software can easily change this by clearing the DMAen bit (PFCR[6]) at the start of the interrupt service routine and setting it again at the end.

- 4. If SVCREQP\* and DMAREQ\* are logically OR'ed together, the service routine must start by checking the SVRR to determine which signal is active.

- 5. SVCACKP\* must not be activated in response to DMAREQ\*; likewise, DMAACK\* must not be activated in response to SVCREQ\*.

- 6. The DMAdir bit (PFCR[5]) can determine whether to write or read to/from the DMABUF register.

- 7. The PFQR can determine how many reads of the 16-bit DMABUF register are necessary to empty the pipeline. Note however, four must be added to the PFQR value, then that number then must be divided by two and truncated to the nearest integer (this accounts for the extra four bytes in the two holding registers and the 16-bit DMABUF register, as well as 16-bit instead of 8-bit reads).

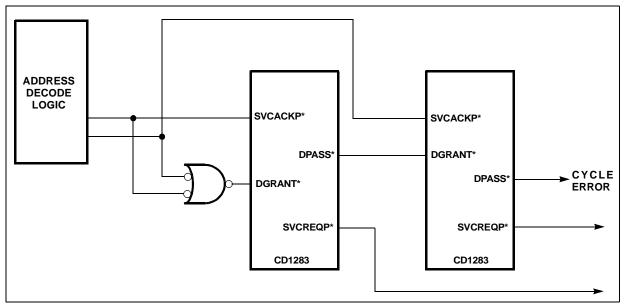

### 5.2.7 Daisy-Chain Configurations

Multiple CD1283s can be connected in a daisy-chain configuration, forming systems with multiple parallel ports. The device provides all signals necessary for this configuration, with only minimal external logic being (Figure 4).

When the CPU acknowledges the request, both CD1283s receive the acknowledge through SVCACK\*. However, only the device receives DGRANT\*. If it has an active request of this type pending, it takes the acknowledge and drives the vector register (RIVR, TIVR, MIVR) onto the data bus.

If the first device does not have a request pending, it passes DGRANT\* to the second CD1283 through DPASS\*. Assuming that the second CD1283 has an active request pending, it then takes the acknowledge and drives its vector register onto the data bus.

Figure 4. CD1283 Daisy-Chain Configuration