# **Intel<sup>®</sup> Wireless Flash Memory** (W18/W30 SCSP)

64WQ Family with Asynchronous RAM

### **Datasheet**

### **Product Features**

#### Device Architecture

- —Flash Density: 64-Mbit

- —Async PSRAM Density: 8-, 16-, 32-Mbit

- —Async SRAM Density: 4-, 8-, 16-Mbit

- —Top, Bottom or Dual flash parameter configuration

#### Device Voltage

- —Flash  $V_{CC} = 1.8 \text{ V } (90 \text{ nm or } 130 \text{ nm})$

- —Flash  $V_{CCO} = 1.8 \text{ V } (90 \text{ nm})$

- —Flash  $V_{CCQ} = 1.8 \text{ V or } 3.0 \text{ V (130 nm)}$ —RAM  $V_{CC} = 3.0 \text{ V}$

- --RAM  $V_{CCO} = 1.8 \text{ V or } 3.0 \text{ V}$

#### Device Packaging

- -88 balls (8 x 10 active ball matrix)

- —Area: 8x10 mm

- —Height: 1.2 mm to 1.4 mm

### PSRAM Performance

- -88 ns initial access, 30 ns async page reads at 1.8 V I/O

- —70 ns initial access, 25 ns async page reads at 1.8 V I/O

- -85 ns initial access, 35 ns async page reads at 3.0 V I/O

- -70 ns initial access, 25 ns async page reads at 3.0 V I/O

#### SRAM Performance

-70 ns initial access at 1.8 V or 3.0 V I/O

#### Flash Performance

- -65 ns initial access at 1.8 V I/O

- —70 ns initial access at 3.0 V I/O

- -25 ns async page at 1.8 V or 3.0 V I/O

- —14 ns sync reads (t<sub>CHOV</sub>) at 1.8 V I/O

- -20 ns sync reads (t<sub>CHOV</sub>) at 3.0 V I/O

- —Enhanced Factory Programming: 3.10 µs/Word (Typ)

#### ■ Flash Architecture

- -Read-While-Write/Erase

- —Asymmetrical blocking structure

- —4-KWord parameter blocks (Top or Bottom)

- -32-KWord main blocks

- —4-Mbit partition size

- -128-bit One-Time Programmable (OTP) **Protection Register**

- -Zero-latency block locking

- -Absolute write protection with block lock using F-VPP and F-WP#

#### Flash Software

- —Intel<sup>®</sup> Flash Data Integrator (FDI)

- —Common Flash Interface (CFI)

#### Quality and Reliability

- –Extended Temperature: −25 °C to +85 °C

- —Minimum 100K flash block erase cycle

- —90 nm ETOX<sup>TM</sup> IX flash technology

- —130 nm ETOX<sup>TM</sup> VIII flash technology

The Intel® Wireless Flash Memory (W18/W30 SCSP) family offers a variety of flash plus static RAM combinations in a common package footprint. The flash memory features 1.8 V low-power operations with flexible, multi-partition, dual-operation Read-While-Write / Read-While-Erase, asynchronous, and synchronous reads. This SCSP device integrates up to two flash die, one PSRAM die, and one SRAM die in a low-profile package compatible with other SCSP families with QUAD+ ballout.

Notice: This document contains information on products in the sampling and initial production phases of development. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

#### IMPORTANT - PLEASE READ BEFORE INSTALLING OR USING INTEL® PRE-RELEASE PRODUCTS

Please review the terms at <a href="http://www.intel.com/design/prerelease\_terms.htm">http://www.intel.com/design/prerelease\_terms.htm</a> carefully before using any Intel® pre-release product, including any evaluation, development or reference hardware and/or software product (collectively, "Pre-Release Product"). By using the Pre-Release Product, you indicate your acceptance of these terms, which constitute the agreement (the "Agreement") between you and Intel Corporation ("Intel"). In the event that you do not agree with any of these terms and conditions, do not use or install the Pre-Release Product and promptly return it unused to Intel.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>(R)</sup> WIRELESS FLASH MEMORY 64WQ FAMILY may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This Datasheet as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation

2 Datasheet

| 1.0  | Intro      | duction                                         | 7  |

|------|------------|-------------------------------------------------|----|

|      | 1.1        | Nomenclature                                    |    |

|      | 1.2        | Conventions                                     |    |

| 2.0  |            | ctional Overview                                |    |

|      | 2.1<br>2.2 | Block DiagramFlash Memory Map and Partitioning  |    |

| 3.0  | Pack       | age Information                                 |    |

| 4.0  | Ballo      | out and Signal Description                      | 14 |

|      | 4.1        | Signal Ballout                                  | 14 |

|      | 4.2        | Signal Descriptions                             |    |

| 5.0  | Maxi       | mum Ratings and Operating Conditions            | 17 |

|      | 5.1        | Absolute Maximum Ratings                        | 17 |

|      | 5.2        | Operating Conditions                            | 18 |

| 6.0  | Elect      | trical Specifications                           | 20 |

|      | 6.1        | DC Characteristics                              | 20 |

| 7.0  | AC C       | Characteristics                                 | 23 |

|      | 7.1        | Flash AC Characteristics                        |    |

|      | 7.2<br>7.3 | SRAM AC CharacteristicsPSRAM AC Characteristics |    |

|      | 7.3<br>7.4 | Device AC Test Conditions                       |    |

| 8.0  | Flash      | h Power Consumption                             | 31 |

| 9.0  | Devi       | ce Operation                                    | 31 |

|      | 9.1        | Bus Operations                                  | 31 |

|      | 9.2        | Flash Command Definitions                       | 35 |

| 10.0 | Flash      | h Read Operations                               | 35 |

| 11.0 | Flash      | h Program Operations                            | 35 |

| 12.0 | Flash      | h Erase Operations                              | 35 |

| 13.0 | Flash      | h Security Modes                                | 35 |

| 14.0 | Flash      | h Read Configuration Register                   | 35 |

| 15.0 | SRA        | M Operations                                    | 36 |

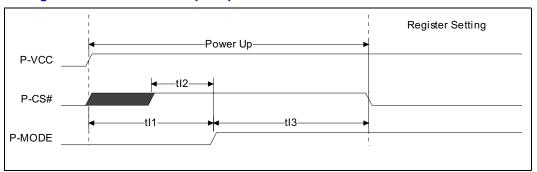

|      | 15.1       | Power-up Sequence and Initialization            |    |

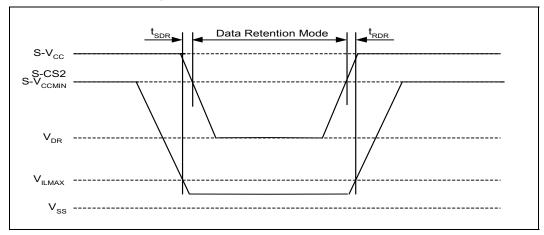

|      | 15.2       | Data Retention Mode                             |    |

| 16.0 |            | AM Operations                                   |    |

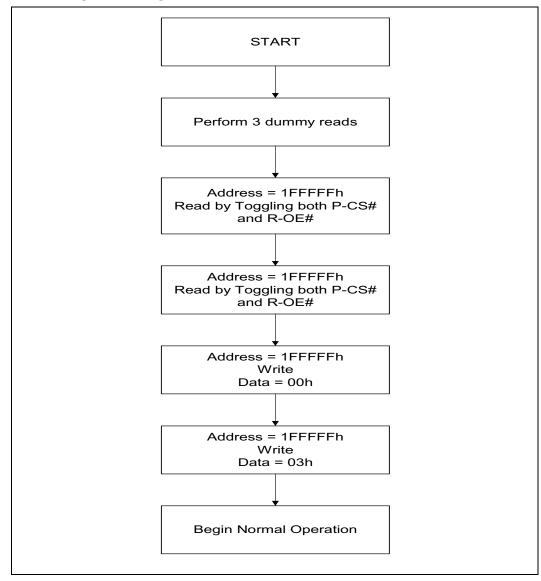

|      | 16.1       | Power-Up Sequence and Initialization            |    |

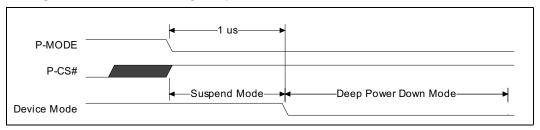

|      | 10.2       | Standby Mode/ Deep Fower-Down Mode              | 40 |

### Contents

|       | 16.3   | PSRAM Special Read and Write Constraints | 41 |

|-------|--------|------------------------------------------|----|

| Appei | ndix A | Write State Machine                      | 42 |

| Appei | ndix B | Common Flash Interface                   | 42 |

| Appei | ndix C | Flash Flowcharts                         | 42 |

| Appei | ndix D | Additional Information                   | 42 |

| Appei | ndix E | Ordering Information                     | 43 |

# Revision History

| Date              | Revision | Description                                                                                                                                                                                      |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2003         | -001     | Initial release.                                                                                                                                                                                 |

| September<br>2003 | -002     | Changed PSRAM Read values. Added new Transient Equivalent Testing Load Circuit figure. General text edits.                                                                                       |

| May 2004          | -006     | Reformatted the datasheet and moved sections around according to the new layout.                                                                                                                 |

| August 2004       | -007     | Added 90 nm product information.  Added line items to Table 24 "64WQ W18/W30 SCSP Ordering Information" on page 45.  Added DC and AC specs for the new line items and edits to related sections. |

Datasheet 5

### Contents

6 Datasheet

### 1.0 Introduction

This document contains information pertaining to the products in the Intel  $^{\circledR}$  Wireless Flash Memory (W18/W30 SCSP) family with asynchronous RAM. This W18/W30 SCSP 64WQ family offers a wide variety of stacked combinations that include single flash die, two flash die, flash + PSRAM, and flash + SRAM options. This document provides information where this SCSP family differs from the Intel  $^{\circledR}$  Wireless Flash Memory (W18/W30) discrete device.

Refer to the discrete datasheets *Intel*® *Wireless Flash Memory (W18) Datasheet* (order number 290701) and *Intel*® *Wireless Flash Memory (W30) Datasheet* (order number 290702) for flash product details not included in this SCSP datasheet.

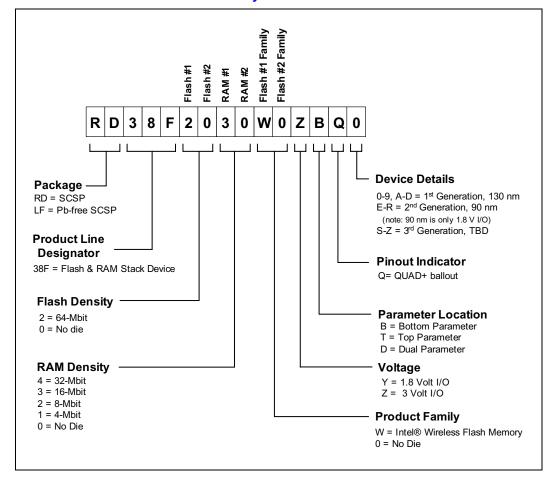

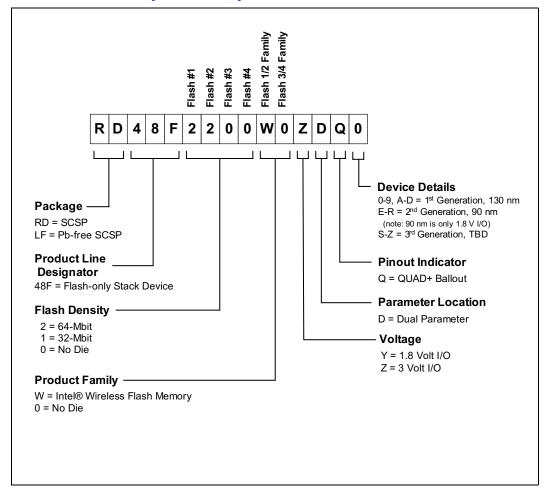

### 1.1 Nomenclature

0x Hexadecimal prefix 0b Binary prefix

Byte 8 bits

CFI Common Flash Interface CUI Command User Interface

DU Don't Use

ETOX EPROM Tunnel Oxide

FDI Flash Data Integrator (Intel® software solution)

k (noun) 1 thousand

Kb 1024 bits

KB 1024 bytes

Kword 1024 words

M (noun) 1 million

Mb 1,048,576 bits

MB 1,048,576 bytes

OTP One-Time Programmable

PLR Protection Lock Register

PR Protection Register

PRD Protection Register Data

RCR Read Configuration Register

RFU Reserved for Future Use

SCSP Stacked Chip Scale Package

SR Status Register SRD Status Register Data

Word 16 bits

WSM Write State Machine

### 1.2 Conventions

- **Group Membership Brackets:** Square brackets are used to designate group membership or to define a group of signals with a similar function, such as A[21:1] and SR[4,1].

- **VCC vs.**  $V_{CC}$ : When referring to a signal or package-connection name, the notation used is VCC, etc. When referring to a timing or electrical level, the notation used is subscripted such as  $V_{CC}$ , etc.

- **Device:** This term is used interchangeably throughout this document to denote either a particular die, or the combination of multiple die within a single package.

- **F[3:1]-CE#**, **F[2:1]-OE#**: This is the method used to refer to more than one chip-enable or output enable at the same time. When each is referred to individually, the reference will be F1-CE# and F1-OE# (for die #1), and F2-CE# and F2-OE# (for die #2).

- **F-VCC**, **P-VCC** or **S-VCC**: When referencing flash memory signals or timings, the notation used is F-VCC or F-V<sub>CC</sub>, respectively. When the reference is to PSRAM signals or timings, the notation is prefixed with "P-" (e.g., P-VCC, P-V<sub>CC</sub>). When referencing SRAM signals or timings, the notation is prefixed with "S-" (e.g., S-VCC or S-V<sub>CC</sub>). P-VCC and S-VCC are RFU for stacked combinations that do not include PSRAM or SRAM.

- **R-OE#, R-LB#, R-UB#, R-WE#:** These are used to identify RAM OE#, LB#, UB#, WE# signals, and are usually shared between 2 or more RAM die. R-OE#, R-LB#, R-UB# and R-WE are RFU for stacked combinations that do not include PSRAM or SRAM.

# 2.0 Functional Overview

This section provides an overview of the features and capabilities of the Intel® Wireless Flash Memory (W18/W30 SCSP) family with asynchronous RAM device.

The W18/W30 SCSP device provides flash + RAM die combinations. Products range from single flash die, two flash die, flash + PSRAM, or flash + SRAM. You can choose a W18 SCSP device or a W30 SCSP device with SRAM or PSRAM offered with the same package footprint and signal ballout.

Table 24, "64WQ W18/W30 SCSP Ordering Information" on page 45 lists possible product combinations for the 64-Mbit W18/W30 SCSP family.

### 2.1 Block Diagram

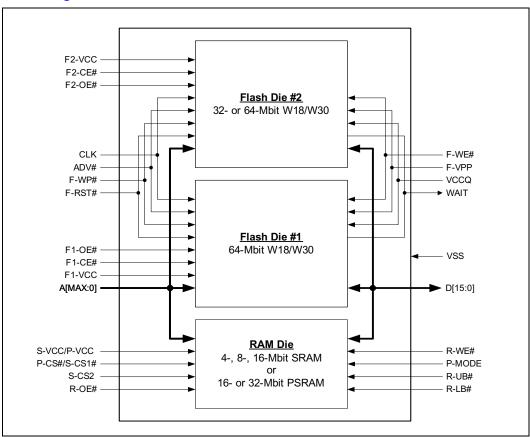

Figure 1 shows all internal package connections for the SCSP family with multiple die. See Table 24 for valid combinations of flash and RAM die. Unused connections on combinations with less than three die are reserved and should not be used.

Please contact your local Intel representative for details regarding any reserved or RFU pins.

Figure 1. Block Diagram

# 2.2 Flash Memory Map and Partitioning

Consult the latest *Intel*® *Wireless Flash Memory (W18) Datasheet* (order number 290701) and the *Intel*® *Wireless Flash Memory (W30) Datasheet* (order number 290702), for individual flash die memory map and partitioning information.

Table 1 and Table 2 show memory map and partitioning information for dual-flash memory die configurations. Flash Die #1 (with F1-CE# as its Chip Select) is configured as a bottom boot while Flash Die #2 (with F2-CE# as its Chip Select) is configured as top boot.

Table 1. 64-Mbit Flash + 32-Mbit Flash Die W18/W30 SCSP Memory Map and Partitioning

|                           | Partitioning       |                 | Block Size<br>(KW) | Block # | Address Range |

|---------------------------|--------------------|-----------------|--------------------|---------|---------------|

|                           |                    |                 |                    |         |               |

|                           | Parameter          | Partition 0     | 4                  | 63-70   | 1F8000-1FFFFF |

|                           | Partition          | 1 artition o    | 32                 | 56-62   | 1C0000-1F7FFF |

| Flash Die #2              |                    | Partition 1     | 32                 | 48-55   | 180000-1BFFFF |

| (32-Mbit)                 | Main               | Partition 2     | 32                 | 40-47   | 140000-17FFFF |

|                           | Partitions         | Partition 3     | 32                 | 32-39   | 100000-13FFFF |

|                           |                    | Partitions 4-7  | 32                 | 0-31    | 000000-0FFFF  |

|                           |                    |                 |                    |         |               |

|                           |                    | Partitions 8-15 | 32                 | 71-134  | 200000-3FFFF  |

|                           |                    | Partitions 4-7  | 32                 | 39-70   | 100000-1FFFFF |

|                           | Main<br>Partitions | Partition 3     | 32                 | 31-38   | 0C0000-0FFFFF |

| Flash Die #1<br>(64-Mbit) |                    | Partition 2     | 32                 | 23-30   | 080000-0BFFFF |

| ( )                       |                    | Partition 1     | 32                 | 15-22   | 040000-07FFFF |

|                           | Parameter          | Partition 0     | 32                 | 8-14    | 008000-03FFFF |

|                           | Partition          | i aitition o    | 4                  | 0-7     | 000000-007FFF |

# Table 2. 64-Mbit Dual-Flash Die W18/W30 SCSP Memory Map and Partitioning

|                     | Partitioning       |                 | Block Size<br>(KW) | Block # | Address Range |

|---------------------|--------------------|-----------------|--------------------|---------|---------------|

|                     |                    |                 |                    |         |               |

|                     | Parameter          | Partition 0     | 4                  | 127-134 | 3F8000-3FFFFF |

|                     | Partition          | Faithorio       | 32                 | 120-126 | 3C0000-3F7FFF |

| _                   |                    | Partition 1     | 32                 | 112-119 | 380000-3BFFFF |

| Top<br>Parameter    |                    | Partition 2     | 32                 | 104-111 | 340000-37FFFF |

|                     | Main<br>Partitions | Partition 3     | 32                 | 96-103  | 300000-33FFFF |

|                     |                    | Partitions 4-7  | 32                 | 64-95   | 200000-2FFFFF |

|                     |                    | Partitions 8-15 | 32                 | 0-63    | 000000-1FFFFF |

|                     |                    |                 |                    |         |               |

|                     |                    | Partitions 8-15 | 32                 | 71-134  | 200000-3FFFFF |

|                     |                    | Partitions 4-7  | 32                 | 39-70   | 100000-1FFFFF |

|                     | Main<br>Partitions | Partition 3     | 32                 | 31-38   | 0C0000-0FFFF  |

| Bottom<br>Parameter |                    | Partition 2     | 32                 | 23-30   | 080000-0BFFFF |

|                     |                    | Partition 1     | 32                 | 15-22   | 040000-07FFFF |

|                     | Parameter          | Partition 0     | 32                 | 8-14    | 008000-03FFFF |

|                     | Partition          | Partition U     | 4                  | 0-7     | 000000-007FFF |

# 3.0 Package Information

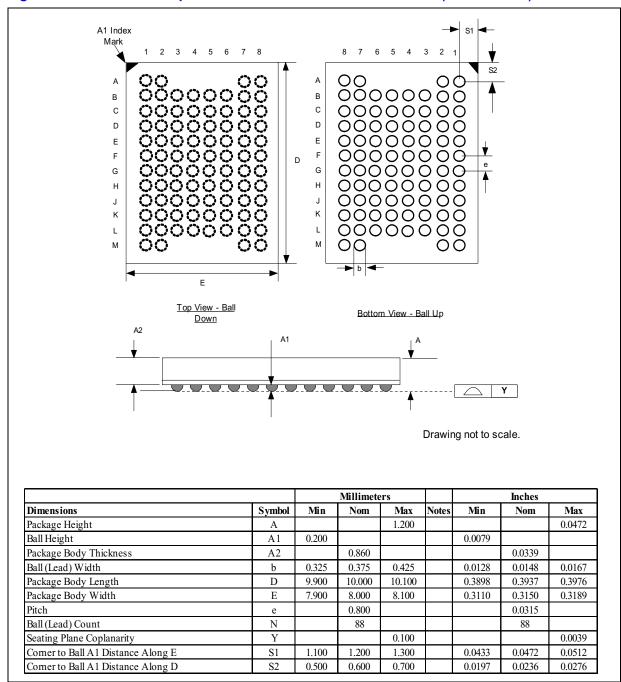

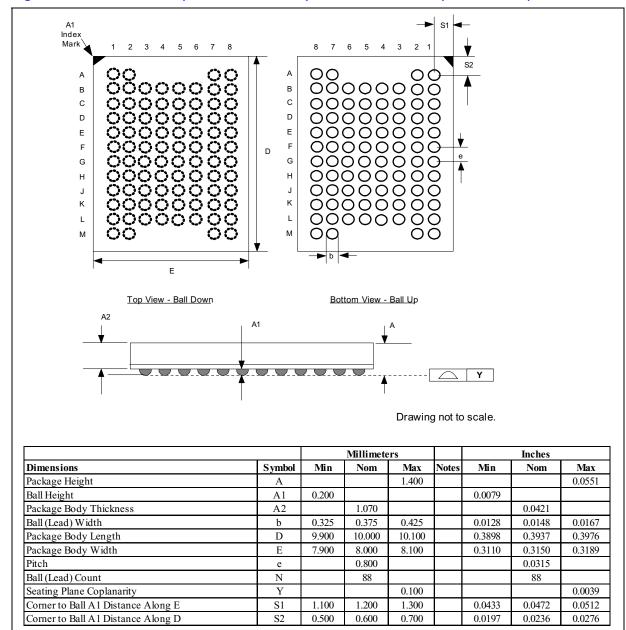

The following packages are offered with the 64WQ Family:

- Figure 2, "Mechanical Specifications for 1- or 2-Die SCSP Device (8x10x1.2 mm)"

- Figure 3, "Mechanical Specifications for Triple-Die SCSP Device (8x10x1.4 mm)"

Figure 2. Mechanical Specifications for 1- or 2-Die SCSP Device (8x10x1.2 mm)

Figure 3. Mechanical Specifications for Triple-Die SCSP Device (8x10x1.4 mm)

# 4.0 Ballout and Signal Description

# 4.1 Signal Ballout

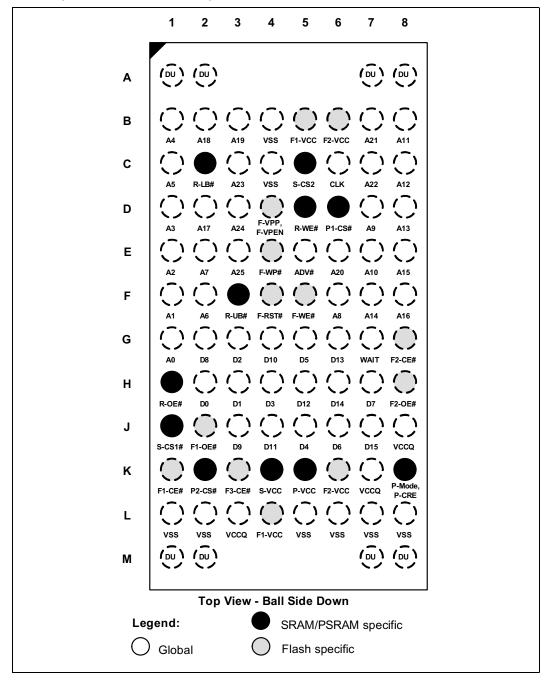

Figure 4 shows the 64WQ W18/W30 SCSP family 88-ball (8x10 active ball matrix) device.

Figure 4. 88-Ball (8x10 Active Ball Matrix) QUAD+ Ballout

# 4.2 Signal Descriptions

Table 3 describes active signals used on the 64WQ W18/W30 SCSP family.

Table 3. Signal Descriptions (Sheet 1 of 2)

| Symbol          | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[21:0]         | Input            | ADDRESS INPUTS: Inputs for all die addresses during read and write operations. Addresses are internally latched during write operations.  • 4-Mbit: A[17:0]  • 8-Mbit: A[18:0]  • 16-Mbit: A[19:0]  • 32-Mbit: A[20:0]  • 64-Mbit: A[21:0]  A0 is the lowest-order word address.  A[25:22] denote high-order addresses reserved for future device densities                                                                                                                                                                                   |

| D[15:0]         | Input/<br>Output | <b>DATA INPUTS/OUTPUTS:</b> Inputs data and commands during write cycles; outputs data during read cycles. Data signals float when the device or its outputs are deselected. Data are internally latched during writes.                                                                                                                                                                                                                                                                                                                       |

| CLK             | Input            | FLASH CLOCK: CLK synchronizes the selected flash die to the memory bus frequency in synchronous-read mode. During synchronous read operations, the initial address is latched on the rising edge of ADV#, or the rising/ falling edge of CLK when ADV# is low, whichever occurs first. CLK is only used in synchronous-read mode. Refer to the flash discrete product datasheet for information on how to use this signal in asynchronous-read mode.                                                                                          |

| ADV#            | Input            | FLASH ADDRESS VALID: Low-true; During synchronous read operations, the initial address is latched on the rising edge of ADV#, or the rising/ falling edge of CLK when ADV# is low, whichever occurs first.  Refer to the flash discrete product datasheet for information on how to use this signal in asynchronous-read mode.                                                                                                                                                                                                                |

| WAIT            | Output           | <b>FLASH WAIT:</b> When asserted, WAIT indicates invalid data from the selected flash die on D[15:0]. WAIT is High-Z whenever the flash die is deselected (CE# = V <sub>IL</sub> ). WAIT is not gated by OE#. WAIT is only used in synchronous array-read mode. Refer to the flash discrete product datasheet for information on how to use this signal in asynchronous-read mode.                                                                                                                                                            |

| F[3:1]-CE#      | Input            | FLASH CHIP ENABLE: Low-true; CE#-low selects the associated flash memory die. When asserted, flash internal control logic, input buffers, decoders, and sense amplifiers are active. When deasserted, the associated flash die is deselected; power is reduced to standby levels, data and WAIT outputs are placed in High-Z.  F1-CE# selects flash die #1; F2-CE# selects flash die #2 and is RFU on combinations with only one flash die. F3-CE# selects flash die #3 and is RFU on SCSP combinations with only one or two flash die.       |

| S-CS1#<br>S-CS2 | Input            | <b>SRAM CHIP SELECTS:</b> When both SRAM chip selects are asserted, SRAM internal control logic, input buffers, decoders, and sense amplifiers are active. When either/both SRAM chip selects are deasserted (S-CS1# = $V_{IH}$ and/or S-CS2 = $V_{IL}$ ), the SRAM is deselected and its power is reduced to standby levels.  S-CS1# and S-CS2 are only available on SCSP combinations with SRAM die.                                                                                                                                        |

| P[2:1]-CS#      | Input            | PSRAM CHIP SELECTS: Low-true; When asserted, PSRAM internal control logic, input buffers, decoders, and sense amplifiers are active. When deasserted, the PSRAM is deselected and its power is reduced to standby levels.  P1-CS# selects PSRAM die #1 and is available only on SCSP combinations with PSRAM die. This ball is RFU on SCSP combinations without PSRAM. P2-CS# selects PSRAM die #2 and is available only on SCSP combinations with two PSRAM die. This ball is RFU on SCSP combinations without PSRAM or with a single PSRAM. |

Table 3. Signal Descriptions (Sheet 2 of 2)

| Symbol          | Type  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |       | <b>FLASH OUTPUT ENABLE:</b> Low-true; OE#-low enables the flash output buffers. OE#-high disables the flash output buffers, and places the flash outputs in High-Z.                                                                                                                                                                                                                                                                              |

| F[2:1]-OE#      | Input | F1-OE# controls the outputs of flash die #1; F2-OE# controls the outputs of flash die #2 and #3, and is available only on SCSP combinations with two or three flash die and is RFU on SCSP combinations with only one flash die.                                                                                                                                                                                                                 |

| R-OE#           | Input | RAM OUTPUT ENABLE: Low-true; R-OE#-low enables the RAM output buffers. R-OE#-high disables the RAM output buffers, and places the RAM outputs in High-Z.  R-OE# is only available on SCSP combinations with RAM die.                                                                                                                                                                                                                             |

| R-UB#<br>R-LB#  | Input | RAM UPPER/ LOWER BYTE ENABLES: Low-true; During RAM reads, R-UB#-low enables the RAM high-order bytes on D[15:8], and R-LB#-low enables the RAM low-order bytes on D[7:0].  R-UB# and R-LB# are only available on SCSP combinations with either SRAM die or PSRAM die.                                                                                                                                                                           |

| F-WE#           | Input | <b>FLASH WRITE ENABLE:</b> Low-true; WE# controls writes to the selected flash die. Address and data are latched on the rising edge of WE#.                                                                                                                                                                                                                                                                                                      |

| R-WE#           | Input | RAM WRITE ENABLE: Low-true; R-WE# controls writes to the RAM die. R-WE# is only available on SCSP combinations with RAM die.                                                                                                                                                                                                                                                                                                                     |

| F-WP#           | Input | FLASH WRITE PROTECT: Low-true; WP# enables/disables the lock-down protection mechanism of the flash die. WP#-low enables the lock-down mechanism- locked down blocks cannot be unlocked with software commands. WP#-high disables the lock-down mechanism, allowing locked down blocks to be unlocked with software commands.                                                                                                                    |

| F-RST#          | Input | <b>FLASH RESET:</b> Low-true; RST#-low initializes flash internal circuitry and disables flash operations. RST#-high enables flash operation. Exit from reset places the flash in asynchronous read array mode.                                                                                                                                                                                                                                  |

| F-VPP<br>F-VPEN | Power | <b>FLASH PROGRAM/ ERASE POWER:</b> A valid F-V <sub>PP</sub> voltage on this ball enables flash program/erase operations. Flash memory array contents cannot be altered when F-V <sub>PP</sub> (V <sub>PEN</sub> ) < V <sub>PPLK</sub> (V <sub>PENLK</sub> ). Erase/ program operations at invalid F-V <sub>PP</sub> (V <sub>PEN</sub> ) voltages should not be attempted. Refer to the flash discrete product datasheet for additional details. |

|                 |       | F-V <sub>PEN</sub> (Erase/Program/Block Lock Enables) is not available for W18/W30 products.                                                                                                                                                                                                                                                                                                                                                     |

| P-MODE          | Input | PSRAM MODE: Low-true; P-MODE is used to enter/exit low power mode.  Low power mode is not applicable to 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0ZBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.                                                                                                                                                                                                                                                |

|                 |       | P-Mode is only available on SCSP combinations with PSRAM die.                                                                                                                                                                                                                                                                                                                                                                                    |

| F[2:1]-VCC      | Power | <b>FLASH LOGIC Power:</b> F1-VCC supplies power to the core logic of flash die #1; F2-VCC supplies power to the core logic of flash die #2 and #3. Write operations are inhibited when F-V <sub>CC</sub> < V <sub>LKO</sub> . Device operations at invalid F-V <sub>CC</sub> voltages should not be attempted.                                                                                                                                   |

|                 |       | F2-VCC is only available on SCSP combinations with two or three flash die, and is RFU on SCSP combinations with only one flash die.                                                                                                                                                                                                                                                                                                              |

| S-VCC           | Power | SRAM Power Supply: Supplies power to the SRAM die. S-VCC is only available on SCSP combinations with SRAM die.                                                                                                                                                                                                                                                                                                                                   |

| P-VCC           | Power | PSRAM Power Supply: Supplies power to the PSRAM die. P-VCC is only available on SCSP combinations with PSRAM die.                                                                                                                                                                                                                                                                                                                                |

| VCCQ            | Power | FLASH OUTPUT-BUFFER Power: Supplies power for the I/O output buffers.                                                                                                                                                                                                                                                                                                                                                                            |

| VSS             | Power | Ground: Connect to ground. Do not float any VSS connection.                                                                                                                                                                                                                                                                                                                                                                                      |

| RFU             | _     | Reserved for Future Use: Reserve for future device functionality/ enhancements.                                                                                                                                                                                                                                                                                                                                                                  |

| DU              | _     | Do Not Use: Do not connect to any other signal, or power supply; must be left floating.                                                                                                                                                                                                                                                                                                                                                          |

# 5.0 Maximum Ratings and Operating Conditions

### 5.1 Absolute Maximum Ratings

Warning:

Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only.

NOTICE: This document contains information available at the time of its release. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

### Table 4. Absolute Maximum Ratings

| Parameter                                                                     | Parameter           |       | Max   | Unit    | Notes |

|-------------------------------------------------------------------------------|---------------------|-------|-------|---------|-------|

| Temperature under Bias Expanded                                               |                     | -25   | +85   | °C      | 7     |

| Storage Temperature                                                           | Storage Temperature |       |       | °C      |       |

| Voltage On Any Signal (except F[2:1]-V <sub>CC</sub> ,                        | 1.8 V I/O           | -0.2  | +2.45 | V       | 1,2,3 |

| V <sub>CCQ,</sub> F-V <sub>PP,</sub> S-V <sub>CC</sub> and P-V <sub>CC)</sub> | 3.0 V I/O           | -0.2  | +3.6  | V       | 1,2,3 |

| F[2:1]-V <sub>CC</sub> Voltage                                                |                     | -0.5  | +2.45 | V       | 2,3   |

| V <sub>CCO</sub> , S-V <sub>CC</sub> and P-V <sub>CC</sub> Voltage            | 1.8 V I/O           | -0.2  | +2.45 | V       | 1,2,3 |

| VCCQ, 3-VCC and 1-VCC voltage                                                 | 3.0 V I/O           | -0.2  | +3.6  | V       | 1,2,3 |

| F-V <sub>PP</sub> Voltage                                                     | -0.2                | +14.0 | V     | 2,3,4,5 |       |

| I <sub>SH</sub> Output Short Circuit Current                                  |                     | _     | 100   | mA      | 6     |

- 1. 90 nm is only avail with the 1.8 V I/O.

- All Specified voltages are relative to V<sub>SS</sub>. Minimum DC voltage is -0.2 V on input/output signals, -0.2 V on F[2:1]-VCC and F-VPP signals. For 90 nm devices, during transitions, this level may overshoot to -1.5 V for periods < 20 ns, during transitions, may overshoot to F-V<sub>CC</sub> + 1.5 V for periods < 20 ns.</li>

- All Specified voltages are relative to V<sub>SS</sub>. Minimum DC voltage is -0.2 V on input/output signals, 0.2 V on F[2:1]-VCC and F-VPP signals. For 130 nm devices, during transitions, this level may

overshoot to -2 V for periods < 20 ns, during transitions, may overshoot to F-V<sub>CC</sub> + 2 V for periods <

20 ns</li>

- 4. Maximum DC voltage on F-VPP may overshoot to +14.0 V for periods < 20 ns.

- 5. F-V<sub>PP</sub> program voltage is normally V<sub>PP1</sub>. The maximum DC voltage on F-V<sub>PP</sub> may overshoot to +14 V for periods < 20 ns. F-V<sub>PP</sub> can be V<sub>PP2</sub> for 1000 erase cycles on main blocks, 2500 cycles on parameter blocks.

- 6. Output shorted for no more than one second. No more than one output shorted at a time.

- 7. Devices available with -30 C temperature specifications are: 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0YBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.

# **5.2** Operating Conditions

Warning:

Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### Table 5. Operating Conditions

| Symbol                                 | Parameter                                             |           | Flash + Flash + SRAM |      | Flash +<br>PSRAM |      | Unit | Notes |    |   |

|----------------------------------------|-------------------------------------------------------|-----------|----------------------|------|------------------|------|------|-------|----|---|

|                                        |                                                       |           | Min                  | Max  | Min              | Max  | Min  | Max   |    |   |

| T <sub>C</sub>                         | Operating Temperature  Flash Supply Voltage           |           | -25                  | +85  | -25              | +85  | -25  | +85   | °C | 2 |

| F-V <sub>CC</sub>                      |                                                       |           | 1.7                  | 1.95 | 1.7              | 1.95 | 1.7  | 1.95  | V  |   |

| V <sub>CCQ</sub>                       | Flash I/O Voltage<br>PSRAM and SRAM<br>Supply Voltage | 3.0 V I/O | 2.2                  | 3.3  | 2.2              | 3.3  | 2.7  | 3.1   | V  |   |

| S-V <sub>CC</sub><br>P-V <sub>CC</sub> |                                                       | 1.8 V I/O | 1.7                  | 1.95 | 1.7              | 1.95 | 1.8  | 1.95  | >  |   |

| V <sub>PP1</sub>                       | Flash Program Logic Level                             |           | 0.9                  | 1.95 | 0.9              | 1.95 | 0.9  | 1.95  | V  |   |

| V <sub>PP2</sub>                       | Flash Factory Program                                 | /oltage   | 11.4                 | 12.6 | 11.4             | 12.6 | 11.4 | 12.6  | V  | 1 |

F-V<sub>PP</sub> is normally V<sub>PP1</sub>. F-VPP can be connected to 11.4 V-12.6 V for 1000 cycles on main blocks for extended temperatures and 2500 cycles on parameter blocks at extended temperature.

Devices available with -30 C temperature specifications are: 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0YBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.

# Capacitance

NOTICE: Refer to the 1.8-Volt Intel® Wireless Flash Memory Datasheet (order number 290701) and 1.8-Volt Intel® Wireless Flash Memory with 3 Volt II0 Datasheet (order number 290702) for flash capacitance details. For SCSP products with two flash die, flash capacitances for each of the flash die need to be considered accordingly.

### Table 6. SRAM, PSRAM Capacitance

| S | ymbol            | Parameter          | Тур | Unit | Condition                                                    |

|---|------------------|--------------------|-----|------|--------------------------------------------------------------|

|   | CIN              | Input Capacitance  | 10  | pF   | $V_{IN} = 0.0 \text{ V}, T_c=25 \text{ °C}, f=1 \text{ MHz}$ |

|   | C <sub>OUT</sub> | Output Capacitance | 10  | pF   | V <sub>OUT</sub> = 0.0 V, T <sub>c</sub> =25 °C, f=1 MHz     |

# 6.0 Electrical Specifications

### 6.1 DC Characteristics

SRAM and PSRAM DC characteristics are shown in Table 7, Table 8 and Table 9. Refer to the *Intel*<sup>®</sup> *Wireless Flash Memory (W18) Datasheet* (order number 290701) and the *Intel*<sup>®</sup> *Wireless Flash Memory (W30) Datasheet* (order number 290702) for flash DC characteristics.

NOTICE: DC Characteristics of all die in a SCSP device need to be considered accordingly, depending on the SCSP device operation.

Table 7. SRAM DC Characteristics (Sheet 1 of 2)

| D                 | Description Test Conditions                |                                                                                      | 1.8 V SRAM |                             | 3.0 V SRAM                 |                         |                            |      |

|-------------------|--------------------------------------------|--------------------------------------------------------------------------------------|------------|-----------------------------|----------------------------|-------------------------|----------------------------|------|

| Parameter         | Description                                | lest Conditions                                                                      |            | Min                         | Max                        | Min                     | Max                        | Unit |

| S-V <sub>CC</sub> | Voltage Range                              |                                                                                      |            | 1.7                         | 1.95                       | 2.2                     | 3.3                        | V    |

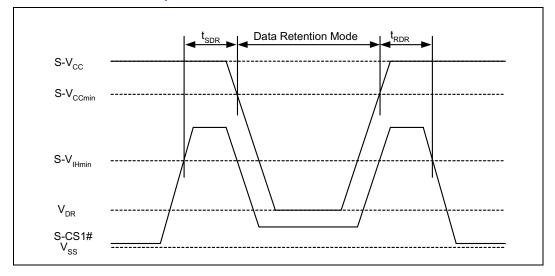

| $V_{DR}$          | V <sub>CC</sub> for Data Retention         |                                                                                      |            | 1.0                         | -                          | 1.5                     | _                          | V    |

|                   |                                            |                                                                                      | 4M         | _                           | 25                         | _                       | 45                         |      |

| $I_{CC}$          | Operating Current at min cycle time        | $I_{IO} = 0 \text{ mA}$                                                              | 8M         | _                           | 35                         | _                       | 50                         | mA   |

|                   | eyele ue                                   |                                                                                      | 16M        | _                           | 40                         | _                       | 55                         |      |

| I <sub>CC2</sub>  |                                            |                                                                                      | 4M         | _                           | 4                          | _                       | 10                         |      |

|                   | Operating Current at max cycle time (1 μs) | I <sub>IO</sub> = 0 mA                                                               | 8M         | _                           | 6                          | _                       | 10                         | mA   |

|                   |                                            |                                                                                      | 16M        | _                           | 10                         | _                       | 15                         | 1    |

|                   | Standby Current                            | S-CS1# ≥ S-V <sub>CC</sub> -0.2V                                                     | 4M         | _                           | 12                         | _                       | 15                         | μΑ   |

| $I_{SB}$          |                                            | or S-CS2 $\leq$ V <sub>SS</sub> +0.2V                                                | 8M         | _                           | 20                         | _                       | 25                         |      |

|                   |                                            | Address/Data toggling at minimum cycle time                                          | 16M        | -                           | 30                         | _                       | 45                         |      |

|                   | Current in Data                            | 1.8 V SRAM:<br>S-V <sub>CC</sub> = 1.0 V<br>3.0 V SRAM:<br>S-V <sub>CC</sub> = 1.5 V | 4M         | _                           | 6                          | _                       | 5                          |      |

| $I_{DR}$          |                                            |                                                                                      | 8M         | _                           | 10                         | _                       | 12                         | μΑ   |

| DIX               | Retention mode                             |                                                                                      | 16M        | _                           | 18                         | -                       | 15                         |      |

| V <sub>OH</sub>   | Output HIGH Voltage                        | I <sub>OH</sub> = -100 μA                                                            | l          | S-V <sub>CC</sub> -<br>0.15 | _                          | S-V <sub>CC</sub> - 0.1 | _                          | V    |

| V <sub>OL</sub>   | Output LOW Voltage                         | I <sub>OL</sub> = 100 μA,<br>V <sub>CCMIN</sub>                                      |            | -0.1                        | 0.2                        | -0.1                    | 0.1                        | ٧    |

| V <sub>IH</sub>   | Input HIGH Voltage                         |                                                                                      |            | S-V <sub>CC</sub> -<br>0.4  | S-V <sub>CC</sub> +<br>0.2 | S-V <sub>CC</sub> - 0.4 | S-V <sub>CC</sub> +<br>0.2 | ٧    |

| V <sub>IL</sub>   | Input LOW Voltage                          |                                                                                      |            | -0.2                        | 0.4                        | -0.2                    | 0.6                        | V    |

| I <sub>OH</sub>   | Output HIGH Current                        |                                                                                      |            | _                           | -                          | _                       | _                          | m/   |

| I <sub>OL</sub>   | Output LOW Current                         |                                                                                      |            | _                           | -                          | _                       | _                          | m/   |

Table 7. **SRAM DC Characteristics (Sheet 2 of 2)**

| *I <sub>IL</sub>  | Input Leakage Current                        | -0.2 < V <sub>IN</sub> < S-V <sub>CC</sub> +0.2 V       | -1 | +1 | -1 | +1 | μΑ |

|-------------------|----------------------------------------------|---------------------------------------------------------|----|----|----|----|----|

| *I <sub>LDR</sub> | Input Leakage Current in Data Retention Mode | $-0.2 < V_{IN} < S-V_{CC}+0.2 V$<br>$S-V_{CC} = V_{DR}$ | -1 | +1 | -1 | +1 | μА |

<sup>\*</sup> Input leakage currents include Hi-Z output leakage for bi-directional buffers with tri-state outputs.

#### PSRAM DC Characteristics<sup>(3)</sup> Table 8.

| Davamatar        | Description                         | Test Conditio                                        |     | 1.8 V I              | PSRAM                  | 3.0 V F                 | PSRAM                      | I I m i 4  | Note    |

|------------------|-------------------------------------|------------------------------------------------------|-----|----------------------|------------------------|-------------------------|----------------------------|------------|---------|

| Parameter        | Description                         | rest Conditio                                        | ns  | Min                  | Max                    | Min                     | Max                        | Unit       | Note    |

| V <sub>CC</sub>  | Voltage Range                       |                                                      |     | 1.8                  | 1.95                   | 2.7                     | 3.1                        | V          | 3       |

| Icc              | Operating Current                   | I <sub>IO</sub> = 0 mA                               | 16M | _                    | -                      | _                       | 35                         | mA         | 2, 3    |

|                  | at min cycle time                   | 10 0                                                 | 32M | -                    | 35                     | -                       | 45                         |            | _, 0    |

|                  | Operating Current at max cycle time | I <sub>IO</sub> = 0 mA                               | 16M | -                    | _                      | -                       | 7                          | mA         | 2, 3    |

| I <sub>CC2</sub> | (1 μs)                              | 10 - 0 1114                                          | 32M | _                    | _                      | _                       | 7                          | IIIA       | 2, 3    |

|                  |                                     | P-CS# ≥ P-V <sub>CC</sub> -<br>0.2V or               | 16M | _                    | _                      | -                       | 85                         |            |         |

| I <sub>SB</sub>  | Standby Current                     | P-Mode ≥ P-V <sub>CC</sub> -<br>0.2V                 |     |                      |                        |                         |                            | μА         | 2, 3    |

| -36              |                                     | Address/Data<br>toggling at<br>minimum cycle<br>time | 32M | -                    | 100                    | -                       | 100                        | <b>F</b> 1 | _, _    |

| I <sub>sbd</sub> | Deep Power-Down                     | P-Mode ≤ 0.2 V                                       | 16M | -                    | _                      | 1                       | 10                         | μА         | 2, 3    |

| 'SDQ             | Beep I ower Bown                    | 1 Wode = 0.2 V                                       | 32M | -                    | 30                     | 1                       | 10                         | μπ         | 2,0     |

| V <sub>OH</sub>  | Output HIGH<br>Voltage              | I <sub>OH</sub> = -0.5 m/                            | 4   | 0.8P-V <sub>CC</sub> | -                      | 2.4                     | _                          | V          | 3       |

| V <sub>OL</sub>  | Output LOW<br>Voltage               | I <sub>OL</sub> = 1 mA,                              |     | -                    | 0.2P-V <sub>CC</sub>   | -                       | 0.4                        | V          | 3       |

| V <sub>IH</sub>  | Input HIGH<br>Voltage               |                                                      |     | 0.8P-V <sub>CC</sub> | P-V <sub>CC</sub> +0.3 | P-V <sub>CC</sub> - 0.3 | P-V <sub>CC</sub> +<br>0.2 | V          | 3       |

| V <sub>IL</sub>  | Input LOW Voltage                   |                                                      |     | -0.3                 | 0.2P-V <sub>CC</sub>   | -0.2                    | 0.5                        | V          | 3       |

| Іон              | Output HIGH<br>Current              |                                                      |     | -                    | -                      | _                       | _                          | mA         | 2, 3    |

| I <sub>OL</sub>  | Output LOW<br>Current               |                                                      |     | -                    | _                      | _                       | _                          | mA         | 2, 3    |

| I <sub>IL</sub>  | Input Leakage<br>Current            | -0.2 < V <sub>IN</sub> < P-V <sub>CC</sub> +0.2 V    |     | -1                   | +1                     | -1                      | +1                         | μА         | 1, 2, 3 |

| I <sub>OL</sub>  | Output Leakage<br>Current           | $-0.2 < V_{IN} < P-V_{CC}$ $P-V_{CC} = V_{DF}$       |     | -1                   | +1                     | -1                      | +1                         | μА         | 1, 2, 3 |

- Input Leakage currents include Hi-Z output leakage for bi-directional buffers with tri-state outputs. All currents are in RMS unless noted otherwise. 1.

- 2.

- Not applicable to 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0YBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.

Table 9. **PSRAM DC Characteristics (See Note 3)**

| Parameter        | Description               | Test Conditio                                           |        | 1.8 V I                | PSRAM                  | 3.0 V F                 | PSRAM                      | Unit | 2<br>2<br>2 |

|------------------|---------------------------|---------------------------------------------------------|--------|------------------------|------------------------|-------------------------|----------------------------|------|-------------|

| Parameter        | Description               | rest Conditio                                           | ns     | Min                    | Max                    | Min                     | Max                        | Unit | Note        |

| v <sub>cc</sub>  | Voltage Range             |                                                         |        | 1.8                    | 1.95                   | 2.7                     | 3.1                        | V    |             |

| Icc              | Operating Current         | I <sub>IO</sub> = 0 mA                                  | 8M     | _                      | -                      | -                       | 30                         | mA   | 2           |

| Ç                | at min cycle time         | 10                                                      | 16M    | _                      | 30                     | _                       | 35                         |      |             |

|                  | Operating Current         | I = 0 A                                                 | 8M     | _                      | _                      | -                       | 5                          | mA   | 2           |

| I <sub>CC2</sub> | at max cycle time (1 μs)  | I <sub>IO</sub> = 0 mA                                  | 16M    | -                      | 5                      | 1                       | 7                          | mA   | 2           |

|                  |                           | P-CS# ≥ P-V <sub>CC</sub> -<br>0.2V.                    | 8M     | -                      | -                      | -                       | 80                         |      |             |

| I <sub>SB</sub>  | Standby Current           | All inputs stable<br>(either high or<br>low)            | 16M    | -                      | 100                    | -                       | 100                        | μΑ   | 2           |

| V <sub>OH</sub>  | Output HIGH<br>Voltage    | I <sub>OH</sub> = -0.1 m/                               | 4      | 1.4                    | _                      | P-V <sub>CC</sub> - 0.3 | _                          | V    |             |

| V <sub>OL</sub>  | Output LOW<br>Voltage     | I <sub>OL</sub> = 0.1 mA, V <sub>O</sub>                | CCMin  | -0.1                   | 0.2                    | -0.1                    | 0.3                        | V    |             |

| V <sub>IH</sub>  | Input HIGH<br>Voltage     |                                                         |        | P-V <sub>CC</sub> -0.3 | P-V <sub>CC</sub> +0.2 | P-V <sub>CC</sub> - 0.4 | P-V <sub>CC</sub> +<br>0.2 | V    |             |

| V <sub>IL</sub>  | Input LOW Voltage         |                                                         |        | -0.2                   | 0.4                    | -0.2                    | 0.6                        | V    |             |

| l <sub>ОН</sub>  | Output HIGH<br>Current    |                                                         |        | _                      | _                      | _                       | _                          | mA   | 2           |

| I <sub>OL</sub>  | Output LOW<br>Current     |                                                         |        | -                      | -                      | -                       | -                          | mA   | 2           |

| I <sub>IL</sub>  | Input Leakage<br>Current  | -0.2 < V <sub>IN</sub> < P-V <sub>CC</sub>              | +0.2 V | -1                     | +1                     | -1                      | +1                         | μА   | 1, 2        |

| I <sub>OL</sub>  | Output Leakage<br>Current | $-0.2 < V_{IN} < P-V_{CC}+0.2 V$<br>$P-V_{CC} = V_{DR}$ |        | -1                     | +1                     | -1                      | +1                         | μΑ   | 1, 2        |

- Input Leakage currents include Hi-Z output leakage for bi-directional buffers with tri-state outputs. 1.

- 2. 3. Applicable to 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0ZTQ2, 38F2030W0ZTQ2.

# 7.0 AC Characteristics

### 7.1 Flash AC Characteristics

Refer to the *Intel*<sup>®</sup> *Wireless Flash Memory (W18) Datasheet* (order number 290701) and *Intel*<sup>®</sup> *Wireless Flash Memory (W30) Datasheet* (order number 290702) for flash AC characteristics details not included in Table 10 below.

### Table 10. Flash AC Read Characteristics

| Nbr  | Sum                  | Parameter                | W                           | 18  | W30 |     | Unit |  |  |  |  |

|------|----------------------|--------------------------|-----------------------------|-----|-----|-----|------|--|--|--|--|

| NDI  | Sym                  | Farameter                | Min                         | Max | Min | Max | Unit |  |  |  |  |

|      |                      | Asynchronous Spec        | Asynchronous Specifications |     |     |     |      |  |  |  |  |

| R1   | t <sub>AVAV</sub>    | Read Cycle Time          | 65                          | _   | 70  | _   | ns   |  |  |  |  |

| R2   | t <sub>AVQV</sub>    | Address to Output Delay  | _                           | 65  | _   | 70  | ns   |  |  |  |  |

| R3   | t <sub>ELQV</sub>    | CE# Low to Output Delay  | _                           | 65  | _   | 70  | ns   |  |  |  |  |

|      |                      | Latching Specific        | cations                     |     |     |     |      |  |  |  |  |

| R103 | t <sub>VLQV</sub>    | ADV# Low to Output Delay | _                           | 65  | _   | 70  | ns   |  |  |  |  |

| R108 | t <sub>APA</sub>     | Page Address Access Time | _                           | 25  | 1   | 25  | ns   |  |  |  |  |

|      | Clock Specifications |                          |                             |     |     |     |      |  |  |  |  |

| R304 | t <sub>CHQV</sub>    | CLK to Output Delay      | _                           | 14  | _   | 20  | ns   |  |  |  |  |

### 7.2 SRAM AC Characteristics

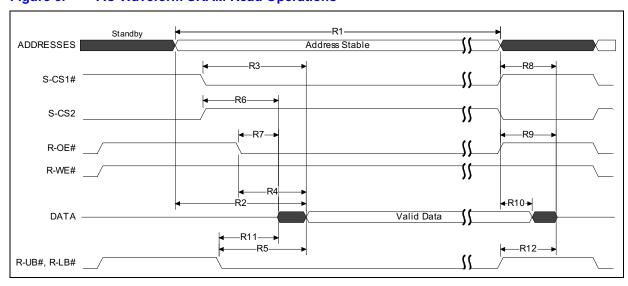

Table 11. SRAM AC Characteristics — Read Operations

| #   | Symbol           | Parameter                                                                         | Min | Max | Unit | Notes   |

|-----|------------------|-----------------------------------------------------------------------------------|-----|-----|------|---------|

| R1  | t <sub>RC</sub>  | Read Cycle Time                                                                   | 70  | -   | ns   | 1       |

| R2  | t <sub>AA</sub>  | Address to Output Delay                                                           | -   | 70  | ns   | 1       |

| R3  | t <sub>CO1</sub> | S-CS1# to Output Delay                                                            | _   | 70  | ns   | 1       |

| R3  | t <sub>CO2</sub> | S-CS2 to Output Delay                                                             | -   | 70  | ns   | 1       |

| R4  | t <sub>OE</sub>  | R-OE# to Output Delay                                                             | -   | 35  | ns   | 1       |

| R5  | t <sub>BA</sub>  | R-UB#, R-LB# to Output Delay                                                      | -   | 70  | ns   | 1       |

| R6  | t <sub>LZ</sub>  | S-CS1# or S-CS2 to Output in Low-Z                                                | 5   | _   | ns   | 1,3,4   |

| R7  | t <sub>OLZ</sub> | R-OE# to Output in Low-Z                                                          | 0   | _   | ns   | 1,4     |

| R8  | t <sub>HZ</sub>  | S-CS1# or S-CS2 to Output in High-Z                                               | 0   | 25  | ns   | 1,2,3,4 |

| R9  | t <sub>OHZ</sub> | R-OE# to Output in High-Z                                                         | 0   | 25  | ns   | 1,2,4   |

| R10 | t <sub>ОН</sub>  | Output Hold (from Address, S-CS1#, S-CS2 or R-OE# Change, whichever occurs first) | 0   | _   | ns   | 1       |

| R11 | t <sub>BLZ</sub> | R-UB#, R-LB# to Output in Low-Z                                                   | 0   | _   | ns   | 1,4     |

| R12 | t <sub>BHZ</sub> | R-UB#, R-LB# to Output in High-Z                                                  | 0   | 25  | ns   | 1,4     |

- See Figure 5, "AC Waveform SRAM Read Operations".

- Timings of t<sub>HZ</sub> and t<sub>OHZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- At any given temperature and voltage condition, t<sub>HZ</sub> (Max) is less than t<sub>LZ</sub> (Max) both for a given device and from device to device interconnection.

- 4. Sampled but not 100% tested.

Figure 5. AC Waveform SRAM Read Operations

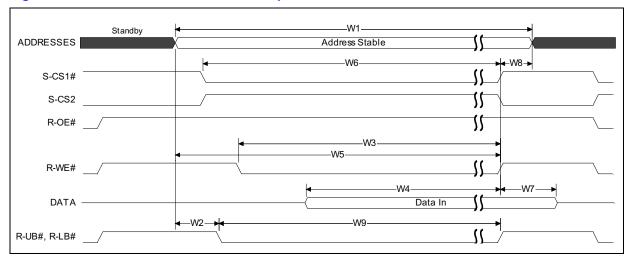

Table 12. **SRAM AC Characteristics — Write Operations**

| #  | Symbol          | Parameter                                           | Min | Max | Unit | Notes |

|----|-----------------|-----------------------------------------------------|-----|-----|------|-------|

| W1 | t <sub>WC</sub> | Write Cycle Time                                    | 70  | _   | ns   | 1     |

| W2 | t <sub>AS</sub> | Address Setup to R-WE# (S-CS1#) and R-UB#/R-LB# Low | 0   | _   | ns   | 1,4   |

| W3 | t <sub>WP</sub> | R-WE# (S-CS1#) Pulse Width                          | 55  | _   | ns   | 1,2,3 |

| W4 | t <sub>DW</sub> | Data to Write Time Overlap                          | 30  | _   | ns   | 1     |

| W5 | t <sub>AW</sub> | Address Setup to R-WE# (S-CS1#) High                | 60  | _   | ns   | 1     |

| W6 | t <sub>CW</sub> | S-CS1# (R-WE#) Setup to R-WE# (S-CS1#) High         | 60  | _   | ns   | 1     |

| W7 | t <sub>DH</sub> | Data Hold from R-WE# (S-CS1#) High                  | 0   | _   | ns   | 1     |

| W8 | t <sub>WR</sub> | Write Recovery                                      | 0   | _   | ns   | 1,5   |

| W9 | t <sub>BW</sub> | R-UB#, R-LB# Setup to R-WE# (S-CS1#) High           | 60  | _   | ns   | 1     |

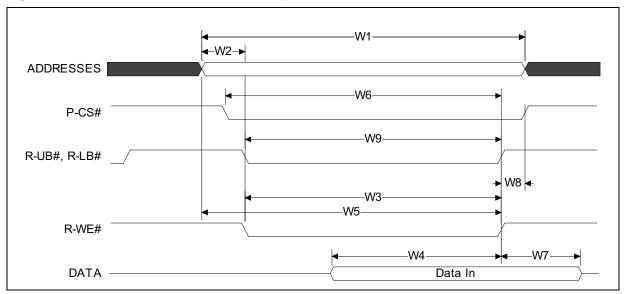

- See Figure 6, "AC Waveform SRAM Write Operations" .

- 1. 2. A write occurs during the overlap (t<sub>WP</sub>) of low S-CS1# and low R-WE#. A write begins when S-CS1# goes low and R-WE# goes low with asserting R-UB# and R-LB# for single byte operation or simultaneously asserting R-UB#R-LB# and R-LB# for double byte operation. A write ends at the earliest high transition of S-CS1# and R-WE#. twp is measured from the beginning to the end of a write.

- t<sub>WP</sub> is measured from S-CS1# low to the end of a write. 3.

- t<sub>AS</sub> is measured from the address valid to the beginning of a write. 4.

- twR is measured from the end of write to the address change. twR applied in case a write ends as S-CS1# or R-WE# goes high.

Figure 6. **AC Waveform SRAM Write Operations**

### 7.3 PSRAM AC Characteristics

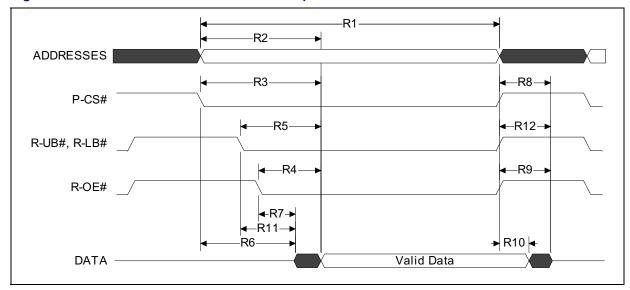

Table 13. PSRAM AC Characteristics — Read Operations

| #   | Cumbal           | Parameter <sup>6</sup>                                                    | 1.8 | 3 V   | 3.0 | V     | Unit | Notes   |

|-----|------------------|---------------------------------------------------------------------------|-----|-------|-----|-------|------|---------|

| #   | Symbol           | Farameter                                                                 | Min | Max   | Min | Max   | Omit | Notes   |

| R1  | t <sub>RC</sub>  | Read Cycle Time                                                           | 88  | 4,000 | 85  | 4,000 | ns   | 1       |

| R2  | t <sub>AA</sub>  | Address to Output Delay                                                   | _   | 88    | _   | 85    | ns   | 1       |

| R3  | t <sub>CO</sub>  | P-CS# to Output Delay                                                     | _   | 88    | _   | 85    | ns   | 1       |

| R4  | t <sub>OE</sub>  | R-OE# to Output Delay                                                     | _   | 65    | _   | 40    | ns   | 1       |

| R5  | t <sub>BA</sub>  | R-UB#, R-LB# to Output Delay                                              | _   | 88    | _   | 85    | ns   | 1       |

| R6  | t <sub>LZ</sub>  | P-CS# to Output in Low-Z                                                  | 10  | _     | 10  | _     | ns   | 1,3,4   |

| R7  | t <sub>OLZ</sub> | R-OE# to Output in Low-Z                                                  | 5   | _     | 0   | _     | ns   | 1,4     |

| R8  | t <sub>HZ</sub>  | P-CS# to Output in High-Z                                                 | _   | 25    | 0   | 25    | ns   | 1,2,3,4 |

| R9  | t <sub>OHZ</sub> | R-OE# to Output in High-Z                                                 | _   | 25    | 0   | 25    | ns   | 1,2,4   |

| R10 | t <sub>OH</sub>  | Output Hold (from Address, P-CS# or R-OE# change, whichever occurs first) | 5   | _     | 0   | -     | ns   | 1       |

| R11 | t <sub>BLZ</sub> | R-UB#, R-LB# to Output in Low-Z                                           | 5   | _     | 0   | _     | ns   | 1,4     |

| R12 | t <sub>BHZ</sub> | R-UB#, R-LB# to Output in High-Z                                          | _   | 25    | 0   | 25    | ns   | 1,4     |

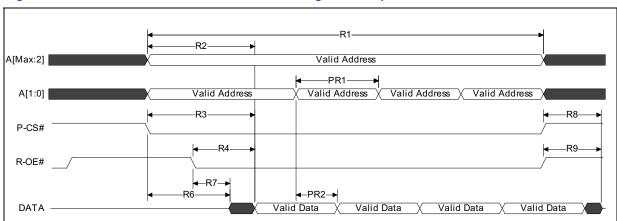

| PR1 | t <sub>PC</sub>  | Page Cycle Time                                                           | 30  | _     | 40  | _     | ns   | 5       |

| PR2 | t <sub>PA</sub>  | Page Access Time                                                          | _   | 30    | _   | 35    | ns   | 5       |

- 1. See Figure 7, "AC Waveform of PSRAM Read Operations" on page 29 and Figure 8, "AC Waveform of PSRAM 4-Word Page Read Operation" on page 29

- Timings of t<sub>HZ</sub> and t<sub>OHZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- At any given temperature and voltage condition, t<sub>HZ</sub> (Max) is less than t<sub>LZ</sub> (Max) both for a given device and from device to device interconnection.

- 4. Sampled but not 100% tested.

- 5. 4-Word Page read only available for 32-Mbit PSRAM. No page mode feature for 16-Mbit PSRAM.

- 6. Not applicable to 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0YBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.

Table 14. PSRAM AC Characteristics — Read Operations (Sheet 1 of 2)

| #   | Symbol           | Parameter <sup>6</sup>       | 1.8 | 3 V   | 3.0 | V     | Unit  | Notes |

|-----|------------------|------------------------------|-----|-------|-----|-------|-------|-------|

| , " | Symbol           | raianietei                   | Min | Max   | Min | Max   | Oilit | Notes |

| R1  | t <sub>RC</sub>  | Read Cycle Time              | 70  | 15000 | 70  | 15000 | ns    |       |

| R2  | t <sub>AA</sub>  | Address to Output Delay      | -   | 70    | _   | 70    | ns    |       |

| R3  | t <sub>CO</sub>  | P-CS# to Output Delay        | -   | 70    | _   | 70    | ns    |       |

| R4  | t <sub>OE</sub>  | R-OE# to Output Delay        | -   | 45    | _   | 45    | ns    |       |

| R5  | t <sub>BA</sub>  | R-UB#, R-LB# to Output Delay | -   | 70    | _   | 70    | ns    |       |

| R6  | t <sub>LZ</sub>  | P-CS# to Output in Low-Z     | 5   | _     | 5   | -     | ns    | 3     |

| R7  | t <sub>OLZ</sub> | R-OE# to Output in Low-Z     | 0   | _     | 0   | -     | ns    |       |

Table 14. PSRAM AC Characteristics — Read Operations (Sheet 2 of 2)

| #        | Symbol           | Parameter <sup>6</sup>                                                    | 1.8 | 3 V | 3.0 | V   | Unit  | Notes |

|----------|------------------|---------------------------------------------------------------------------|-----|-----|-----|-----|-------|-------|

| <b>"</b> | Symbol           | raidiletei                                                                | Min | Max | Min | Max | Oilit | Notes |

| R8       | t <sub>HZ</sub>  | P-CS# to Output in High-Z                                                 | 0   | 25  | 0   | 25  | ns    | 2, 3  |

| R9       | t <sub>OHZ</sub> | R-OE# to Output in High-Z                                                 | 0   | 25  | 0   | 25  | ns    | 2     |

| R10      | t <sub>OH</sub>  | Output Hold (from Address, P-CS# or R-OE# change, whichever occurs first) | 0   | _   | 0   | -   | ns    |       |

| R11      | t <sub>BLZ</sub> | R-UB#, R-LB# to Output in Low-Z                                           | 0   | _   | 0   | _   | ns    |       |

| R12      | t <sub>BHZ</sub> | R-UB#, R-LB# to Output in High-Z                                          | 0   | 25  | 0   | 25  | ns    |       |

| PR1      | t <sub>PC</sub>  | Page Cycle Time                                                           | 25  | -   | 25  | _   | ns    | 4     |

| PR2      | t <sub>PA</sub>  | Page Access Time                                                          | _   | 25  | ı   | 25  | ns    | 4     |

- 1. See Figure 7, "AC Waveform of PSRAM Read Operations" on page 29 and Figure 8, "AC Waveform of PSRAM 4-Word Page Read Operation" on page 29

- 2. Timings of t<sub>HZ</sub> and t<sub>OHZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- At any given temperature and voltage condition, t<sub>HZ</sub> (Max) is less than t<sub>LZ</sub> (Max) both for a given device and from device to device interconnection.

- 4. 4-Word Page read only available for 16-Mbit PSRAM. No page mode feature for 8-Mbit PSRAM.

- 5. 8-Mbit has additional skew limitation of 10 ns. 16-Mbit does not have this limitation.

- Applicable to 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0YBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.

Table 15. PSRAM AC Characteristics—Write Operations (Sheet 1 of 2)

| #        | Symbol          | Parameter <sup>6</sup> 1.8 V 3.0 V                        |     | V     | Unit | Notes |       |       |

|----------|-----------------|-----------------------------------------------------------|-----|-------|------|-------|-------|-------|

| <b>"</b> | Symbol          | raiameter                                                 | Min | Max   | Min  | Max   | Oiiit | Notes |

| W1       | t <sub>WC</sub> | Write Cycle Time                                          | 85  | 4,000 | 85   | 4,000 | ns    | 1     |

| W2       | t <sub>AS</sub> | Address Setup to R-WE# (P-CS#) and R-UB#, R-LB# going low | 0   | -     | 0    | -     | ns    | 1,4   |

| W3       | t <sub>WP</sub> | R-WE#(P-CS#) Pulse Width                                  | 60  | _     | 85   | _     | ns    | 1,2,3 |

| W4       | t <sub>DW</sub> | Data to Write Time Overlap                                | 30  | -     | 35   | -     | ns    | 1     |

| W5       | t <sub>AW</sub> | Address Setup to R-WE# (P-CS#) Going High                 | 70  | -     | 70   | -     | ns    | 1     |

| W6       | t <sub>CW</sub> | P-CS# (R-WE#) Setup to R-WE# (P-CS#)<br>Going High        | 70  | -     | 70   | -     | ns    | 1     |

| W7       | t <sub>DH</sub> | Data Hold from R-WE#<br>(P-CS#) High                      | 0   | _     | 0    | _     | ns    | 1     |

#### Table 15. PSRAM AC Characteristics—Write Operations (Sheet 2 of 2)

| W8         | t <sub>WR</sub> | Write Recovery                                 | 0  | - | 20 | _ | ns | 1,5 |

|------------|-----------------|------------------------------------------------|----|---|----|---|----|-----|

| <b>W</b> 9 | t <sub>BW</sub> | R-UB#, R-LB# Setup to R-WE# (P-CS#) Going High | 70 | _ | 70 | _ | ns | 1   |

#### Notes:

- 1. See Figure 9, "AC Waveform PSRAM Write Operation" .

- 2. A write occurs during the overlap (t<sub>WP</sub>) of low P-CS# and low R-WE#. A write begins when P-CS# goes low and R-WE# goes low with asserting R-UB# or R-LB# for single byte operation or simultaneously asserting R-UB# and R-LB# for double byte operation. A write ends at the earliest transition when P-CS# goes high and R-WE# goes high. The t<sub>WP</sub> is measured from the beginning to the end of a write.

- 3. t<sub>WP</sub> is measured from P-CS# going low to end of a write.

- t<sub>AS</sub> is measured from the address valid to the beginning of a write.

- 5. t<sub>WR</sub> is measured from the end of a write to the address change. t<sub>WR</sub> applied in case a write ends as P-CS# or R-WE# going high.

- Not applicable to 38F2020W0ZTQ1, 38F2020W0ZBQ1, 38F2030W0YTQ1, 38F2030W0YBQ1, 38F2030W0ZTQ2, 38F2030W0ZBQ2.

#### Table 16. PSRAM AC Characteristics—Write Operations

| #         | Symbol          | Parameter <sup>7</sup>                                    |     | 3.0 | V   | Unit | Notes |       |

|-----------|-----------------|-----------------------------------------------------------|-----|-----|-----|------|-------|-------|

| #         | Symbol          | Farameter                                                 | Min | Max | Min | Max  | Unit  | Notes |

| W1        | t <sub>WC</sub> | Write Cycle Time                                          | 70  | -   | 70  | -    | ns    | 1     |