### **ILXT970A** Dual-Speed Fast Ethernet Transceiver

#### Datasheet

The LXT970A is an enhanced derivative of the LXT970 10/100 Mbps Fast Ethernet PHY Transceiver that supports selectable driver strength capabilities and link-loss criteria. The LXT970A supports 100BASE-TX, 10BASE-T, and 100BASE-FX applications. It provides a Media Independent Interface (MII) for easy attachment to 10/100 Media Access Controllers (MAC)s and a pseudo-ECL interface for use with 100BASE-FX fiber networks.

The LXT970A supports full-duplex operation at 10 and 100 Mbps. Its operating condition is set using auto-negotiation, parallel detection or manual control. The encoder may be bypassed for symbol mode applications.

The LXT970A is fabricated with an advanced CMOS process and requires only a single 5V power supply. The MII may be operated independently with either a 5V or a 3.3V supply.

#### **Applications**

- Combination 10BASE-T/100BASE-TX Network Interface Cards (NICs)

- 10/100 Switches, 10/100 Printservers

#### **Product Features**

- IEEE 802.3 Compliant:

- —10BASE-T and 100BASE-TX using a single RJ-45 connection.

- Supports auto-negotiation and parallel detection for legacy systems.

- MII interface with extended register capability.

- Robust baseline wander correction performance.

- 100BASE-FX fiber optic capable.

- Standard CSMA/CD or full-duplex operation.

- Configurable via MII serial port or external control pins.

- 100BASE-FX Network Interface Cards (NICs)

- Configurable for DTE or switch applications.

- CMOS process with single 5Vsupply operation with provision for interface to 3.3V MII bus.

- Integrated LED drivers.

- Integrated supply monitor and line disconnect during low supply fault.

- Available in:

- -64-pin TQFP (LXT970ATC)

- -64-pin PQFP (LXT970AQC)

- Commercial temperature range (0 70°C ambient).

### intel

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT970A may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

# int<sub>e</sub>l。 *Contents*

| 1.0 | Pin /       | Assignr   | ments and Signal Descriptions               | 10 |

|-----|-------------|-----------|---------------------------------------------|----|

| 2.0 | Fund        | ctional   | Description                                 | 18 |

|     | 2.1         | Introdu   | uction                                      |    |

|     | 2.2         |           | ces (Network Media/Protocol Support)        |    |

|     |             | 2.2.1     | Twisted-Pair Interface                      |    |

|     |             | 2.2.2     | Fiber Interface                             |    |

|     |             | 2.2.3     | MII Interface                               |    |

|     |             | 2.2.0     | 2.2.3.1 Selectable Driver Levels            |    |

|     |             |           | 2.2.3.2 MII Data Interface                  |    |

|     |             |           | 2.2.3.3 Repeater Mode                       |    |

|     |             |           | 2.2.3.4 MII Management Interface            |    |

|     |             | 2.2.4     | Hardware Control Interface                  |    |

|     | 2.3         | Operat    | ting Requirements                           |    |

|     |             | 2.3.1     | Power Supply Requirements                   |    |

|     |             |           | 2.3.1.1 Optional MII Power Supply           |    |

|     |             | 2.3.2     | Reference Clock Requirements                |    |

|     |             | -         | 2.3.2.1 Master Clock Mode                   |    |

|     |             |           | 2.3.2.2 Slave Clock Mode                    |    |

|     |             | 2.3.3     | Bias Circuit Requirements                   | 29 |

|     | 2.4         | Initializ | ation                                       |    |

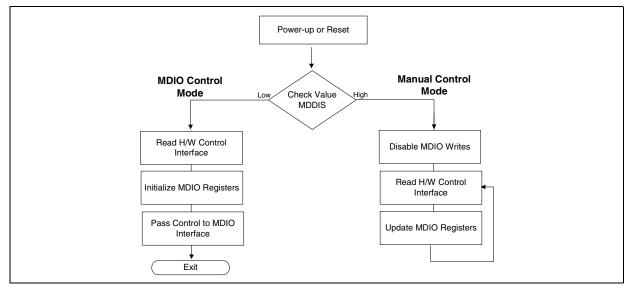

|     |             | 2.4.1     | Control Mode Selection                      |    |

|     |             |           | 2.4.1.1 MDIO Control Mode                   |    |

|     |             |           | 2.4.1.2 Manual Control Mode                 |    |

|     |             | 2.4.2     | Link Configuration                          |    |

|     |             |           | 2.4.2.1 Manual Configuration                |    |

|     |             |           | 2.4.2.2 Auto-Negotiation/Parallel Detection |    |

|     | 2.5         | Monito    | ring Operational Status                     |    |

|     |             | 2.5.1     | Monitoring Status via MII Registers         |    |

|     |             | 2.5.2     | Monitoring Status via Indicator Pins        |    |

|     | 2.6         | 100BA     | SE-X Operation                              |    |

|     |             | 2.6.1     | 100BASE-X MII Operations                    |    |

|     |             | 2.6.2     | 100BASE-X Network Operations                |    |

|     | 2.7         |           | SE-T Operation                              |    |

|     | <b>_</b> ., | 2.7.1     | 10BASE-T MII Operations                     |    |

|     |             | 2.7.2     | 10BASE-T Network Operations                 |    |

|     | 2.8         |           | ol Sublayer Operations                      |    |

|     | 2.0         | 2.8.1     | PCS Sublayer                                |    |

|     |             | 2.0.1     | 2.8.1.1 100X Preamble Handling              |    |

|     |             |           | 2.8.1.2 10T Preamble Handling               |    |

|     |             |           | 2.8.1.3 Data Errors (100X Only)             |    |

|     |             |           | 2.8.1.4 Collision Indication                |    |

|     |             |           | 2.8.1.5 SQE (10T Only)                      |    |

|     |             |           | 2.8.1.6 Jabber (10T Only)                   |    |

|     |             | 2.8.2     | PMA Layer                                   |    |

|     |             |           | 2.8.2.1 100TX Link Options                  |    |

|     |             |           | 2.8.2.2 10T Link Test                       |    |

|     |       |         | 2.8.2.3 Carrier Sense (CRS)                  |    |

|-----|-------|---------|----------------------------------------------|----|

|     |       | 2.8.3   | Twisted-Pair PMD Layer                       |    |

|     |       |         | 2.8.3.1 Scrambler/Descrambler (100TX Only)   |    |

|     |       |         | 2.8.3.2 Baseline Wander Correction           |    |

|     |       |         | (100TX Only)39                               |    |

|     |       |         | 2.8.3.3 Polarity Correction                  |    |

|     |       | 2.8.4   | Fiber PMD Layer                              |    |

|     |       | 2.8.5   | Additional Operating Features                |    |

|     |       | 2.8.6   | Low-Voltage-Fault Detect                     |    |

|     |       | 2.8.7   | Power Down Mode                              |    |

|     |       | 2.8.8   | Software Reset                               |    |

|     |       | 2.8.9   | Hardware Reset                               |    |

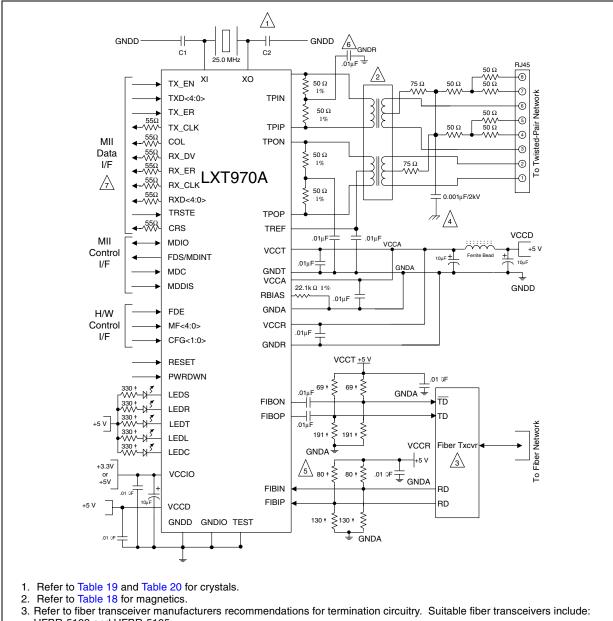

| 3.0 | Appli | cation  | Information                                  | 41 |

|     | 3.1   | Magne   | etics Information                            | 41 |

|     | 3.2   |         | I Information                                |    |

|     | 3.3   |         | n Recommendations                            |    |

|     |       | 3.3.1   | General Design Guidelines                    |    |

|     |       | 3.3.2   | Power Supply Filtering                       |    |

|     |       | 3.3.3   | Ground Noise                                 |    |

|     |       | 3.3.4   | Power and Ground Plane Layout Considerations | 43 |

|     |       | 3.3.5   | Interfaces for Twisted-Pair /Fiber           | 43 |

|     |       |         | 3.3.5.1 Twisted-Pair                         |    |

|     |       |         | 3.3.5.2 Fiber                                |    |

|     |       | 3.3.6   | Interface for the MII                        |    |

|     |       |         | 3.3.6.1 Transmit Hold Time Adjustment        |    |

|     |       |         | 3.3.6.2 MII Terminations                     |    |

|     |       | 3.3.7   | Typical Application                          |    |

|     |       |         | 3.3.7.1 Voltage Divider For MF Inputs        | 45 |

| 4.0 | Test  | Specif  | ications                                     | 47 |

| 5.0 | Regis | ster De | efinitions                                   | 63 |

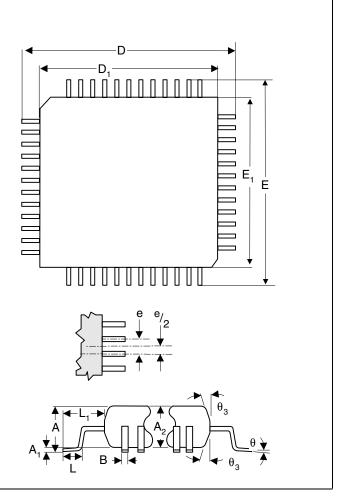

| 6.0 | Mech  | anical  | Specifications                               | 73 |

|     |       |         | •                                            |    |

# intel®

### Figures

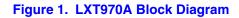

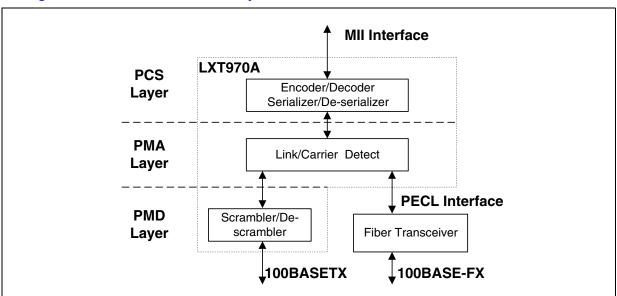

| 1  | LXT970A Block Diagram                               | 9    |

|----|-----------------------------------------------------|------|

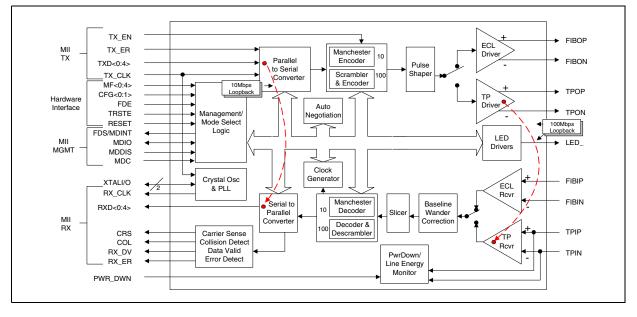

| 2  | LXT970A Pin Assignments                             |      |

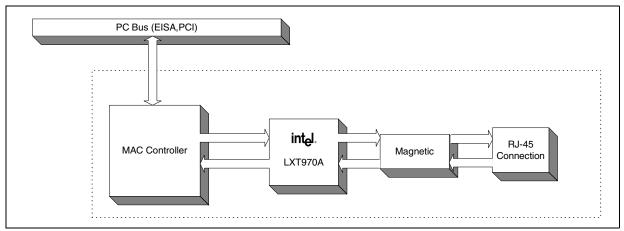

| 3  | Network Interface Card (NIC) Application            | .18  |

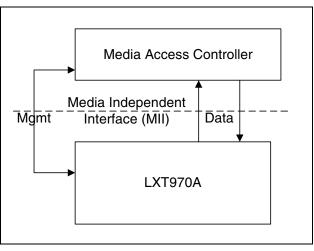

| 4  | MII Interface                                       | .20  |

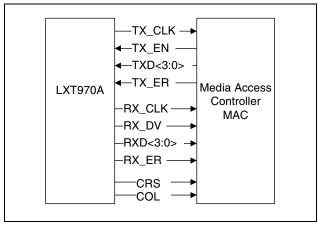

| 5  | MII Data Interface                                  | .21  |

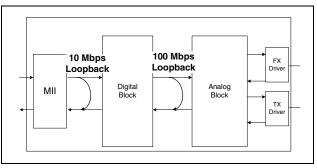

| 6  | Loopback Paths                                      | .23  |

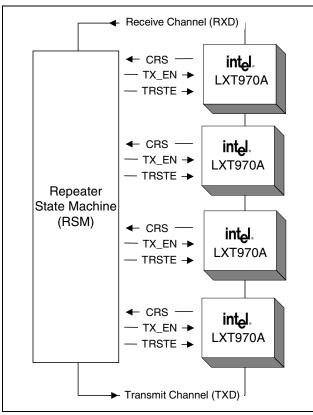

| 7  | Repeater Block Diagram                              | .24  |

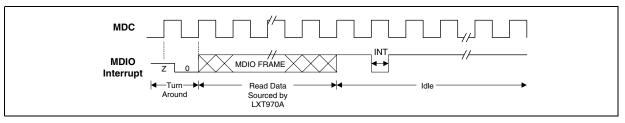

| 8  | MDIO Interrupt Signaling                            | .25  |

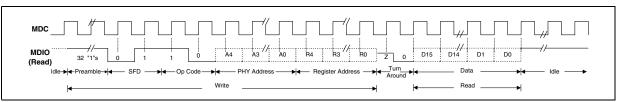

| 9  | Management Interface - Read Frame Structure         | .25  |

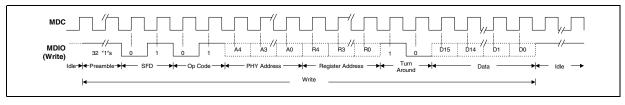

| 10 | Management Interface - Write Frame Structure        | .25  |

| 11 | LXT970A Initialization Sequence                     | .30  |

| 12 | Auto-Negotiation Operation                          | .31  |

| 13 | 100BASE-TX Frame Structure                          | .33  |

| 14 | 100BASE-TX Data Flow                                | .33  |

| 15 | LXT970A Protocol Sublayers                          | .36  |

| 16 | 100BASE-TX Reception with No Errors                 | .37  |

| 17 | 100BASE-TX Reception with Invalid Symbol            | .37  |

| 18 | 100BASE-TX Transmission with No Errors              | .37  |

| 19 | 100BASE-TX Transmission with Collision              | .37  |

| 20 | Voltage Divider                                     |      |

| 21 | Typical Interface Circuitry                         | .46  |

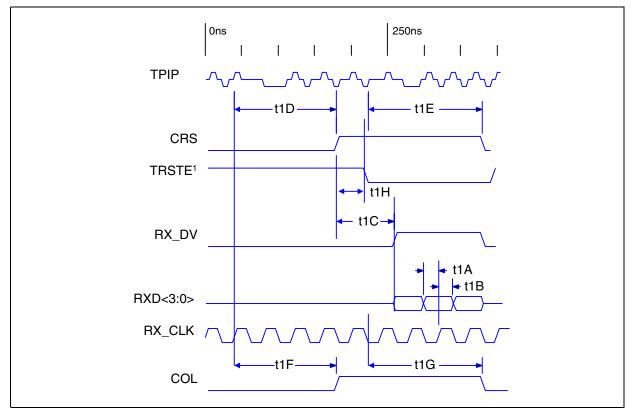

| 22 | MII - 100BASE-TX Receive Timing / 4B Mode           | .51  |

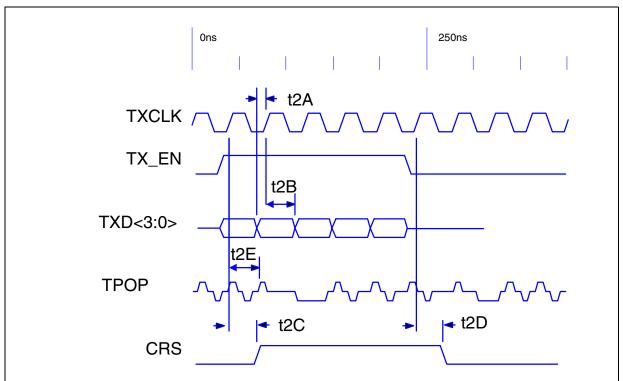

| 23 | MII - 100BASE-TX Transmit Timing / 4B Mode          | .52  |

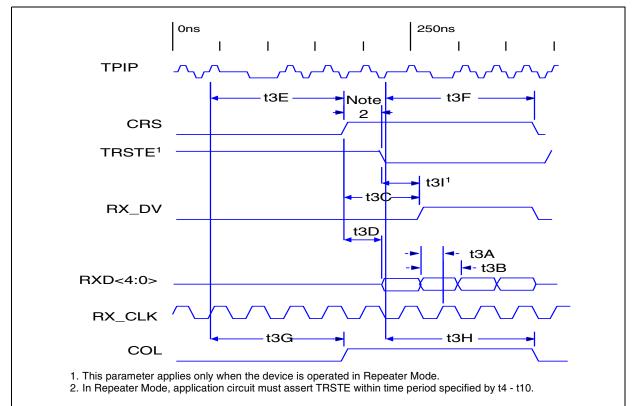

| 24 | MII - 100BASE-TX Receive Timing / 5B Mode           | .53  |

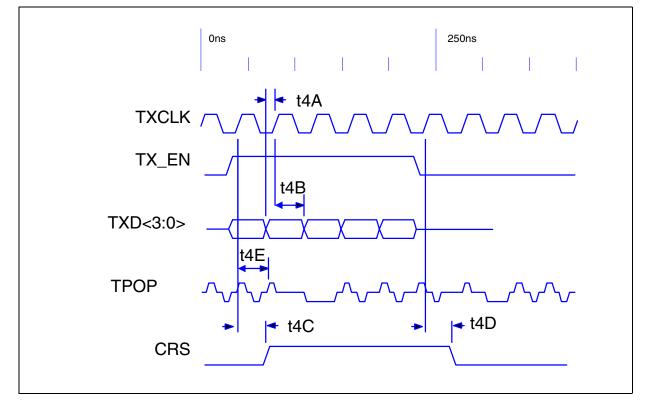

| 25 | 100BASE-TX Transmit Timing / 5B Mode                | .54  |

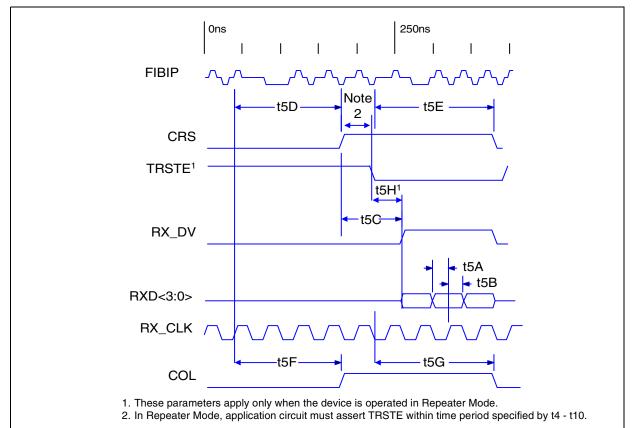

| 26 | MII - 100BASE-FX Receive Timing / 4B Mode           | .55  |

| 27 | MII - 100BASE-FX Transmit Timing / 4B Mode          | .56  |

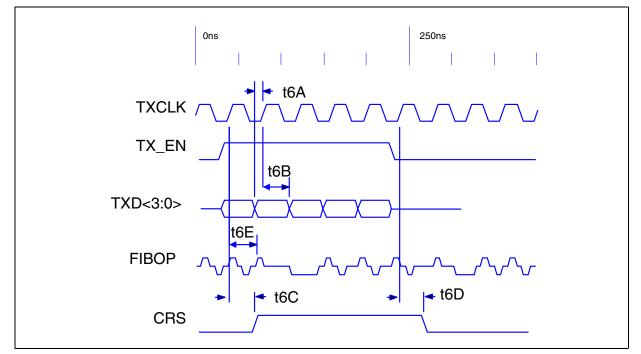

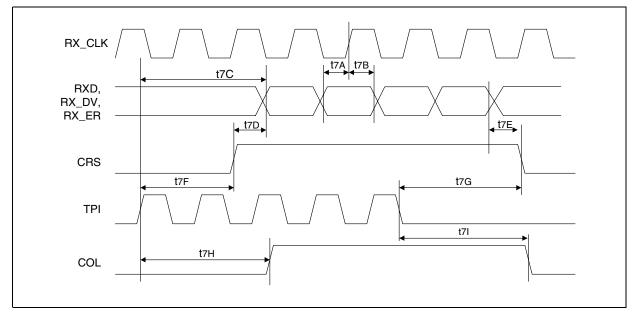

| 28 | MII - 10BASE-T Receiving Timing                     | .57  |

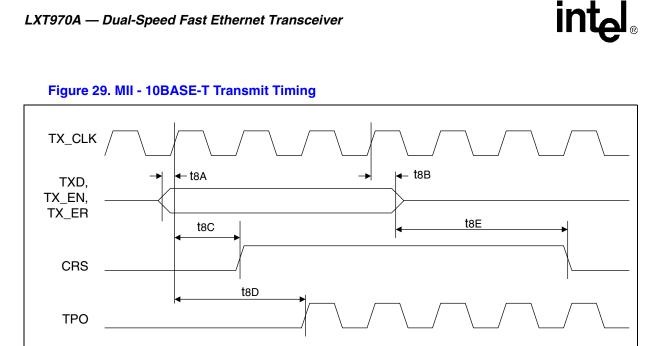

| 29 | MII - 10BASE-T Transmit Timing                      | . 58 |

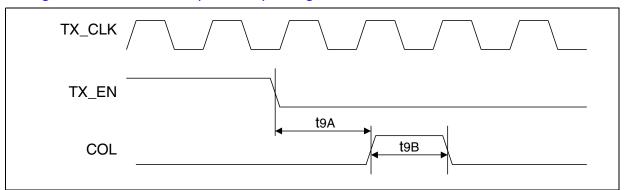

| 30 | 10BASE-T SQE (Heartbeat) Timing                     | . 59 |

| 31 | 10BASE-T Jab and Unjab Timing                       | . 59 |

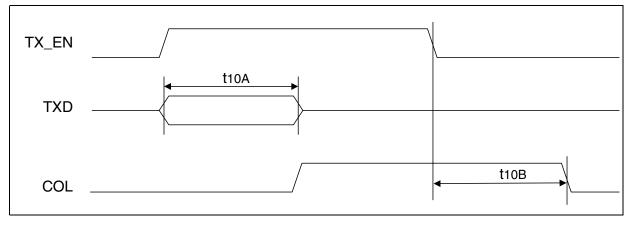

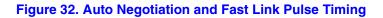

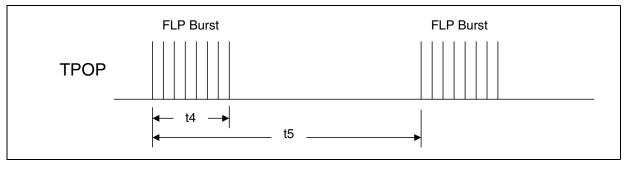

| 32 | Auto Negotiation and Fast Link Pulse Timing         | .60  |

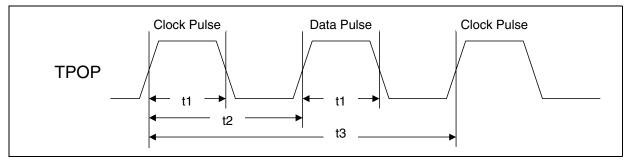

| 33 | Fast Link Pulse Timing                              | .60  |

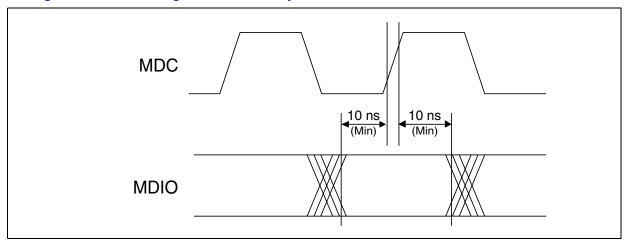

| 34 | MDIO Timing when Sourced by STA                     | .61  |

| 35 | MDIO Timing when Sourced by PHY                     | .61  |

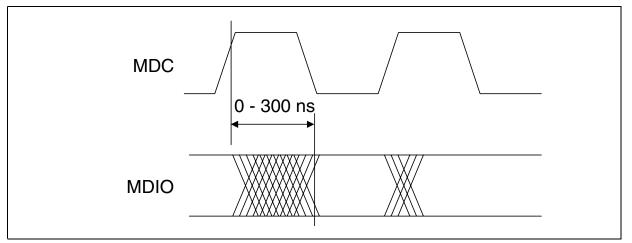

| 36 | Power-Down Recovery Timing (Over Recommended Range) |      |

| 37 | PHY Identifier Bit Mapping                          |      |

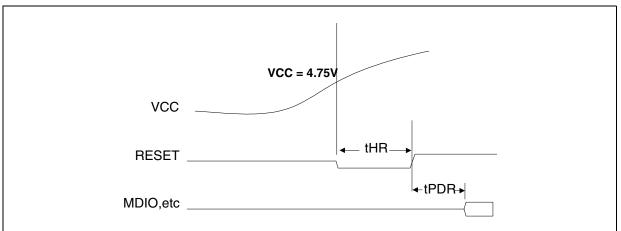

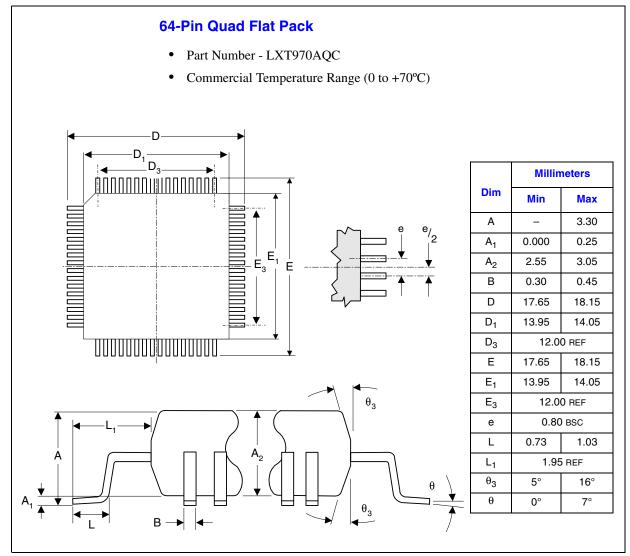

| 38 | 64-Pin QFP Package Diagram                          |      |

| 39 | 64-Pin TQFP Package Diagram                         | .74  |

|    |                                                     |      |

#### **Tables**

| 1        | LXT970A Power Supply Signal Descriptions                     |      |

|----------|--------------------------------------------------------------|------|

| 2        | LXT970A MII Signal Descriptions                              | .11  |

| 3        | LXT970A Fiber Interface Signal Descriptions                  |      |

| 4        | LXT970A Twisted-Pair Interface Signal Descriptions           | . 13 |

| 5        | LXT970A LED Indicator Signal Descriptions                    | . 13 |

| 6        | LXT970A Miscellaneous Signal Descriptions                    | .13  |

| 7        | LXT970A Hardware Control Interface Signal Descriptions       | .14  |

| 8        | MF Pin Function Settings1, 3                                 |      |

| 9        | LXT970A Auto-Negotiation Operating Speed/Full-Duplex         |      |

|          | Advertisement Settings                                       | . 17 |

| 10       | Test Loopback Operation                                      |      |

| 11       | Carrier Sense, Loopback, and Collision Conditions            |      |

| 12       | Configuring the LXT970A via Hardware Control                 | .26  |

| 13       | LXT970A Operating Configurations / Auto-Negotiation Enabled  |      |

| 14       | LXT970A Operating Configurations / Auto-Negotiation Disabled |      |

| 15       | Mode Control Settings                                        |      |

| 16       | LXT970A Status using FDS/LED Pins                            |      |

| 17       | 4B/5B Coding                                                 |      |

| 18       | Magnetics Requirements                                       |      |

| 19       | Crystal Requirements                                         |      |

| 20       | Crystal Component Manufacturers                              |      |

| 21       | Absolute Maximum Ratings                                     |      |

| 22       | Operating Conditions                                         |      |

| 23       | Digital I/O Characteristics1                                 |      |

| 24       | Digital I/O Characteristics - MultiFunction Pins MF<4:0>     |      |

| 25       | Required Clock Characteristics                               |      |

| 26       | Low Voltage Fault Detect Characteristics                     |      |

| 27       | 100BASE-TX Transceiver Characteristics                       |      |

| 28       | 100BASE-FX Transceiver Characteristics                       |      |

| 29       | 10BASE-T Transceiver Characteristics                         |      |

| 30       | 10BASE-T Link Integrity Timing Characteristics               |      |

| 31       | MII - 100BASE-TX Receive Timing Parameters / 4B Mode         |      |

| 32       | MII - 100BASE-TX Transmit Timing Parameters / 4B Mode        |      |

| 33       | MII - 100BASE-TX Receive Timing Parameters / 5B Mode         |      |

| 34       | MII - 100BASE-TX Transmit Timing Parameters / 5B Mode        |      |

| 35       | MII - 100BASE-FX Receive Timing Parameters / 4B Mode         |      |

| 36       | MII - 100BASE-FX Transmit Timing Parameters / 4B Mode        |      |

| 37       | MII - 10BASE-T Receive Timing Parameters                     |      |

| 38       | MII - 10BASE-T Transmit Timing Parameters                    |      |

| 39       | 10BASE-T SQE (Heartbeat) Timing Parameters                   |      |

| 40       | 10BASE-T Jab and Unjab Timing Parameters                     |      |

| 41       | Auto Negotiation and Fast Link Pulse Timing Parameters       |      |

| 42       | MDIO Timing Parameters                                       |      |

| 43       | -                                                            |      |

|          | Power-Down Recovery Timing Parameters                        |      |

| 44<br>45 | Register Set                                                 |      |

| 45<br>46 | Control Register (Address 0)                                 |      |

| 46       | Status Register (Address 1)                                  | .00  |

| 47       | PHY Identification Register 1 (Address 2)                    |      |

| 48       | PHY Identification Register 2 (Address 3)                    | . 00 |

| Auto Negotiation Advertisement Register (Address 4)        | 67                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto Negotiation Link Partner Ability Register (Address 5) | 68                                                                                                                                                                                                                                                                                                                                                                                                  |

| Auto Negotiation Expansion (Address 6)                     | 69                                                                                                                                                                                                                                                                                                                                                                                                  |

| Mirror Register (Address 16, Hex 10)                       | 69                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupt Enable Register (Address 17, Hex 11)             | 70                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupt Status Register (Address 18, Hex 12)             | 70                                                                                                                                                                                                                                                                                                                                                                                                  |

| Configuration Register (Address 19, Hex 13)                | 71                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                            | Auto Negotiation Advertisement Register (Address 4)<br>Auto Negotiation Link Partner Ability Register (Address 5)<br>Auto Negotiation Expansion (Address 6)<br>Mirror Register (Address 16, Hex 10)<br>Interrupt Enable Register (Address 17, Hex 11)<br>Interrupt Status Register (Address 18, Hex 12)<br>Configuration Register (Address 19, Hex 13)<br>Chip Status Register (Address 20, Hex 14) |

### **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

#### 1.0 Pin Assignments and Signal Descriptions

#### Figure 2. LXT970A Pin Assignments

#### Table 1. LXT970A Power Supply Signal Descriptions

| Pin# <sup>1</sup> | Pin Name                | I/O  | Signal Description                                    |

|-------------------|-------------------------|------|-------------------------------------------------------|

| 19, 22            | VCCT, GNDT              | -    | Transmitter Supply (+5V) and Ground. (Analog plane)   |

| 37, 31            | VCCR, NDR               | -    | Receiver Supply (+5V) and Ground. (Analog plane)      |

| 24, 26            | VCCA, NDA               | -    | Analog Supply (+5V) and Ground.                       |

| 9, 43             | VCCD, GNDD              | -    | Digital Supply (+5V) and Ground.                      |

| 53, 52            | VCCIO, GNDIO            | -    | MII Supply (+3.3V or +5V) and Ground. (Digital plane) |

| 1. Pin numbers a  | pply to all package typ | oes. | •                                                     |

| Pin# <sup>1</sup> | Pin Name | I/O <sup>2,3</sup> | Signal Description <sup>4</sup>                                                                                                                                                                                                                                                                             |

|-------------------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |          |                    | MII Data Interface Pins                                                                                                                                                                                                                                                                                     |

| 63                | TXD4     |                    |                                                                                                                                                                                                                                                                                                             |

| 62                | TXD3     |                    | Transmit Data. The Media Access Controller (MAC) drives data to the                                                                                                                                                                                                                                         |

| 61                | TXD2     | I                  | LXT970A using these inputs. TXD4 is monitored only in Symbol (5B) Mode.                                                                                                                                                                                                                                     |

| 60                | TXD1     |                    | These signals must be synchronized to the TX_CLK.                                                                                                                                                                                                                                                           |

| 59                | TXD0     |                    |                                                                                                                                                                                                                                                                                                             |

| 58                | TX_EN    | I                  | <b>Transmit Enable</b> . The MAC asserts this signal when it drives valid data on the TXD inputs. This signal must be synchronized to the TX_CLK.                                                                                                                                                           |

| 57                | TX_CLK   | I/O                | <ul> <li>Transmit Clock. Normally the LXT970A drives TX_CLK; in Slave Clock Mode TX_CLK is an input. Refer to the Clock Requirements discussion in the Functional Description section on page 18.</li> <li>25 MHz for 100 Mbps operation.</li> <li>2.5 MHz for 10 Mbps operation.</li> </ul>                |

| 56                | TX_ER    | I                  | <b>Transmit Coding Error</b> . The MAC asserts this input when an error has occurred in the transmit data stream. When the LXT970A is operating at 100 Mbps, the LXT970A responds by sending invalid code symbols on the line.                                                                              |

| 46                | RXD4     |                    |                                                                                                                                                                                                                                                                                                             |

| 47                | RXD3     |                    | Receive Data. The LXT970A drives received data on these outputs,                                                                                                                                                                                                                                            |

| 48                | RXD2     | 0                  | synchronous to RX_CLK.                                                                                                                                                                                                                                                                                      |

| 49                | RXD1     |                    | RXD4 is driven only in Symbol (5B) Mode.                                                                                                                                                                                                                                                                    |

| 50                | RXD0     |                    |                                                                                                                                                                                                                                                                                                             |

| 51                | RX_DV    | 0                  | <b>Receive Data Valid</b> . The LXT970A asserts this signal when it drives valid data on RXD. This output is synchronous to RX_CLK.                                                                                                                                                                         |

| 55                | RX_ER    | 0                  | <b>Receive Error</b> . The LXT970A asserts this output when it receives invalid symbols from the network. This signal is synchronous to RX_CLK.                                                                                                                                                             |

| 54                | RX_CLK   | 0                  | <ul> <li>Receive Clock. This continuous clock provides reference for RXD, RX_DV, and RX_ER signals. Refer to the Clock Requirements discussion in the Functional Description section.</li> <li>25 MHz for 100 Mbps operation.</li> <li>2.5 MHz for 10 Mbps operation.</li> </ul>                            |

| 64                | COL      | ο                  | <b>Collision Detected</b> . The LXT970A asserts this output when detecting a collision. This output remains High for the duration of the collision. This signal is asynchronous and inactive during full-duplex operation.                                                                                  |

| 1                 | CRS      | 0                  | <b>Carrier Sense</b> . During half-duplex operation (bit $0.8 = 0$ ), the LXT970A asserts this output when either transmit or receive medium is non-idle. During full-duplex operation (bit $0.8 = 1$ ) or repeater operation (bit $19.13 = 1$ ), CRS is asserted only when the receive medium is non-idle. |

#### Table 2. LXT970A MII Signal Descriptions

1. Pin numbers apply to all package types.

I/O Column Coding: I = Input, O = Output, OD = Open Drain, A = Analog.

If bit 17.3 = 0, 55Ω series termination resistors are recommended on all output signals to avoid undershoot/overshoot, even on short traces.

If bit 17.3 = 1, termination resistors are not required.

4. The LXT970A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

| Pin# <sup>1</sup> | Pin Name                                  | I/O <sup>2,3</sup> | Signal Description <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------|-------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   |                                           |                    | <b>Tri-state</b> . In DTE Mode (19.13 = 0), when TRSTE input is High, the LXT970A isolates itself from the MII Data Interface, and controls the MDIO register bit 0.10 (Isolate bit).                                                                                                                                                                                                                                                   |  |

| 3                 | TRSTE                                     | I                  | When MDDIS is High, TRSTE provides continuous control over bit 0.10. When MDDIS is Low, TRSTE sets initial (default) values only and reverts control back to the MDIO interface.                                                                                                                                                                                                                                                        |  |

|                   |                                           |                    | In Repeater Mode (19.13 = 1), when TRSTE input is High, the LXT970A tri-<br>states the receive outputs of the MII (RXD<4:0>, RX_DV, RX_ER, RX_CLK).                                                                                                                                                                                                                                                                                     |  |

|                   | •                                         |                    | MII Control Interface Pins                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 15                | MDDIS                                     | I                  | <b>Management Disable</b> . When MDDIS is High, the MDIO is restricted to Read Only and the MF<4:0>, CFG<1:0>, and FDE pins provide continual control of their respective bits. When MDDIS is Low at power up or Reset, the MF<4:0>, CFG<1:0>, and FDE pins control only the initial or "default" values of their respective register bits. After the power-up/reset cycle is complete, bit control reverts to the MDIO serial channel. |  |

| 45                | MDC                                       | I                  | Management Data Clock. Clock for the MDIO serial data channel. Maximum frequency is 2.5 MHz.                                                                                                                                                                                                                                                                                                                                            |  |

| 44                | MDIO                                      | I/O                | Management Data Input/Output. Bidirectional serial data channel for PHY/STA communication.                                                                                                                                                                                                                                                                                                                                              |  |

|                   |                                           |                    | <b>Full-Duplex Status.</b> When bit 17.1 = 0 (default), this pin indicates full-duplex status. (High = full-duplex, Low = half-duplex)                                                                                                                                                                                                                                                                                                  |  |

| 2                 | FDS/MDINT                                 | OD                 | This pin can drive a high efficiency LED. (See Table 23 for detail specifications).                                                                                                                                                                                                                                                                                                                                                     |  |

| 2                 | PD3/MDINT                                 | 00                 | <b>Management Data Interrupt</b> . When bit 17.1 = 1, an active Low output on this pin indicates status change.                                                                                                                                                                                                                                                                                                                         |  |

|                   |                                           |                    | Interrupt is cleared by sequentially reading Register 1, then Register 18.                                                                                                                                                                                                                                                                                                                                                              |  |

| 1. Pin numbers a  | . Pin numbers apply to all package types. |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

#### Table 2. LXT970A MII Signal Descriptions (Continued)

Pin numbers apply to all package types.

I/O Column Coding: I = Input, O = Output, OD = Open Drain, A = Analog.

3. If bit  $17.3 = 0, 55\Omega$  series termination resistors are recommended on all output signals to avoid undershoot/overshoot, even on short traces.

If bit 17.3 = 1, termination resistors are not required.

4. The LXT970A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

#### Table 3. LXT970A Fiber Interface Signal Descriptions

| Pin# <sup>1</sup> | Pin Name                                | I/O <sup>2</sup> | Signal Description                                                                       |

|-------------------|-----------------------------------------|------------------|------------------------------------------------------------------------------------------|

| 17                | FIBOP                                   | 0                | Fiber Output, Positive and Negative. Differential pseudo-ECL driver pair compatible with |

| 18                | FIBON                                   | 0                | standard fiber transceiver for 100BASE-FX.                                               |

| 27                | FIBIP                                   |                  | Fiber Input, Positive and Negative. Differential pseudo-ECL receive pair compatible with |

| 28                | FIBIN                                   | 1                | standard fiber transceiver for 100BASE-FX.                                               |

|                   | Imbers apply to al<br>blumn Coding: I = |                  | e types.<br>= Output, OD = Open Drain, A = Analog.                                       |

| Pin# <sup>1</sup> | Pin Name         | I/O <sup>2</sup> | Signal Description                                                                       |

|-------------------|------------------|------------------|------------------------------------------------------------------------------------------|

| 21                | TPOP             |                  | Twisted-Pair Output, Positive and Negative. Differential driver pair produces 802.3-     |

| 23                | TPON             | AO               | compliant pulses for either 100BASE-TX or 10BASE-T transmission.                         |

| 20                | TREF             | AO               | Transmit Reference. Tie to center tap of output transformer.                             |

| 29                | TPIP             |                  | Twisted-Pair Input, Positive and Negative. Differential input pair for either 100BASE-TX |

| 30                | TPIN             | AI               | or 10BASE-T reception.                                                                   |

|                   | mbers apply to a |                  | e types.<br>= Output, OD = Open Drain, A = Analog                                        |

#### Table 4. LXT970A Twisted-Pair Interface Signal Descriptions

#### Table 5. LXT970A LED Indicator Signal Descriptions

| LEDS<br>LEDR | 0    | Speed LED. Active Low output indicates 100 Mbps operation is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEDR         |      | - Free State Stat |

|              | 0    | Receive LED. Active Low output indicates that receiver is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LEDT         | 0    | Transmit LED. Active Low output indicates transmitter is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LEDL         | 0    | Link LED. Active Low output;<br>During 100 Mbps operation, indicates scrambler lock and receipt of valid Idle codes.<br>During 10 Mbps operation, indicates Link Valid status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LEDC         | 0    | <b>Collision LED</b> . In default mode, active Low output indicates collision. However, LEDC is programmable and may be set for other indications. For programming options, see Configuration Register 19 in Table 55, "Configuration Register (Address 19, Hex 13)" on page 71.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | LEDL | LEDL O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Pin numbers apply to an package types.

I/O Column Coding: I = Input, O = Output, OD = Open Drain, A = Analog.

LEDs are read at power-up to determine scrambler seed values.

#### Table 6. LXT970A Miscellaneous Signal Descriptions

| Pin# <sup>1</sup> | Pin Name                                | I/O <sup>2</sup> | Signal Description                                                                                                                                                                                   |

|-------------------|-----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                | TEST                                    | I                | Test. Must be tied Low.                                                                                                                                                                              |

| 12<br>11          | XI<br>XO                                | 1<br>0           | <b>Crystal Input and Output</b> . Use a clock at XI or connect a 25 MHz crystal oscillator across XI and XO. Refer to the Functional Description section for detailed clock requirements on page 18. |

| 25                | RBIAS                                   | AI               | <b>Bias Control</b> . Controls operating circuit bias via an external 22.1 k $\Omega$ , 1% resistor to ground.                                                                                       |

| 16                | RESET                                   | I                | <b>Reset</b> . This active Low input is OR'ed with the control register Reset bit (0.15). The LXT970A reset cycle is extended 300 $\mu$ s (nominal) after Reset is de-asserted.                      |

| 34                | PWRDWN                                  | I                | <b>Power Down</b> . When High, forces LXT970A into power down mode. This pin is OR'ed with the Power Down bit (0.11). Refer to Table 45 for more information.                                        |

| 32, 35,<br>36     | N/C                                     | -                | No Connection. Leave open.                                                                                                                                                                           |

|                   | umbers apply to al<br>plumn Coding: I = |                  | e types.<br>= Output, OD = Open Drain, A = Analog.                                                                                                                                                   |

| Pin# <sup>1</sup> | Pin Name | I/O <sup>2</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |            | Signal Description <sup>3</sup>               |  |  |  |

|-------------------|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-----------------------------------------------|--|--|--|

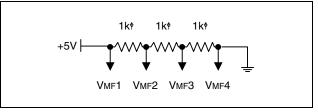

|                   |          |                  | <b>Multi-Function (MF).</b> Five dual-function configuration inputs. Each pin accepts one of four input voltage levels (VMF1 = 5V, VMF2 = 3.5V, VMF3 = 1.5V, VMF4 = 0V). A simple resistor divider network, as shown in Figure 20 on page 45, is required to establish Mid-level (VMF2 and VMF3) settings. VMF1 and VMF4 (default) settings, can be established with the LXT970A standard power supply and do not require a voltage divider. One voltage divider may be used to drive the MF pins in designs using multiple LXT970A's.                                                  |   |            |                                               |  |  |  |

| 8                 | MF0      |                  | Each MF pin internally drives two different configuration functions. The first function determines the 5-bit address that the LXT970A responds to on the MDIO line. The second function determines a particular operational mode of the LXT970A. Each MF pin also determines the state of a particular bit in the MII registers. The MDDIS input determines if this effect occurs only at initialization (MDDIS = 0) or continuously (MDDIS = 1). The relationship between the input levels and the two configuration functions are shown in Table 8 on page 16 and Table 9 on page 17. |   |            |                                               |  |  |  |

| 7                 | MF1      |                  | The operating functions of MF4, CFGO, and CFG1 change depending on the state of MF0 (Auto-Negotiation enabled or disabled). The functions of MF4, CFG1 and FDE are                                                                                                                                                                                                                                                                                                                                                                                                                      |   |            |                                               |  |  |  |

| 6                 | MF2      | I                | interrelated.<br>The functions of the five MF inputs are as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |            |                                               |  |  |  |

| 5                 | MF3      |                  | Pin MII Address MII Bit Operating Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |            |                                               |  |  |  |

| 4                 | MF4      |                  | MF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 | 0.12       | Auto-Negotiation                              |  |  |  |

|                   |          |                  | MF1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 | 19.13      | Repeater Mode (Disabling DTE Mode)            |  |  |  |

|                   |          |                  | MF2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 | 19.4       | 5B Symbol Mode (Disabling 4B Nibble Mode)     |  |  |  |

|                   |          |                  | MF3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3 | 19.3       | Scrambler Operation (Disabling Scrambler)     |  |  |  |

|                   |          |                  | MF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4 | 4.7<br>4.8 | Auto-Negotiation Enabled - Advertise 100 Mbps |  |  |  |

|                   | 1        | 1                | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 |            | Auto-Negotiation Disabled - Selects TX/FX     |  |  |  |

#### Table 7. LXT970A Hardware Control Interface Signal Descriptions

1. Pin numbers apply to all package types.

I/O Column Coding: I = Input, O = Output, OD = Open Drain, A = Analog.

FDE, CFG0, and CFG1 are affected by the MDDIS input pin. When MDDIS = 0, these inputs determine only the initial state of the function they control. When MDDIS = 1, these inputs provide continuous hardware control over their corresponding functions.

| Pin# <sup>1</sup>      | Pin Name      | I/O <sup>2</sup>     | Signal Description <sup>3</sup>                                                                                                                                                                                                                     |

|------------------------|---------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |               |                      | Full-Duplex Enable.                                                                                                                                                                                                                                 |

|                        |               |                      | When A/N is enabled, FDE determines full-duplex advertisement capability in combination with MF4 and CFG1.                                                                                                                                          |

| 13                     | FDE           | I                    | When A/N is disabled, FDE directly affects full-duplex operation and determines the value of bit 0.8 (Duplex Mode).                                                                                                                                 |

|                        |               |                      | When FDE is High, full-duplex is enabled and $0.8 = 1$ .                                                                                                                                                                                            |

|                        |               |                      | When FDE is Low, full-duplex is disabled and $0.8 = 0$ .                                                                                                                                                                                            |

|                        |               |                      | Configuration Control 0.                                                                                                                                                                                                                            |

|                        |               |                      | When A/N is enabled, Low-to-High transition on CFG0 causes auto-negotiate to re-start and 0.9 = 1.                                                                                                                                                  |

| 14 CFG0 I              |               | I.                   | When A/N is disabled, this input selects operating speed and directly affects bit 0.13.                                                                                                                                                             |

|                        |               |                      | When CFG0 is High, 100 Mbps is selected and $0.13 = 1$ . If FX Operation is selected, this input must be tied High.                                                                                                                                 |

|                        |               |                      | When CFG0 is Low, 10 Mbps is selected and $0.13 = 0$ .                                                                                                                                                                                              |

|                        |               |                      | Configuration Control 1.                                                                                                                                                                                                                            |

|                        |               |                      | When A/N is enabled, CFG1 determines operating speed advertisement capabilities in combination with MF4.                                                                                                                                            |

| 33                     | CFG1          | I                    | When A/N is disabled, CFG1 enables 10 Mbps link test function and directly affects bit 19.8.                                                                                                                                                        |

|                        |               |                      | When CFG1 is High, 10 Mbps link test is disabled and 19.8 = 1.                                                                                                                                                                                      |

|                        |               |                      | When CFG1 is Low, 10 Mbps link test is enabled and 19.8 = 0.                                                                                                                                                                                        |

| 2. I/O Co<br>3. FDE, 0 | CFG0, and ČFG | = Input,<br>1 are af | Age types.<br>O = Output, OD = Open Drain, A = Analog.<br>fected by the MDDIS input pin. When MDDIS = 0, these inputs determine only the initial state<br>(hen MDDIS = 1, these inputs provide continuous hardware control over their corresponding |

#### Table 7. LXT970A Hardware Control Interface Signal Descriptions (Continued)

1, these inputs pr spond ÷у iy functions.

Table 8 summarizes the relationship between input voltage levels (VMF1, VMF2, VMF3, VMF4) and the configuration function for each of the MF input pins. Each MF pin shows two configuration inputs; configuration function and MII address. The initial setting of the corresponding bit is also shown.

#### Table 8. MF Pin Function Settings<sup>1, 3</sup>

|       |                                                                                                                                                                        | Input Voltage Levels <sup>2</sup> |                           |                           |                           |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|---------------------------|---------------------------|--|--|

| Pin   | Function                                                                                                                                                               | Vmf1 (5V)                         | VMF2 (3.5V)               | VMF3 (1.5V)               | VMF4 (0V)                 |  |  |

|       | MII Address Bit 0                                                                                                                                                      | 1                                 | 1                         | 0                         | 0                         |  |  |

| MFO   | Auto-Negotiation<br>Sets the initial value of bit<br>0.12                                                                                                              | Disabled<br>(0.12 = 0)            | Enabled<br>(0.12 = 1)     | Enabled<br>(0.12 = 1)     | Disabled<br>(0.12 = 0)    |  |  |

|       | MII Address Bit 1                                                                                                                                                      | 1                                 | 1                         | 0                         | 0                         |  |  |

|       | Repeater / DTE Mode<br>Sets the initial value of bit<br>19.13                                                                                                          | DTE<br>(19.13 = 0)                | Repeater<br>(19.13 = 1)   | Repeater<br>(19.13 = 1)   | DTE<br>(19.13 = 0)        |  |  |

|       | MII Address Bit 2                                                                                                                                                      | 1                                 | 1                         | 0                         | 0                         |  |  |

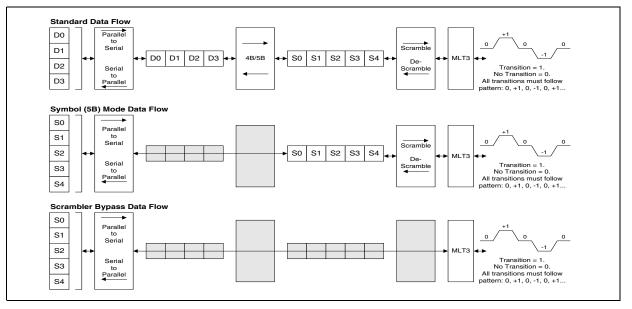

| MF2 N | Nibble (4B) / Symbol (5B) Mode<br>Sets the initial value of bit<br>19.4                                                                                                | Nibble (4B)<br>(19.4 = 0)         | Symbol (5B)<br>(19.4 = 1) | Symbol (5B)<br>(19.4 = 1) | Nibble (4B)<br>(19.4 = 0) |  |  |

|       | MII Address Bit 3                                                                                                                                                      | 1                                 | 1                         | 0                         | 0                         |  |  |

| MF3   | Scrambler Operation<br>Sets the initial value of bit<br>19.3                                                                                                           | Enabled<br>(19.3 = 0)             | Bypassed<br>(19.3 = 1)    | Bypassed<br>(19.3 = 1)    | Enabled<br>(19.3 = 0)     |  |  |

|       | MII Address Bit 4                                                                                                                                                      | 1                                 | 1                         | 0                         | 0                         |  |  |

| MF4   | If Auto-Negotiate Enabled via<br>MF0, MF4 works in combination<br>with CFG1 to control operating<br>speed and duplex advertisement<br>capabilities via bits 4.5 - 4.8. | See Table 9 for details.          |                           |                           |                           |  |  |

|       | If Auto-Negotiate Disabled via<br>MF0, MF4 selects either<br>TX or FX Mode<br>Sets the initial value of bit<br>19.2                                                    | 100TX<br>(19.2 = 0)               | 100FX<br>(19.2 = 1)       | 100FX<br>(19.2 = 1)       | 100TX<br>(19.2 = 0)       |  |  |

3. See Table 12 through Table 14 for operating configuration set-up.

### Table 9. LXT970A Auto-Negotiation Operating Speed/Full-Duplex Advertisement Settings

| Desired Configuration                          | Input       | Value | MDIO Registers |                                                      |

|------------------------------------------------|-------------|-------|----------------|------------------------------------------------------|

| Desired Configuration                          | MF4 CFG1 FD |       | FDE            | MDIO negisters                                       |

| Advertise all capabilities<br>Ignore FDE       | VMF1, VMF4  | Low   | -              | Sets 4.5, 4.6, 4.7 and 4.8 = 1                       |

| Advertise 10 Mbps only<br>Advertise FD         | Vmf1, Vmf4  | High  | High           | Sets 4.5 = 1<br>Sets 4.7 and 4.8 = 0<br>Sets 4.6 = 1 |

| Advertise 10 Mbps only<br>Do Not Advertise FD  |             |       | Low            | Sets 4.5 = 1<br>Sets 4.7 and 4.8 = 0<br>Sets 4.6 = 0 |

| Advertise 100 Mbps only<br>Advertised FD       | Vmf2, Vmf3  | Low   | High           | Sets 4.7 = 1<br>Sets 4.5 and 4.6 = 0<br>Sets 4.8 = 1 |

| Advertise 100 Mbps only<br>Do Not Advertise FD |             |       | Low            | Sets 4.7 = 1<br>Sets 4.5 and 4.6 = 0<br>Sets 4.8 = 0 |

| Advertise 10/100 Mbps<br>Advertise FD          | VMF2, VMF3  | High  | High           | Sets 4.5 and 4.7 = 1<br>Sets 4.6 and 4.8 = 1         |

| Advertise 10/100 Mbps<br>Do Not Advertise FD   |             |       | Low            | Sets 4.5 and 4.7 = 1<br>Sets 4.6 and 4.8 = 0         |

#### 2.0 Functional Description

#### 2.1 Introduction

The LXT970A, a new-generation version of the LXT970 10/100 PHY Fast Ethernet Transceiver incorporates several functional enhancements for a more robust Ethernet solution. The LXT970A supports optional MII driver strength capabilities and link-loss criteria selectable via the MDIO register set.

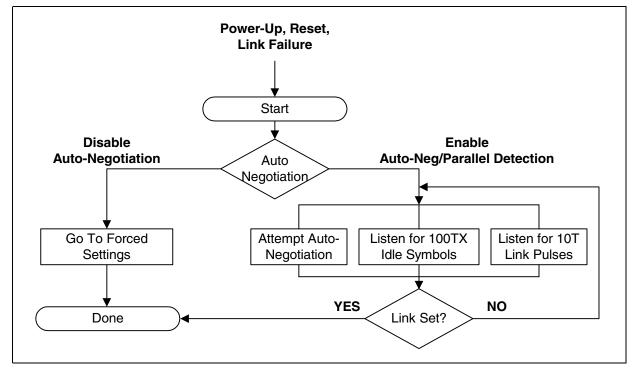

The LXT970A can directly drive a twisted-pair cable for up to 100 meters. The LXT970A also provides a pseudo-ECL interface for driving a 100BASE-FX fiber connection. On power-up, the LXT970A uses auto-negotiation with parallel detection to automatically determine line operating conditions. If the PHY device on the other side of the link supports auto-negotiation, the LXT970A auto-negotiates using Fast Link Pulse (FLP) bursts. If the PHY partner does not support auto-negotiation, the LXT970A automatically detects the presence of either link pulses (10 Mbps PHY) or Idle symbols (100 Mbps PHY) and set its operating speed accordingly. When the line speed selection is made via the parallel detection method, the duplex mode sets to half. The user may later select full-duplex operation by subsequent writes to the appropriate MDIO register. Line operation can also be set using the Hardware Control Interface.

The LXT970A interfaces to a 10/100 MAC through the MII interface. The LXT970A performs all functions of the Physical Coding Sublayer (PCS) and Physical Media Attachment (PMA) sublayer as defined in the IEEE 802.3 100BASE-X specification. It also performs all Physical Media Dependent (PMD) sublayer functions for 100BASE-TX connections. The MII speed is automatically set once line operating conditions have been determined.

See Figure 3 for a typical Network Interface Card (NIC). The LXT970A supports NIC, repeater, and switch applications. It provides half- and full-duplex operation at 100 Mbps and 10 Mbps. The LXT970A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register address (0-6 or 16-20) and Y is the bit number (0:15).

#### 2.2 Interfaces (Network Media/Protocol Support)

The LXT970A provides the following interfaces:

- A Twisted-Pair Interface which directly supports 100BASE-TX and 10BASE-T applications.

- A pseudo-ECL (PECL) Fiber Interface which supports 100BASE-FX applications through an external fiber transceiver.

- An MII (Media Independent Interface) for interfacing 10/100 Media Access Controllers (MACs).

- A Hardware Control Interface to configure various operating characteristics.

#### 2.2.1 Twisted-Pair Interface

The Twisted-Pair Interface directly supports both 100BASE-TX and 10BASE-T applications. The interface is capable of directly driving an RJ-45 interface through magnetics and termination resistors. The interface uses two signal pairs - one for transmit and one for receive. A third output, TREF, connects to the center-tap of the transmit transformer. The same signal pairs, magnetics, and termination resistors are used for both 10 and 100 Mbps operation.

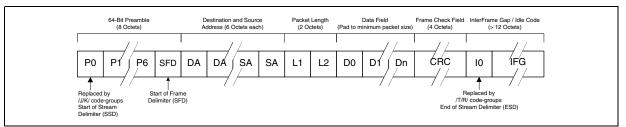

When the LXT970A is operating as a 100 Mbps device, it transmits and receives a 125 Mbps, 5Bencoded, scrambled MLT-3 waveform on this interface. The MLT-3 waveform is continuous. When there is no data to send, "IDLE" symbols are sent and received.

When the LXT970A is operating as a 10 Mbps device, it transmits and receives 10 Mbps Manchester-encoded data. The waveform is not continuous. When there is no data to send, the line is left in an idle state. Link pulses are transmitted periodically to keep the link up.

The LXT970A supports both fixed operation and auto-negotiation with parallel detection on this interface. Fixed operation allows the designer to specify the line speed and duplex mode. With auto-negotiation enabled, the LXT970A automatically determines line speed and duplex state by exchanging capability "pages" with its link partner.

A 4 k $\Omega$  passive load is always present across the twisted-pair inputs. When enabled, the twisted-pair inputs are actively biased to approximately 2.8V.

In applications where the Twisted-Pair Interface is not used, the inputs and outputs may be left unconnected.

The Twisted-Pair Interface is disabled in power down mode, when the Fiber Interface is selected, or when the transmit disconnect (bit 19.0) is set. When the Twisted-Pair Interface is disabled its outputs are tri-stated and inputs are unbiased.

#### 2.2.2 Fiber Interface

The pseudo-ECL Fiber Interface is suitable for driving 100BASE-FX applications through an external fiber transceiver. This interface consists of a transmit and receive pair. The LXT970A sends and receives a continuous 125 Mbps, 5B-encoded NRZI stream on this interface. Scrambling and MLT-3 are not used in fiber connections.

There is no industry standard for auto-negotiation on 100BASE-FX. The LXT970A only supports forced operation on the Fiber Interface. The LXT970A does not support 10FL (10 Mbps fiber) applications.