## Intel<sup>®</sup> 80321 I/O Processor

**Specification Update**

May 12, 2003

**Notice:** The Intel<sup>®</sup> 80321 I/O processor (80321) may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 80321 I/O processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright© Intel Corporation, 2003

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel Insuiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetStructure, Intel Play, Intel Play, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

# int<sub>e</sub>l<sub>®</sub> Contents

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 6  |

| Summary Table of Changes     | 7  |

| Identification Information   | 11 |

| Core Errata                  | 13 |

| Non-Core Errata              | 27 |

| Specification Changes        | 34 |

| Specification Clarifications | 35 |

| Documentation Changes        | 36 |

## This page intentionally left blank.

I

## **Revision History**

| Date           | Version | Description                                                                                                                                                                                                  |

|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 13, 2003   | 010     | Added Specification Clarifications 7.                                                                                                                                                                        |

|                |         | Revised Non-Core Errata 3.                                                                                                                                                                                   |

|                |         | Added Non-Core Errata 17.                                                                                                                                                                                    |

| May 2003       | 009     | Added Specification Clarifications 6.                                                                                                                                                                        |

|                |         | Added Document Change 12.                                                                                                                                                                                    |

|                |         | <ul> <li>Removed C-0 Step column from Core Errata, Non-Core Errata, Specification<br/>Changes, Specification Clarifications, Die Details, Device ID Registers. Not<br/>planned to be implemented.</li> </ul> |

| November 2002  | 008     | Updated Status indicators in Core Errata and Non-Core Errata.                                                                                                                                                |

|                |         | Added Specification Change 3.                                                                                                                                                                                |

|                |         | Added Specification Clarifications 4 and 5.                                                                                                                                                                  |

| September 2002 | 007     | <ul> <li>Removed Specification Clarification 3. It does not apply to the Intel<sup>®</sup> 80321<br/>I/O processor.</li> </ul>                                                                               |

|                |         | Added B-1 Stepping Column.                                                                                                                                                                                   |

|                |         | Added Core Errata 19 through 21.                                                                                                                                                                             |

|                |         | Reworded Non-Core Errata 4.                                                                                                                                                                                  |

| August 2002    | 000     | <ul> <li>Added two Diagrams at end of Non-Core Errata 9.</li> </ul>                                                                                                                                          |

| August 2002    | 006     | Added Non-Core Errata 15 and 16.                                                                                                                                                                             |

|                |         | Reworded Specification Change 1.                                                                                                                                                                             |

|                |         | Added Specification Clarification 3.                                                                                                                                                                         |

|                |         | Revised Die Details and Device ID Registers.                                                                                                                                                                 |

|                |         | Added Non-Core Errata 13 and 14.                                                                                                                                                                             |

| June, 2002     | 005     | Added Specification Clarifications 1 and 2.                                                                                                                                                                  |

| 00110, 2002    | 005     | <ul> <li>Document Changes 1 and 4 through 11 are now incorporated in the latest<br/>Design Guide revision.</li> </ul>                                                                                        |

|                |         | Added Core Errata 18 and Specification Changes 1 and 2.                                                                                                                                                      |

|                |         | <ul> <li>Added notes to Core Erratum 13 and 14 and edited workaround for<br/>Non-Core Errata 10.</li> </ul>                                                                                                  |

|                |         | Deleted previous Core Errata 12.                                                                                                                                                                             |

| April 11, 2002 | 004     | <ul> <li>Added Intel® 80321 I/O Processor Advance Information Datasheet to<br/>related/affected documents</li> </ul>                                                                                         |

|                |         | • Changed steppings for the fixes of Non-Core Errata 2, 3, 4, 7, 8, 9, 10, 11, and 12.                                                                                                                       |

|                |         | <ul> <li>Added Die Details and Device ID Registers for B-0 stepping.</li> </ul>                                                                                                                              |

|                |         | Added Core Errata 12 and 14 (rearranged other numbering to fit new order)                                                                                                                                    |

| March 26, 2002 |         | Added Non-Core Errata 8 through 12.                                                                                                                                                                          |

|                | 003     | Revised Non-Core Errata 2 through 7.                                                                                                                                                                         |

|                | 005     | Rearranged Document Change order to reflect sequential page flow.                                                                                                                                            |

|                |         | Added Document Change 2.                                                                                                                                                                                     |

|                |         | Renumbered old Document Change 10 to 3.                                                                                                                                                                      |

| March 14, 2002 | 002     | Added Non-Core Errata 7.                                                                                                                                                                                     |

| March 14, 2002 | 002     | Added Document Changes 1 through 3.                                                                                                                                                                          |

| February 2002  | 001     | Initial Release.                                                                                                                                                                                             |

## **Preface**

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### **Affected Documents/Related Documents**

| Title                                                                | Order  |

|----------------------------------------------------------------------|--------|

| Intel <sup>®</sup> 80321 I/O Processor Developer's Manual            | 273517 |

| Intel <sup>®</sup> 80321 I/O Processor Advance Information Datasheet | 273518 |

| Intel <sup>®</sup> 80321 I/O Processor Design Guide                  | 273520 |

#### Nomenclature

T

**Errata** are design defects or errors. These may cause the Product Name's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

## **Summary Table of Changes**

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the Product Name product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

#### **Codes Used in Summary Table**

#### Stepping

| X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| (No mark)       |                                                                                                               |

| or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| (Page):         | Page location of item in this document.                                                                       |

| Doc:            | Document change or update will be implemented.                                                                |

| PlanFix:        | This erratum may be fixed in a future stepping of the product.                                                |

| Fixed:          | This erratum has been previously fixed.                                                                       |

| NoFix:          | There are no plans to fix this erratum.                                                                       |

|                 |                                                                                                               |

#### Row

Page

**Status**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### **Core Errata**

| No. | Steppings |            | Steppings  |      | Status | Errata                                                                                                                             |  |  |

|-----|-----------|------------|------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | A-0       | <b>B-0</b> | <b>B-1</b> | Page | Status | Elfata                                                                                                                             |  |  |

| 1   | Х         | Х          | Х          | 14   | NoFix  | Boundary Scan Is Not Fully Compliant to the IEEE 1149.1 Specification                                                              |  |  |

| 2   | Х         | Х          | Х          | 14   | NoFix  | Drain Is Not Flushed Correctly when Stalled in the Pipeline                                                                        |  |  |

| 3   | х         | Х          | Х          | 15   | NoFix  | Undefined Data Processing-'like' Instructions are Interpreted as an MSR Instruction                                                |  |  |

| 4   | Х         | Х          | Х          | 15   | NoFix  | Debug Unit Synchronization with the TXRXCTRL Register                                                                              |  |  |

| 5   | Х         | Х          | Х          | 15   | NoFix  | Extra Circuitry Is Not JTAG Boundary Scan Compliant                                                                                |  |  |

| 6   | х         | Х          | х          | 16   | NoFix  | Incorrect Decode of Unindexed Mode, Using Addressing Mode 5, Can Corrupt<br>Protected Registers                                    |  |  |

| 7   | Х         | Х          | Х          | 16   | NoFix  | Load Immediately Following a DMM Flush Entry is Also Flushed                                                                       |  |  |

| 8   | Х         | Х          | Х          | 16   | NoFix  | Trace Buffer Does Not Operate Below 1.3 V                                                                                          |  |  |

| 9   | Х         | Х          | Х          | 16   | NoFix  | Data Cache Unit Can Stall for a Single Cycle                                                                                       |  |  |

| 10  | Х         | Х          | Х          | 17   | NoFix  | Aborted Store that Hits the Data Cache May Mark Writeback Data As Dirty                                                            |  |  |

| 11  | х         |            |            | 18   | Fixed  | CP15 Data Cache Unlock Command Can Cause Unlock in User Mode or when<br>Flushed from the Pipe in Supervisor Mode                   |  |  |

| 12  | х         |            |            | 19   | Fixed  | Store to Cacheable Memory, Interrupted by an Exception, May Inadvertently Write to Memory                                          |  |  |

| 13  | х         |            |            | 21   | Fixed  | Data Cache Dirty Bits May be Corrupted when a Line Invalidate is Followed<br>Immediately by a Store                                |  |  |

| 14  | х         |            |            | 22   | Fixed  | Data cache dirty bits may be Corrupted when a Bus Error on a Cache Line Fill is Followed Immediately by a Store                    |  |  |

| 15  | х         | Х          | х          | 23   | NoFix  | Performance Monitor Unit Event 0x1 Can Be Incremented Erroneously by Unrelated Events                                              |  |  |

| 16  | х         | Х          | х          | 23   | NoFix  | In Special Debug State, Back-to-Back Memory Operations Where the First<br>Instruction Aborts May Cause a Hang                      |  |  |

| 17  | х         |            |            | 24   | Fixed  | Instruction Memory Management Unit Address Translation is Turned Off for the<br>First Fetch After Exiting Special Debug State      |  |  |

| 18  | х         |            |            | 25   | Fixed  | Data cache dirty bits may be corrupted when a store to cacheable memory occurs during a tag replacement for a different cache line |  |  |

| 19  | х         | Х          | х          | 28   | NoFix  | Accesses to the CP15 ID register with opcode2 > 0b001 returns unpredictable values                                                 |  |  |

| 20  | х         | Х          | х          | 28   | NoFix  | Disabling and re-enabling the MMU can hang the core or cause it to execute the wrong code                                          |  |  |

| 21  | Х         | Х          | Х          | 29   | NoFix  | Updating the JTAG parallel register requires an extra TCK rising edge                                                              |  |  |

### **Non-Core Errata**

| No. | Steppings |            | teppings |      | Steppings |                                                                                                                                                                                                                         | Steppings | Steppings |  | Status | Errata |

|-----|-----------|------------|----------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|--|-----------|--|-----------|--|-----------|--|-----------|--|-----------|--|-----------|--|--------|--------|

| NO. | A-0       | <b>B-0</b> | B-1      | Page | Status    | Lindu                                                                                                                                                                                                                   |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 1   | Х         | Х          | Х        | 30   | NoFix     | The SSP TXD Does Not Retain the Value of the Last Bit Transferred                                                                                                                                                       |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 2   | х         | Х          | х        | 30   | NoFix     | The ATU Returns Invalid Data for the DWORD that Target Aborted from the MCU when Using 32-Bit Memory, ECC Enabled and in PCI Mode                                                                                       |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 3   | Х         | Х          | Х        | 30   | NoFix     | PBI Issue When Using 16-bit PBI Transactions in PCI Mode                                                                                                                                                                |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 4   | Х         | Х          | Х        | 31   | NoFix     | All-zero Result Buffer" for the AAU is not Implemented                                                                                                                                                                  |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 5   | Х         | Х          | Х        | 31   | NoFix     | MCU Pointers are Incorrect following a Restoration from a Power Fail                                                                                                                                                    |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 6   | х         | Х          | Х        | 31   | NoFix     | PMU Does Not Account for when the Arbiter Deasserts GNT# One Cycle before FRAME#                                                                                                                                        |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

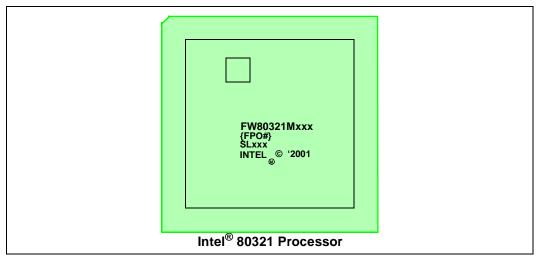

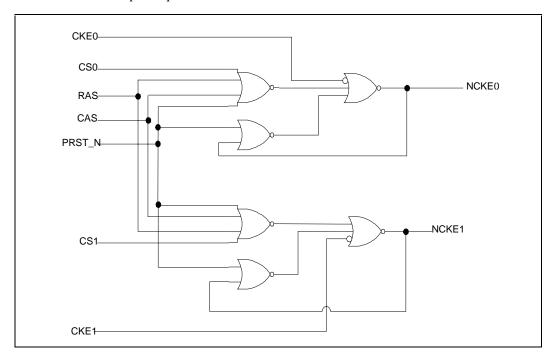

| 7   | Х         |            |          | 32   | Fixed     | SCKE[1:0] Contention During a Power Failure                                                                                                                                                                             |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

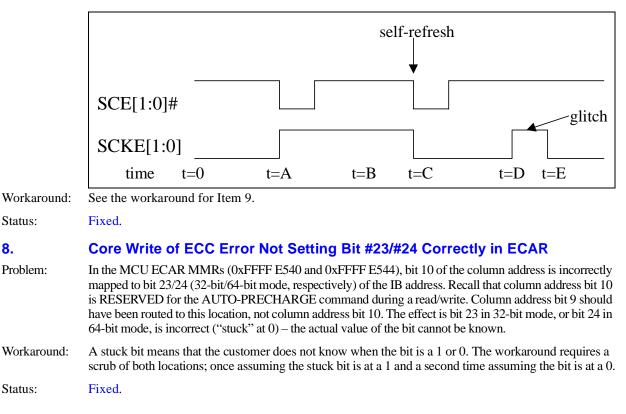

| 8   | Х         |            |          | 32   | Fixed     | Core Write of ECC Error Not Setting Bit #23/#24 Correctly in ECAR                                                                                                                                                       |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 9   | Х         |            |          | 33   | Fixed     | Improper Power Fail Sequence During a Power Failure                                                                                                                                                                     |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 10  | Х         |            |          | 35   | Fixed     | PLL Unable to Lock at Reset                                                                                                                                                                                             |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 11  | Х         | Х          | Х        | 36   | NoFix     | Lost Data During Bursts of Large Number of Partials with 32-bit ECC Memory                                                                                                                                              |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 12  | Х         |            |          | 36   | Fixed     | P_RST# to PCI-X Initialization Pattern Hold Time (Tprh)                                                                                                                                                                 |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 13  | Х         | Х          | Х        | 37   | NoFix     | The MTTR1 (Core Multi-Transaction Timer) is not operating due to improper behavior of the core internal bus request signal (REQ#)                                                                                       |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 14  | Х         | Х          | Х        | 37   | NoFix     | The MCU supports a page size of 2 Kbytes for 64-bit mode                                                                                                                                                                |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 15  | х         | х          |          | 38   | Fixed     | A logic error in the Memory Controller Unit (MCU) incorrectly reports an ECC Error on memory writes. This error does not corrupt memory contents or data. There are two different conditions that exacerbate the issue. |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 16  | Х         | Х          |          | 42   | Fixed     | Intel® 80321 I/O Processor/PCI-X Bridge Unexpected Split Completion Error                                                                                                                                               |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

| 17  | Х         | Х          |          | 43   | NoFix     | Vih Minimum Input High Voltage (Vih) level for the PCI pins                                                                                                                                                             |           |           |  |           |  |           |  |           |  |           |  |           |  |           |  |        |        |

Т

T

### **Specification Changes**

| No. | Steppings |   | gs         | Page | Specification Changes                                                                                             |  |  |

|-----|-----------|---|------------|------|-------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | A-0 B-0   |   | <b>B-1</b> | raye | Specification changes                                                                                             |  |  |

| 1   | х         | х | х          |      | DDR $\rm V_{CC}$ and DDR $\rm V_{REF}$ minimum specifications need to be changed on the A-0 and B-0/B-1 steppings |  |  |

| 2   | Х         | Х | Х          | 44   | DDR SDRAM signal timing change, T <sub>VA3</sub>                                                                  |  |  |

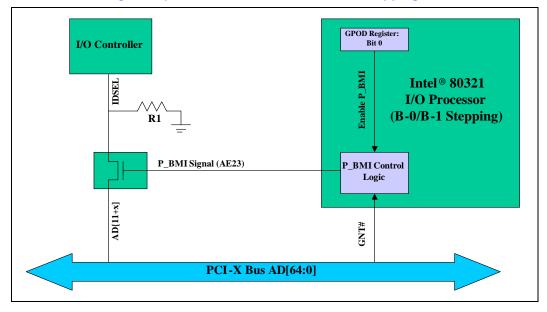

| 3   | Х         | Х | Х          | 45   | P_BMI (AE23) added to B-0/B-1 Steppings                                                                           |  |  |

### **Specification Clarifications**

| No. | Steppings |            | Steppings |      | Status | Specification Clarifications                                                                                                                                                          |  |

|-----|-----------|------------|-----------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | A-0       | <b>B-0</b> | B-1       | Page | Status | Specification Granifications                                                                                                                                                          |  |

| 1   | x         | х          | х         | 47   | NoFix  | The Intel® 80321 I/O processor is compliant with the PCI Local Bus Specification, Revision 2.2 but it is not compliant with PCI Local Bus Specification, Revision 2.3                 |  |

| 2   | x         | х          | х         | 47   | NoFix  | Modifications to the Hot-Debug procedure are necessary for the<br>Intel <sup>®</sup> 80321 I/O processor when flat memory mapping is not<br>used (Virtual Address = Physical Address) |  |

| 3   | Х         | Х          | Х         | 47   | Doc    | Removed. Does not apply to the Intel <sup>®</sup> 80321 I/O processor.                                                                                                                |  |

| 4   | Х         | Х          | Х         | 48   | Doc    | BAR0 Configuration When Using the Messaging Unit (MU)                                                                                                                                 |  |

| 5   | Х         | Х          | Х         | 48   | Doc    | Reading Unpopulated SDRAM Memory Banks                                                                                                                                                |  |

| 6   | х         | Х          | х         | 48   | Doc    | 32-bit Writes-to-Unaligned 64-bit Addresses, are Promoted to 64-bit Aligned Writes                                                                                                    |  |

| 7   | х         | Х          | х         | 49   | Doc    | In-order Delivery not guaranteed for data blocks described by a single DMA descriptor                                                                                                 |  |

### **Documentation Changes**

| No. | Document Revision | Page | Status   | Documentation Changes                                                                    |

|-----|-------------------|------|----------|------------------------------------------------------------------------------------------|

| 1   | 273520-002        | 49   | In Guide | Table 4 Page 18 second row has incorrect data                                            |

| 2   | 273518-001        | 49   | Doc      | Table 9 (Sheet 3 of 5), page 31 and Table 10 (Sheet 5 of 5), page 38 have incorrect data |

| 3   | 273518-001        | 49   | Doc      | Table 10 (Sheet 2 of 5), page 35 has incorrect data                                      |

| 4   | 273520-001        | 49   | In Guide | Section 6.2.2 on page 37 has incorrect data                                              |

| 5   | 273520-002        | 50   | In Guide | Figure 14 on page 40 has missing text                                                    |

| 6   | 273520-002        | 50   | In Guide | Table 18, page 61 has missing data and incorrect data                                    |

| 7   | 273520-002        | 51   | In Guide | Section 7.6.1 page 75 has incorrect data                                                 |

| 8   | 273520-002        | 51   | In Guide | Section 7.6.1 page 76 has incorrect data                                                 |

| 9   | 273520-002        | 51   | In Guide | Section 7.6.1 page 77 has incorrect data                                                 |

| 10  | 273520-002        | 51   | In Guide | Section 7.6.3 page 78 has missing data and incorrect data                                |

| 11  | 273520-002        | 52   | In Guide | Section 14.1 page 113 has missing data                                                   |

| 12  | 273518-001        | 52   | Doc      | Channel Control Register; Channel Enable, page 248                                       |

T

## **Identification Information**

### **Markings**

#### **Topside Markings**

#### **Die Details**

| Stepping | Part Number | QDF (Q)/<br>Specification<br>Number (SL) | Voltage<br>(V) | Intel <sup>®</sup><br>80321 I/O<br>Processor<br>Speed<br>(MHz) | Notes                     |

|----------|-------------|------------------------------------------|----------------|----------------------------------------------------------------|---------------------------|

| A-0      | FW80321M400 | Q237                                     | 3.3            | 400                                                            | Samples - limited testing |

| A-0      | FW80321M600 | Q238                                     | 3.3            | 600                                                            | Samples - limited testing |

| A-0      | FW80321M400 | Q359                                     | 3.3            | 400                                                            | Samples                   |

| A-0      | FW80321M600 | Q284                                     | 3.3            | 600                                                            | Samples                   |

| A-0      | FW80321M400 | Q285                                     | 3.3            | 400                                                            | General Samples           |

| A-0      | FW80321M600 | Q286                                     | 3.3            | 600                                                            | General Samples           |

| A-0      | FW80321M400 | SL5PC                                    | 3.3            | 400                                                            | Production Material       |

| A-0      | FW80321M600 | SL5PD                                    | 3.3            | 600                                                            | Production Material       |

| B-0      | FW80321M400 | Q377                                     | 3.3            | 400                                                            | Samples - limited testing |

| B-0      | FW80321M600 | Q379                                     | 3.3            | 600                                                            | Samples - limited testing |

| B-0      | FW80321M400 | Q378                                     | 3.3            | 400                                                            | General Samples           |

| B-0      | FW80321M600 | Q380                                     | 3.3            | 600                                                            | General Samples           |

| B-0      | FW80321M400 | Q385                                     | 3.3            | 400                                                            | General Samples           |

| B-0      | FW80321M600 | Q386                                     | 3.3            | 600                                                            | General Samples           |

| B-0      | FW80321M400 | SL69L                                    | 3.3            | 400                                                            | Production Material       |

| B-0      | FW80321M600 | SL69M                                    | 3.3            | 600                                                            | Production Material       |

| B-1      | FW80321M400 | Q464                                     | 3.3            | 400                                                            | Samples - limited testing |

| B-1      | FW80321M600 | Q465                                     | 3.3            | 600                                                            | Samples - limited testing |

| B-1      | FW80321M400 | Q466                                     | 3.3            | 400                                                            | General Samples           |

| B-1      | FW80321M600 | Q467                                     | 3.3            | 600                                                            | General Samples           |

| B-1      | FW80321M400 | SL6R2                                    | 3.3            | 400                                                            | Production Material       |

| B-1      | FW80321M600 | SL6R3                                    | 3.3            | 600                                                            | Production Material       |

### **Device ID Registers**

| Device and<br>Stepping | Processor Device ID<br>(CP15, Register0 - opcode_2=0) | ATU<br>Device ID<br>(ATUDID) | ATU<br>Revision ID<br>(ATURID) | JTAG<br>Device ID |

|------------------------|-------------------------------------------------------|------------------------------|--------------------------------|-------------------|

| A-0 (400 MHz)          | 0x69052420                                            | 0x0318                       | 0x00                           | 0x09266013        |

| A-0 (600 MHz)          | 0x69052430                                            | 0x0319                       | 0x00                           | 0x09267013        |

| B-0 (400 MHz)          | 0x69052C21                                            | 0x0318                       | 0x01                           | 0x19266013        |

| B-0 (600 MHz)          | 0x69052C31                                            | 0x0319                       | 0x01                           | 0x19267013        |

| B-1 (400 MHz)          | 0x69052C22                                            | 0x0318                       | 0x02                           | 0x29266013        |

| B-1 (600 MHz)          | 0x69052C32                                            | 0x0319                       | 0x02                           | 0x29267013        |

## int<sub>ط</sub> Core Errata

#### Boundary Scan Is Not Fully Compliant to the IEEE 1149.1 Specification

Problem:

1.

The IEEE Standard 1149.1 specifies the boundary scan logic to support two main goals:

- 1. To allow the interconnections between the various components to be tested, test data can be shifted into all the boundary-scan register cells associated with component output pins and loaded in parallel through the component interconnections, into those cells associated with inputs pins; and

- 2. To allow the components on the board to be tested, the boundary-scan register can be used as a means of isolating on-chip system logic from stimuli received from surrounding components, while an internal self-test is performed. Alternatively, when the boundary-scan register is suitably designed, it can permit a limited slow-speed static test of the on-chip system logic, since it allows delivery of test data to the component and examination of the test results. (IEEE std. 1149.1-1990, page 1-5)

The Intel<sup>®</sup> Xscale<sup>TM</sup> core does not support the second goal, because it does not support the optional INTEST or RUBIST instructions. The Intel<sup>®</sup> Xscale<sup>TM</sup> core is not required to provide these instructions, however, since it doesn't, this makes the following statement practically invalid.

The IEEE std. 1149.1 description of the SAMPLE/PRELOAD instruction states that, "When the SAMPLE/PRELOAD instruction is selected, the state of all signals flowing through system pins (input or output) shall be loaded into the boundary scan register on the rising edge of the TCK in the Capture-DR controller state." (Page 7-8).

The boundary scan cells of the Intel<sup>®</sup> Xscale<sup>TM</sup> core bi-directional pads, do not capture the data driven from the on-chip system logic to the pins, when these pads are acting as outputs. This would only be useful when trying to capture the data driven from the on-chip logic, during normal operation of the assembled board. However, the Intel<sup>®</sup> Xscale<sup>TM</sup> core does not allow single stepping of its clocks. Thus, even when the Intel<sup>®</sup> Xscale<sup>TM</sup> core did provide the compliant boundary scan cell, it would be extremely difficult (or impossible) to synch the boundary scan logic with the state of the on-chip logic. Therefore, this feature of the boundary scan cells is not useful. This has NO effect on the ability to determine the integrity of the interconnections on boards, which is what the Intel<sup>®</sup> Xscale<sup>TM</sup> core boundary scan logic was designed to support.

Workaround: No workaround.

Status: NoFix.

#### 2. Drain Is Not Flushed Correctly when Stalled in the Pipeline

- Problem: In a load followed by a drain scenario, the load table walks and then gets a precise data abort. The core fetches the address for the abort handler, but in the same cycle does not flush the drain.

- Implication: Not a functional problem, but may effect performance.

- Workaround: No workaround.

- Status: NoFix.

### 3. Undefined Data Processing-'like' Instructions are Interpreted as an MSR Instruction

Problem: The instruction decode allows undefined opcodes, which look similar to the MSR (Move to Status register from an ARM register) instruction, to be interpreted as an MSR instruction. The mis-decoded MSR instruction also adds a SUBNV PC,0x4 to the instruction flow.

| Workaround: Do not use undefined opcodes of this form: | Workaround: | Do not use undefined opcodes of this form: |  |

|--------------------------------------------------------|-------------|--------------------------------------------|--|

|--------------------------------------------------------|-------------|--------------------------------------------|--|

| 3 | 1 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| - |   | -  | -  | -  | 0  | 0  | 0  | 1  | 0  | -  | 1  | 0  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | - | - | 0 | 0 | 1 | 0 | - | - | - | - |

| - |   | -  | -  | -  | 0  | 0  | 0  | 1  | 0  | -  | 1  | 0  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | - | - | 0 | 1 | 0 | 0 | - | - | - | - |

| - |   | -  | -  | -  | 0  | 0  | 0  | 1  | 0  | -  | 1  | 0  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | - | - | 0 | 1 | 1 | 0 | - | - | - | - |

Status: NoFix.

#### 4. Debug Unit Synchronization with the TXRXCTRL Register

- Problem: The RX bit in the TXRXCTRL (TX/RX Control) register comes from the JTAG clock domain to the core clock domain, and several cycles are needed for the register in the core clock domain to update. During this time, a debugger, which is running a fast JTAG clock relative to the core clock, may read the bit before it updates in the register, thus reading the old value.

- Workaround: The JTAG clock should be slower than the core clock.

Status: NoFix.

#### 5. Extra Circuitry Is Not JTAG Boundary Scan Compliant

- Problem: The IEEE 1149.1 (JTAG) specification states that, "when the HIGHZ instruction is selected, all system logic outputs.... shall immediately be placed in an inactive drive state". The JTAG unit on the core creates an internal 'float' signal, which is driven to the I/O pads. This signal is derived from the HIGHZ instruction; however, the HIGHZ instruction gets flopped by a rising edge of TCK first, before it is able to 'float' the pads. This is in violation of the JTAG specification, specifically the term "immediately". It is possible for TCK to stop after the HIGHZ instruction is loaded and thus the pads may never 'float'.

- Workaround: Do not stop the JTAG clock (TCK).

| 6.          | Incorrect Decode of Unindexed Mode, Using Addressing Mode 5, Can<br>Corrupt Protected Registers                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Problem:    | The instruction decoder incorrectly decodes the valid combination of $P=0$ , $U=1$ and $W=0$ , when using unindexed mode in addressing mode 5 (load and store coprocessor). In this case, the LDC or STC should produce consecutive address loads or stores, with no base update until the coprocessor signals that it has received enough data. Instead, the instruction gets separated into an LDR/STR and a CP access.                                                                        |  |  |  |  |  |  |  |  |

|             | The LDR/STR gets decoded as a post-index address, updating the base register. Due to the decoding as post-index, the 'option' bits, normally reserved for the coprocessor in unindexed mode, become the 8-bit offset value used in the base register update calculation.                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|             | The implication is, that protected registers can be corrupted. This errata can cause the corruption of FIQ registers, R13-R14, in user and system modes when the LDC instruction is executed using unindexed addressing mode. It can also cause the corruption of FIQ registers, R8-R12, in any mode, when the LDC instruction is executed using unindexed addressing. The R13 register in debug mode may also be corrupted during an LDC in any mode. In the case of STC, only Rn is corrupted. |  |  |  |  |  |  |  |  |

|             | Unexpected memory accesses can also occur. In the case of an LDC, any memory location may be accessed, since the FIQ registers may be improperly used as the base register. In the case of an STC, the memory word located at Rn+4 is corrupted. This is the memory location immediately following the locations which should be modified by STC unindexed.                                                                                                                                      |  |  |  |  |  |  |  |  |

| Workaround: | Do not use unindexed addressing in addressing mode 5 – Load and Store Coprocessor.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Status:     | NoFix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 7.          | Load Immediately Following a DMM Flush Entry is Also Flushed                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Problem:    | A load that immediately follows a data memory management (DMM) flush entry command, that also hits the data TLB, is also flushed. Therefore, the instruction immediately following the flush, is also flushed from the data TLB.                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Workaround: | All flush entry commands to the data TLB must be followed by two NOPs. The first ensures the erratum is not encountered, and the second ensures the speed path is not hit.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Status:     | NoFix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 8.          | Trace Buffer Does Not Operate Below 1.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Problem:    | The trace buffer within the debug unit is not guaranteed to operate, due to voltage sensitivity, when the core voltage supply is below 1.3 V.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Workaround: | Make sure the voltage is above 1.3 V during debug.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Status:     | NoFix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 9.          | Data Cache Unit Can Stall for a Single Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Problem:    | When the data cache unit retries an operation that is in the pending buffer, a single cycle stall occurs.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Workaround: | No workaround. This is a performance issue only.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Status:     | NoFix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

#### 10. Aborted Store that Hits the Data Cache May Mark Writeback Data As Dirty

Problem:

When there is an aborted store that hits clean data in the data cache (data in an aligned four word range, that has not been modified from the core, since it was last loaded in from memory or cleaned), the data in the array is not modified (the store is blocked), but the dirty bit is set.

When the line is then aged out of the data cache or explicitly cleaned, the data in that four word range is evicted to external memory, even though it has never been changed. In normal operation, this is nothing more than an extra store on the bus, that writes the same data to memory as is already there.

Here is the boundary condition where this might be visible:

- 1. a cache line is loaded into the cache at address A

- 2. another master externally modifies address A

- 3. a core store instruction attempts to modify A, hits the cache, aborts because of MMU permissions, and is backed out of the cache. That line should not be marked dirty, but because of this errata is marked as dirty.

- 4. the cache line at A then ages out or is explicitly cleaned. The original data from location A is evicted to external memory, overwriting the data written by the external master.

This only happens when software is allowing an external master to modify memory, that is, writeback or write-allocate in the page tables, and depending on the fact that the data is not 'dirty' in the cache, to preclude the cached version from overwriting the external memory version. When there are any semaphores or any other handshaking to prevent collisions on shared memory, this should not be a problem.

Workaround: For this shared memory region, mark it as write-through memory in the page table. This prevents the data from ever being written out as dirty.

## 11. CP15 Data Cache Unlock Command Can Cause Unlock in User Mode or when Flushed from the Pipe in Supervisor Mode

Problem: Correct behavior for the "unlock data cache" command (MCR p15, 0, Rd, c9, c2, 1), issued in user mode, is to generate an invalid instruction exception and not affect the state of the cache. Instead, the exception is generated, but the cache is unlocked anyway. In this case, the illegal instruction event is generated. When the OS does not attempt to recover from illegal instructions, this erratum is no issue.

A secondary effect of this erratum, iMs that even in a privileged mode, when an instruction should execute, the data cache unlock hardware activity can occur while the actual MCR instruction is still in the execution pipeline. When an interrupt or some other event causes the instruction to be flushed from the pipe, the hardware activity may still occur. It is likely that the instruction executes shortly after returning from the handler, so unlocking the cache early probably is not an issue, unless the event handler code makes an assumption about data cache locking.

Workaround: When user mode code is well controlled, the OS can detect that user code did the illegal operation and report the error for software debugging purposes. Then re-code the user application and try again.

When code deliberately trying to crash the machine is a concern, here are possible ways to recover when the cache is unlocked in user mode:

- 1. When data cache locking is used with the knowledge of the OS, to keep local copies of external data for performance, it is possible, for the OS to fix things. The OS detects that the invalid instruction fault was caused by a coprocessor 15 operation, cleans out the cache, and relocks the data that was supposed to be locked. The offending user application should be terminated.

- 2. When data cache locking is used as SRAM as part of the data cache (allocated with the data cache line operation, rather than loading in existing memory), it is difficult for the machine to recover. When any of the SRAM locations are evicted, external memory at a random location can be corrupted. One solution is to immediately turn off the data cache at the beginning of the invalid instruction event handler to avoid evictions in the cache. The SRAM contents can then be copied to scratch memory, the cache cleaned and invalidated, and the SRAM reallocated and locked. At that point, the contents can be copied back in and operation can continue.

When early unlocking of the data cache in privileged modes is a concern, the following software workarounds exist:

- 1. Disable interrupts before unlocking the data cache, and ensure that no abort conditions exist around the unlock code. Imprecise external data aborts and parity errors are still potential issues, when software attempts to recover from these situations.

- 2. Do not make assumptions about data cache lock state in the event handlers. When the event handler code does not require access to locked data cache regions, the early unlock is transparent, as the unlock MCR is executed once the handler is finished.

Status: Fixed.

### 12. Store to Cacheable Memory, Interrupted by an Exception, May Inadvertently Write to Memory

Problem:

In some cases, when a store to a cacheable region of memory occurs simultaneously with an exception, the store is not properly cancelled and may update memory. This may occur even when the store did not have permission to write to that memory region, and no data abort is recorded at the time memory is incorrectly modified. It is important that developers review this erratum and assess the impact to their specific application to ensure that no potential exists for data corruption.

This combination of events required for the erratum to occur:

- 1. A memory operation occurs that requires a cache line fill, which in-turn causes a cache line eviction. For example, a load or prefetch.

- 2. A few cycles later, an exception event occurs. The following exception events cause the erratum:

- a. interrupt

- b. prefetch abort

- c. instruction breakpoint

- d. invalid opcode fault

- e. imprecise data abort

- A precise data abort may not cause the erratum.

- 3. The instruction which is being flushed by the exception event is a store to write-back memory, and the store address coincides with the cache line that is being evicted to make room for the cache line fill.

- 4. Returning data on the bus causes a data cache stall at a specific cycle.

#### Result:

The store writes to memory when it should not. When the store is to write-back memory, the cache line is evicted and external memory is incorrectly updated as when that store had occurred. The exception return points to the store instruction.

When the store is to write-through memory, the store instruction is properly flushed and external memory is not updated.

Memory access permissions are not checked before the store updates the cache. This means the store may change memory without permission and without taking an abort.

When the store did a pre- or post-index update on its address, the register file correctly flushes the update. This means that when the store is executed on return from the exception, correct data is stored into memory at the correct address.

#### **Example Manifestations:**

The following examples explain how the erratum may manifest itself. The examples are intended to help developers assess the impact upon their applications.

- *Note:* This is not an exhaustive list, there may be other examples depending upon how specific the architecture of the application code is.

- 1. Copy on Write -

In a multi-tasking OS, a process has read access to a shared memory region, but not write access. Upon a write, the data abort handler creates a physical copy of that region and allow write access to that new region.

In the failing case, the shared read-only region can be updated incorrectly and without a data abort. Eventually, when the original process is returned to, a data abort happens, but the problem is that the memory has already been corrupted. Linux supports Copy on Write and when activated, can experience the erratum. Other OSs may also be affected.

2. Flags to memory shared with interrupt handler -

When there is a flag used to communicate between a process and the interrupt handler, and the store to set the flag is being set by the store that is interrupted, the interrupt handler may see the flag set, do the required work, and clear the flag. Upon return to the

interrupted process, the store instruction would be executed and the flag set. The interrupted process would incorrectly assume that the interrupt handler had not yet seen that flag and serviced it. This flag error can also occur between two task switched processes.

3. Debug -

Instruction breakpoints and prefetch aborts on a store can cause the erratum. When a user is single stepping through code, stops with an instruction breakpoint on a store, and then checks external memory for the pre-store value of the address the store is about to write to, the debugger may see the post store value.

- Workaround: The global workaround for the erratum would be to disable write-back cache within the application. This ensures the erratum does not manifest itself. However, it is understood that this can be cumbersome in performance-sensitive applications. As an alternative, developers may simply prevent the conditions from occurring simultaneously which would cause the erratum to be manifested. By preventing these conditions, one effectively has implemented a workaround.

- 1. Disable write-back cache. This can apply to Linux-based applications due to the fact that Linux utilizes copy-on-write.

- 2. Enable write-back cache and insure the code does not allow the simultaneous occurrence of the conditions required to manifest the erratum.

Here are some workaround options for the specific examples listed above:

1. Copy on Write -

This section is concerned with permissions as applied to first Linux\* and then to an embedded real-time controller. In Linux, Copy on Write, is a memory allocation technique used to provide a performance boost. The erratum can be avoided by setting the caching policy for a copy-on-write read-protected page to write-through. There is no memory access penalties because the memory is read-only. When a write occurs and a write-able copy is made, that memory cache policy should be set to write-back. Without this change, errors may occur.

When concerned with a real-time controller, the purpose for using permissions usually is to detect a misbehaving pointer or for quickly detecting runaway code. This erratum only applies to the misbehaving pointer problem, which when missed on one misuse is most likely found on the next, resulting in the software problem being found and fixed.

2. Flags to memory shared with interrupt handler -

The impact of this problem most likely only involves a handful of sensitive variables for an embedded controller. That is because most variables are used within a task. Only some variables, which need to be passed from one task to another task, is affected. A classic example variable would be a semaphore flag. These variables can be protected in one of three ways:

- a. Locate the variable in locked cache or non-evicting mini-cache. This is the ideal solution for time critical variables such as those passed between an interrupt handler and a background processing task. A non-evicting mini-cache region can be created by setting up a mini-cache memory region and then limiting all access to that region to a 2K aligned address range. Because accesses are not outside the cache boundary, an eviction never occurs and the memory behaves as though it were on-board RAM.

- b. Surround the write of these variables with interrupt disable/enable commands. This is often already done because manipulation of these variables exists in 'critical code' regions where an interrupt between any of the instructions in the critical code region may cause an error condition. Modifying a semaphore is a typical critical code example.

- c. Use the atomic instructions, SWP or SWPB. Therefore, limiting the manipulation of sensitive variables to these instructions avoids the erratum.

- 3. Debug / Breakpoints -

Most debug handlers flush the cache when a break occurs, which reduces the potential for a cache eviction and reduces the potential for a system to be affected by the erratum. So there are few times this erratum should be seen in a debug session, and misinterpreting an apparent bug may be avoided by knowing where this erratum might occur.

#### Status: Fixed.

### 13. Data Cache Dirty Bits May be Corrupted when a Line Invalidate is Followed Immediately by a Store

Problem: The dirty bits in the data cache can be corrupted by an 'Invalidate Data Cache Line' command to address "A" immediately followed by any store to address "B" where address "B" and address "A" are to the same cache set (bits 9:5 of the two addresses are the same).

This can lead to clean or invalid data being marked dirty in the cache, or dirty data in the cache being marked clean. Possible outcomes:

- 1. Invalid data being marked dirty can lead to unpredictable four word stores to an unpredictable address in memory.

- 2. Valid, but clean write-back data, being marked dirty can lead to unnecessary evictions to external memory.

- 3. Valid dirty data being marked clean can lead to data corruption. External memory is not updated upon cache line replacement.

- Workaround: Do not perform a store operation immediately following an 'Invalidate Data Cache Line' command. 'Invalidate Data Cache Line' is a supervisor mode instruction. Placing a NOP between these two operations avoids the erratum.

- *Note:* For more details, see the workaround information for "Data cache dirty bits may be corrupted when a store to cacheable memory occurs during a tag replacement for a different cache line" on page 25.

- Status: Fixed.

Problem:

#### 14. Data cache dirty bits may be Corrupted when a Bus Error on a Cache Line Fill is Followed Immediately by a Store

This erratum is very similar to erratum #14. The problem is the same, but the root cause is different. When certain types of bus errors occur, and a store to the cache occurs near the time when the error is reported, the dirty bits in the array in the same set as the store may be corrupted. The bus errors that can cause this erratum are a multi-bit ECC error on a returning cache line fill or assertion of the external ABORT pin on a returning cache line fill.

This can lead to clean or invalid data being marked dirty in the cache, or dirty data in the cache being marked clean. Possible outcomes:

- 1. Invalid data being marked dirty can lead to unpredictable four word stores to an unpredictable address in memory.

- 2. Valid, but clean write-back data, being marked dirty can lead to unnecessary evictions to external memory.

- 3. Valid dirty write-back data being marked clean can lead to data corruption. External memory will not be updated upon cache line replacement.

Bus errors reported on any store, or on loads that are smaller than 32 bytes do not cause this bug.

Workaround: Set up the page tables such that unimplemented regions of memory do not have valid page table entries. A precise data abort occurs on accesses to those regions and no bus error is seen.

Mark any region of memory that has valid memory locations and unimplemented memory locations within one page as non-cacheable, to avoid cache line fills. This precludes the erratum. An example of this might be a memory mapped register region.

Mark any region of memory that may generate bus aborts that cannot be prevented by appropriate page table entries as non-cacheable.

When there is some reason that code must do a cache line fill that has a chance of creating a bus abort, then avoid store instructions in supervisor mode while potentially aborting cache line fills are pending. The drain write buffer CP15 command issued right after the cache line fill can be used to stall the core during these transactions.

For any triggering abort that cannot be avoided by page table permissions or cacheability (such as multi-bit ECC error on a cache line fill), there is no known workaround. Bus aborts should, in general, be avoided during normal operation.

*Note:* For more details, see the workaround information for "Data cache dirty bits may be corrupted when a store to cacheable memory occurs during a tag replacement for a different cache line" on page 25.

Status: Fixed.

### 15. Performance Monitor Unit Event 0x1 Can Be Incremented Erroneously by Unrelated Events

- Problem: Event 0x1 in the performance monitor unit (PMU) can be used to count cycles in which the instruction cache cannot deliver an instruction. The only cycles counted should be those due to an instruction cache miss or an instruction TLB miss. The following unrelated events in the core, also causes the corresponding count to increment when event number 0x1 is being monitored:

- 1. Any architectural event (e.g. IRQ, data abort)

- 2. MSR instructions which alter the CPSR control bits

- 3. Some branch instructions, including indirect branches and those mispredicted by the BTB

- 4. CP15 mcr instructions to registers 7, 8, 9, or 10 which involve the instruction cache or the instruction TLB.

Each of the items above may cause the performance monitoring count to increment several times. The resulting performance monitoring count may be higher than expected when the above items occur, but never lower.

- Workaround: There is no way to obtain the correct number of cycles stalled due to instruction cache misses and instruction TLB misses. Extra counts due to branch instructions mispredicted by the BTB, may be one component of the unwanted count that can be filtered out. The number of mispredicted branches can also be monitored using performance monitoring event 0x6 during the same time period as event 0x1. The mispredicted branch number can then be subtracted from the instruction cache stall number generated by the performance monitor to get a value closer to the correct one. Note that this only addresses counts contributed by branches that the BTB is able to predict. All the items listed above still affect the count. Depending on the nature of the code being monitored, this workaround may have limited value.

- Status: NoFix.

## 16. In Special Debug State, Back-to-Back Memory Operations Where the First Instruction Aborts May Cause a Hang

Problem: When back-to-back memory operations occur in the Special Debug State (SDS, used by ICE and Debug vendors) and the first memory operation gets a precise data abort, the first memory operation is correctly cancelled and no abort occurs. However, depending on the timing, the second memory operation may not work correctly. The data cache may internally cancel the second operation, but the register file may have scoreboarded registers for that second memory operation.

The effect is that the core may hang (due to a permanently scoreboarded register) or that a store operation may be incorrectly cancelled.

- Workaround: In Special Debug State, any memory operation that may cause a precise data abort should be followed by a write-buffer drain operation. This precludes further memory operations from being in the pipe when the abort occurs. Load Multiple/Store Multiple that may cause precise data aborts should not be used.

- Status: NoFix.

### 17. Instruction Memory Management Unit Address Translation is Turned Off for the First Fetch After Exiting Special Debug State

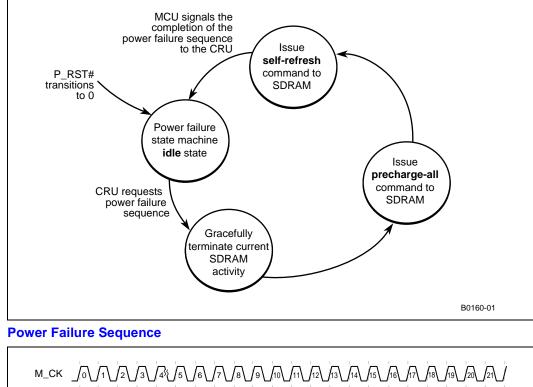

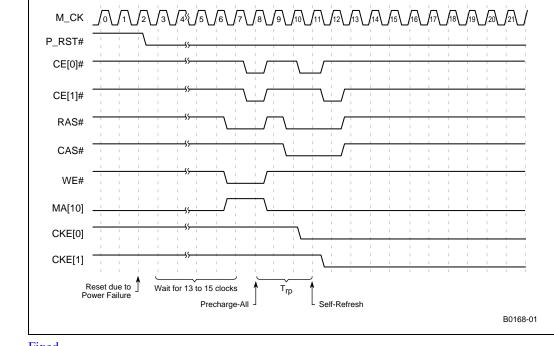

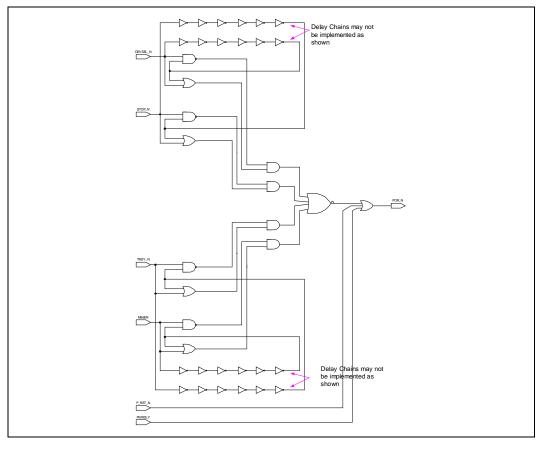

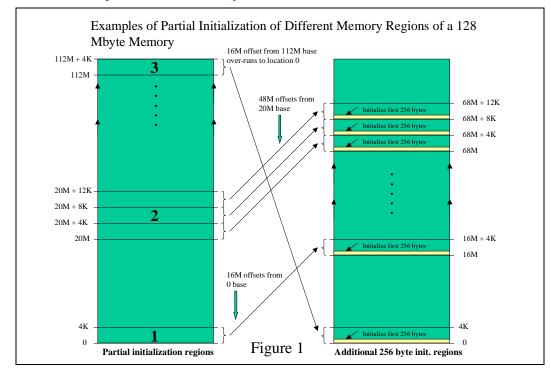

Problem: When the processor enters SDS (Special Debug State), the Instruction Memory Management Unit is disabled. This means that the instruction TLB is no longer accessed and physical-to-virtual address translation no longer occurs. The first code executed after exiting SDS mode should cause an instruction TLB access and execute from the physical memory specified in the appropriate page table entry.