# 21554 PCI-to-PCI Bridge for Embedded Applications

#### **Product Preview Datasheet**

#### **Product Features**

- Full compliance with the PCI Local Bus Specification, Revision 2.1

- 3.3 V operation with 5 V-tolerant I/O

- Selectable asynchronous or synchronous primary and secondary interface clocks

- Concurrent primary and secondary bus operation

- Queuing of multiple transactions in either direction

- 256 bytes of posted write (data and address) buffering in each direction

- 256 bytes of read data buffering in each direction

- Four delayed transaction entries in each direction

- Two dedicated I<sub>2</sub>O delayed transaction entries

- Two sets of standard PCI configuration registers corresponding to the primary and secondary interface; each set is accessible from either the primary or secondary interface

- Memory and I/O mapping of 21554 CSRs on both the primary and secondary interface

- Four downstream and three upstream address ranges, with programmable size and prefetchability

- Look-up table based address translation for one upstream range; direct offset address translation for all other forwarding ranges

- Inverse decoding above the 4 GB address boundary for upstream DACs

- Ability to generate Type 0 and Type 1 configuration transactions on the primary or secondary interface via configuration or I/O CSR accesses

- Ability to generate I/O transactions on the primary or secondary interface via I/O CSR

- I<sub>2</sub>O message unit

- Doorbell registers for software generation of primary and secondary bus interrupts, 16 bits per interface

- Eight Dwords of scratchpad registers

- Parallel ROM interface with primary bus expansion ROM base address register

- Serial ROM interface

- Secondary bus arbiter support for up to nine devices (in addition to the 21554)

- CompactPCI® Hot Swap Controller

- Configurable PCI power management support

- IEEE Standard 1149.1 boundary-scan JTAG interface

**Notice:** This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

Order Number: 278089-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 21554 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

${}^{\star}\mathsf{Third}\text{-party}$  brands and names are the property of their respective owners.

| 1.0 | Introduction                                                                                                                                                                                                                                                                                                                                                          | 1                          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|     | 1.1 General Information                                                                                                                                                                                                                                                                                                                                               |                            |

|     | 1.5 Manual Organization                                                                                                                                                                                                                                                                                                                                               |                            |

| 2.0 | Signal Pins  2.1 Primary PCI Bus Interface 64-Bit Extension Signals  2.2 Secondary PCI Bus Interface Signals  2.3 Secondary PCI Bus Interface 64-Bit Extension Signals  2.4 Secondary PCI Bus Arbitration Signals  2.5 Clock Signals  2.6 Power Management, Hot Swap, and Reset Signals  2.7 ROM Interface Signals  2.8 Miscellaneous Signals  2.9 Diagnostic Signals | 10<br>13<br>14<br>15<br>16 |

| 3.0 | Pin Assignment                                                                                                                                                                                                                                                                                                                                                        | 19                         |

|     | Pin Location List (Alphanumeric)      Pin Signal List (Alphanumeric)                                                                                                                                                                                                                                                                                                  |                            |

| 4.0 | JTAG Boundary Scan                                                                                                                                                                                                                                                                                                                                                    | 30                         |

|     | 4.1 Test Access Port Controller                                                                                                                                                                                                                                                                                                                                       | 30<br>31<br>31             |

| 5.0 | Electrical Specifications                                                                                                                                                                                                                                                                                                                                             | 38                         |

|     | 5.1 PCI Electrical Specification Conformance                                                                                                                                                                                                                                                                                                                          | 38<br>39<br>40             |

#### 21554 PCI-to-PCI Bridge for Embedded Applications

|          |          | 5.4.4 Serial ROM Timing Specifications                |   |

|----------|----------|-------------------------------------------------------|---|

|          |          | 5.4.6 JTAG Timing Specifications                      |   |

| 6.0      | Mecha    | anical Specifications                                 |   |

| Figures  |          |                                                       |   |

| i igaics |          | 21554 Intelligent Controller Application              | • |

|          | 1<br>2   | 21554 Microarchitecture                               |   |

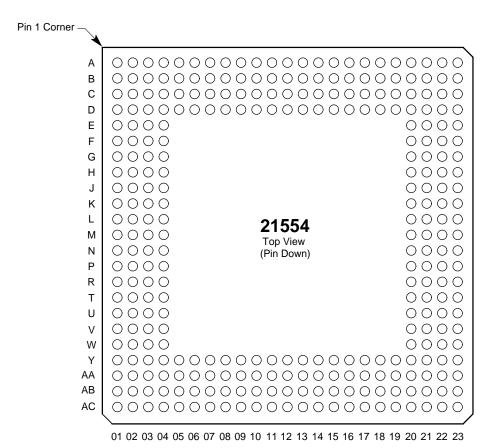

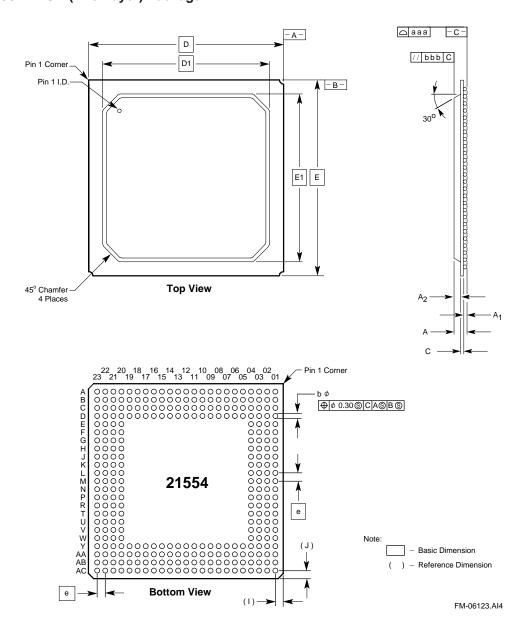

|          | 3        | 21554 PBGA Cavity Down View                           |   |

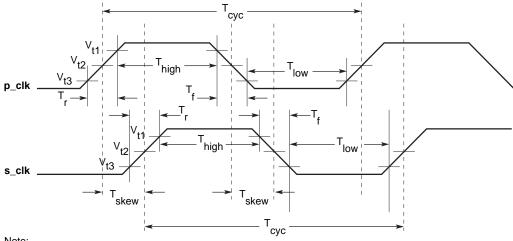

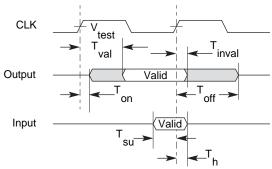

|          | 4        | PCI Clock Signal AC Parameter Measurements            |   |

|          | 5        | PCI Signal Timing Measurement Conditions              |   |

|          | 6        | 304 PBGA (Two-Layer) Package                          |   |

| Tables   |          |                                                       |   |

| 143155   | 1        | 21554 and PPB Feature Comparison                      | 3 |

|          | 2        | Data-unit Terminology                                 |   |

|          | 3        | Signal Pin Function Groups                            | 7 |

|          | 4        | Signal Type Abbreviations                             | 7 |

|          | 5        | Primary PCI Bus Interface Signals (Sheet 1 of 2)      |   |

|          | 6        | Primary PCI Bus Interface 64-Bit Extension Signals    |   |

|          | 7        | Secondary PCI Bus Interface Signals (Sheet 1 of 2)    |   |

|          | 8        | Secondary PCI Bus Interface 64-Bit Extension Signals  |   |

|          | 9        | Secondary PCI Bus Arbitration Signals                 |   |

|          | 10       | Clock Signals                                         |   |

|          | 11       | Power Management, Hot Swap, and Reset Signals         |   |

|          | 12       | ROM Interface Signals (Sheet 1 of 2)                  |   |

|          | 13       | Miscellaneous Signals                                 |   |

|          | 14       | JTAG Signals                                          |   |

|          | 15<br>10 | Signal Type Abbreviations                             |   |

|          | 16       | 21554 Pin Location List (Alphanumeric) (Sheet 1 of 5) |   |

|          | 17<br>18 | Signal Type Abbreviations                             |   |

|          | 19       | 21554 Pin Signal List (Alphanumeric) (Sheet 1 of 5)   |   |

|          | 20       | JTAG Signal Firs                                      |   |

|          | 21       | Boundary-Scan Order (Sheet 1 of 6)                    |   |

|          | 22       | Absolute Maximum Ratings                              |   |

|          | 23       | Functional Operating Range                            |   |

|          | 24       | DC Parameters                                         |   |

|          | 25       | PCI Clock Signal AC Parameters                        |   |

|          | 26       | PCI Signal Timing Specifications                      |   |

|          | 27       | Reset Timing Specifications                           |   |

|          | 28       | Serial ROM Timing Specifications                      |   |

|          | 29       | Parallel ROM Timing Specifications                    |   |

|          | 30       | JTAG Timing Specifications                            |   |

|          | 31       | 304-Point 2-Layer PBGA Package Dimensions             |   |

|          |          |                                                       |   |

#### 1.0 Introduction

This data sheet describes the 21554 PCI-to-PCI bridge chip for embedded applications. For a detailed functional and register description, see the 21554 PCI-to-PCI Bridge for Embedded Applications Hardware Reference Manual.

#### 1.1 General Information

The 21554 is a PCI peripheral chip that performs PCI bridging functions for embedded and intelligent I/O applications. The 21554 is a "non-transparent" PCI-to-PCI bridge that acts as a gateway to an intelligent subsystem. It allows a local processor to independently configure and control the local subsystem. The 21554 implements an I<sub>2</sub>O message unit that enables any local processor to function as an intelligent I/O processor (IOP) in an I<sub>2</sub>O-capable system. Because the 21554 is architecture independent, it works with any host and local processors that support a PCI bus. This architecture independence enables vendors to leverage existing investments while moving products to PCI technology.

Unlike a transparent PCI-to-PCI bridge, the 21554 is specifically designed to bridge between two processor domains. The processor domain on the primary interface of the 21554 is also referred to as the host domain, and its processor is the host processor. The secondary bus interfaces to the local domain and the local processor. Special features include support of independent primary and secondary PCI clocks, independent primary and secondary address spaces, and address translation between the primary (host) and secondary (local) domains.

The 21554 enables add-in card vendors to present to the host system a higher level of abstraction than is possible with a transparent PCI-to-PCI bridge. The 21554 uses a Type 0 configuration header, which presents the entire subsystem as a single "device" to the host processor. This allows loading of a single device driver for the entire subsystem, and independent local processor initialization and control of the subsystem devices. Because the 21554 uses a Type 0 configuration header, it does not require hierarchical PCI-to-PCI bridge configuration code.

The 21554 forwards transactions between the primary and secondary PCI buses as does a transparent PCI-to-PCI bridge. In contrast to a transparent PCI-to-PCI bridge, however, the 21554 can translate the address of a forwarded transaction from a system address to a local address, or vice versa. This mechanism allows the 21554 to hide subsystem resources from the host processor and to resolve any resource conflicts that may exist between the host and local subsystems.

The 21554 operates at 3.3 V, but is also 5.0 V I/O tolerant. Adapter cards designed using the 21554 can be keyed as universal, thus permitting use in either a 5 V or 3 V slot.

The 21554 supports a 64-bit primary PCI bus, a 64-bit secondary PCI bus, and a maximum operating frequency of 33 MHz.

## 1.2 Comparison of 21554 and Standard PCI-to-PCI Bridge

The 21554 is functionally similar to a standard PCI-to-PCI bridge (PPB) in that both provide a connection path between devices attached to two independent PCI buses. A 21554 and a PPB allow the electrical loading of devices on one PCI bus to be isolated from the other bus while permitting concurrent operation on both buses. Because the *PCI Local Bus Specification* restricts PCI option cards to a single electrical load, the ability of PPBs and the 21554 to spawn PCI buses enables the design of multidevice PCI option cards. The key difference between a PPB and the 21554 is that

the presence of a PPB in a connection path between the host processor and a device is transparent to devices and device drivers, while the presence of the 21554 is not. This difference enables the 21554 to provide features that better support the use of intelligent controllers in the subsystem.

It was a primary goal of the PCI-to-PCI bridge architecture that a PPB be transparent to devices and device drivers. For example, no changes are needed to a device driver when a PCI peripheral is located behind a PPB. Once configured during system initialization, a PPB operates without the aid of a device driver. A PPB does not require a device driver of its own since it does not have any resources that must be managed by software during run-time. This requirement for transparency forced the usage of a flat addressing model across PCI-to-PCI bridges. This means that a given physical address exists at only one location in the PCI bus hierarchy and that this location may be accessed by any device attached at any point in the PCI bus hierarchy. As a consequence, it is not possible for a PPB to isolate devices or address ranges from access by devices on the opposite interface of a PPB. The PPB architecture assumes that the resources of any device in a PCI system are configured and managed by the host processor.

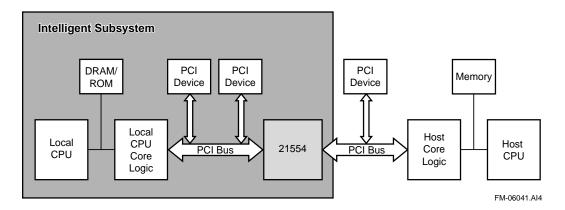

However, there are applications where the transparency of a PCI-to-PCI bridge is not desired. For example, Figure 1 shows a hypothetical PCI add-in card used for an intelligent subsystem application.

Figure 1. 21554 Intelligent Controller Application

Assume that the local processor on the add-in card is used to manage the resources of the devices attached to the add-in card's local PCI bus. Assume also that it is desirable to restrict access to these same resources from other PCI bus masters in the system and from the host processor. In addition, there is a need to resolve address conflicts that may exist between the host system and the local processor. The nontransparency of the 21554 is perfectly suited to this kind of configuration, where a transparent PCI-to-PCI bridge would be problematic.

Because the 21554 is not transparent, the device driver for the add-in card must be aware of the presence of the 21554 and manage its resources appropriately. The 21554 allows the entire subsystem to appear as a single virtual device to the host. This enables configuration software to identify the appropriate driver for the subsystem.

With a transparent PCI-to-PCI bridge, a driver does not need to know about the presence of the bridge and manage its resources. The subsystem appears to the host system as individual PCI devices on a secondary PCI bus, not as a single virtual device.

Table 1 shows a comparison between a 21554 and a standard transparent PCI-to-PCI bridge.

Table 1. 21554 and PPB Feature Comparison

| Feature                         | 21554                                                                                                                                                                                                                                                                                                                        | PCI-to-PCI Bridge                                                                                                                                                                                                                                                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transaction forwarding          | Adheres to PPB ordering rules. Uses posted writes and delayed                                                                                                                                                                                                                                                                | Adheres to PPB ordering rules. Uses posted writes and delayed                                                                                                                                                                                                                                                                        |

|                                 | transactions.  Adheres to PPB transaction error and parity error guidelines, although some errors may be reported differently.                                                                                                                                                                                               | transactions.  Adheres to PPB transaction error and parity error guidelines.                                                                                                                                                                                                                                                         |

| Address decoding                | Base address registers are used to define both downstream and upstream forwarding windows.  Inverse decoding for upstream transactions is only used above the 4GB boundary.                                                                                                                                                  | PPB base and limit address registers are used to define downstream forwarding windows.  Inverse decoding for all I/O and memory upstream forwarding.                                                                                                                                                                                 |

| Address<br>translation          | Supported for both memory and I/O transactions.                                                                                                                                                                                                                                                                              | None. Flat address model is assumed.                                                                                                                                                                                                                                                                                                 |

| Configuration                   | Downstream devices are not visible to host.  Does not require hierarchical configuration code (Type 0 configuration header).  Does not respond to Type 1 configuration transactions.  Supports configuration access from the secondary bus.  Implements separate set of configuration registers for the secondary interface. | Downstream devices are visible to host. Requires hierarchical configuration code (Type 1 configuration header). Forwards and converts Type 1 configuration transactions. Does not support configuration access from the secondary bus. Same set of configuration registers is used to control both primary and secondary interfaces. |

| Run-time resources              | Includes features such as doorbell interrupts, I <sub>2</sub> O message unit, and so on, that must be managed by the device driver.                                                                                                                                                                                          | Typically has only configuration registers; no device driver is required.                                                                                                                                                                                                                                                            |

| Clocks                          | Generates secondary bus clock output. Asynchronous secondary clock input is also supported.                                                                                                                                                                                                                                  | Generates one or more secondary bus clock outputs.                                                                                                                                                                                                                                                                                   |

| Secondary bus central functions | Implements secondary bus arbiter. This function can be disabled.  Drives secondary bus AD,  C/BE#, and PAR during reset. This function can be disabled.                                                                                                                                                                      | Implements secondary bus arbiter. This function can be disabled. Drives secondary bus AD, C/BE#, and PAR during reset.                                                                                                                                                                                                               |

### 1.3 Architectural Overview

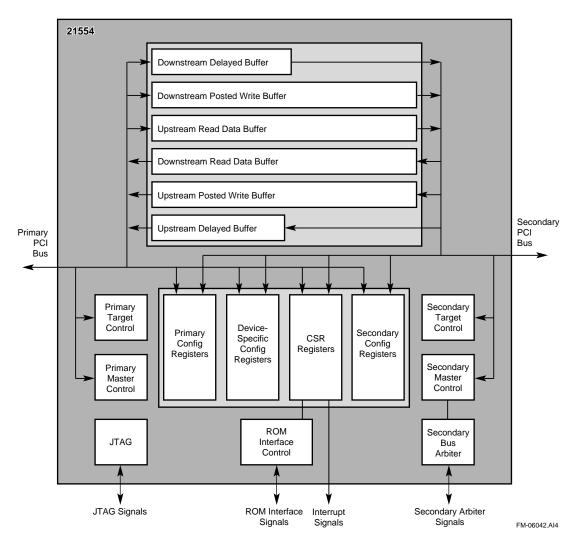

The 21554 consists of the following function blocks:

#### 1.3.1 Data Buffers

Data buffers include the buffers along with the associated data path control logic. Delayed transaction buffers contain the compare functionality for completing delayed transactions. The blocks also contain the watchdog timers associated with the buffers. The data buffers are as follows:

- Four-entry downstream delayed transaction buffer

- Four-entry upstream delayed transaction buffer

- 256-byte downstream posted write buffer

- 256-byte upstream posted write buffer

- 256-byte downstream read data buffer

- 256-byte upstream read data buffer

- Two downstream I<sub>2</sub>O delayed transaction entries

#### 1.3.1.1 Registers

The following register blocks also contain address decode and translation logic,  $I_2O$  message unit, and interrupt control logic:

- Primary interface header Type 0 configuration registers

- Secondary interface header Type 0 configuration registers

- Device-specific configuration registers

- Memory and I/O mapped control and status registers

#### 1.3.2 Control Logic

- Primary PCI target control logic

- Primary PCI master control logic

- Secondary PCI target control logic

- Secondary PCI master control logic

- ROM interface control logic for both serial and parallel ROM connections (interfaces between the ROM registers and ROM signals)

- Secondary PCI bus arbiter interface to secondary bus device request and grant lines, as well as the 21554 secondary master control logic

- JTAG control logic

Figure 2 shows the 21554 microarchitecture.

Figure 2. 21554 Microarchitecture

## 1.4 Conventions and Terminology

This section describes the terminology and conventions used in this datasheet.

#### 1.4.1 Caution

Cautions provide information to prevent damage to equipment or loss of data.

#### 1.4.2 Data Units

This manual uses the following data-unit terminology.

#### Table 2. Data-unit Terminology

| Term     | Words | Bytes | Bits |

|----------|-------|-------|------|

| Byte     | 1/2   | 1     | 8    |

| Word     | 1     | 2     | 16   |

| Dword    | 2     | 4     | 32   |

| Quadword | 4     | 8     | 64   |

#### 1.4.3 Note

Notes emphasize particularly important information.

#### 1.4.4 Numbering

All numbers are decimal or hexadecimal unless otherwise indicated. In cases of ambiguity, a subscript indicates the radix of nondecimal numbers. For example, 19 is decimal, but 19h and 19A are hexadecimal.

#### 1.4.5 Signal Names

Signal names are printed in lowercase, boldface type.

Signal names indicate whether a signal is low-asserted (the signal is active, or asserted, when it is at a low voltage level) or high-asserted (the signal is asserted when it is at a high voltage level). The names of low-asserted signals carry the suffix \_l; the names of high-asserted signals have no suffix. For example, p idsel is a high-asserted signal, and p frame 1 is a low-asserted signal.

The prefix p\_denotes a primary bus signal; the prefix s\_denotes a secondary bus signal. For example, p\_ad is primary interface address/data bus, and s\_ad is secondary interface address/data bus.

#### 1.4.6 SIGNAME#

PCI signals that can be on either the primary interface or the secondary interface are printed in uppercase, normal type. The names of low-asserted signals are followed by #. For example, "asserting FRAME#" can refer to the assertion of the p\_frame\_l signal if the transaction is occurring on the primary bus, or the assertion of the s\_frame\_l signal if the transaction is occurring on the secondary bus.

## 1.5 Manual Organization

This datasheet contains the following chapters and an appendix:

- Chapter 1.0, "Introduction", overview of the 21554 functionality and architecture.

- Chapter 2.0, "Signal Pins", describes the signal pins.

- Chapter 3.0, "Pin Assignment", describes the pin assignments by location and by signal name.

- Chapter 4.0, "JTAG Boundary Scan", explains the 21554's JTAG test port.

- Chapter 5.0, "Electrical Specifications", describes 21554 AC and DC electrical specifications.

- Chapter 6.0, "Mechanical Specifications", describes the 21554 mechanical specifications.

- "", contains technical support and ordering information.

## 2.0 Signal Pins

This chapter provides detailed descriptions of the 21554 signal pins, grouped by function. Table 3 describes these signal pin functional groups.

#### Table 3. Signal Pin Function Groups

| Function                                                     | Description                                                                                                           |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Primary PCI bus interface signal pins                        | All PCI pins required by the PCI Local Bus Specification, Revision 2.1.                                               |

| Primary PCI bus interface<br>64-bit extension signal<br>pins | All PCI 64-bit extension pins required by the PCI Local Bus Specification, Revision 2.1.                              |

| Secondary PCI bus interface signal pins                      | All PCI pins required by the PCI Local Bus Specification, Revision 2.1.                                               |

| Secondary PCI bus interface 64-bit extension signal pins     | All PCI 64-bit extension pins required by the PCI Local Bus Specification, Revision 2.1.                              |

| Secondary PCI bus arbitration signal pins                    | Nine request/grant pairs of pins for the secondary PCI bus.                                                           |

| Clock signal pins                                            | Two clock inputs (one for each PCI interface).                                                                        |

|                                                              | One secondary bus clock output.                                                                                       |

| Power Management, Hot<br>Swap, and Reset signal<br>pins      | Power management and hot-swap status and events. A primary interface reset input. A secondary interface reset output. |

| ROM interface signal pins                                    | 8-bit multiplexed address/data bus plus control for parallel and serial ROM connection.                               |

| Miscellaneous signal pins                                    | Two input voltage signaling level pins.                                                                               |

| Diagnostic signal pins                                       | IEEE Standard 1149.1 boundary-scan JTAG interface. Scan enable.                                                       |

Table 4 defines the signal type abbreviations used in the signal tables.

#### Table 4. Signal Type Abbreviations

| Signal Type | Description                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------|

| I           | Standard input only.                                                                            |

| 0           | Standard output only.                                                                           |

| TS          | Tristate bidirectional.                                                                         |

| STS         | Sustained tristate. Active low signal must be pulled high for one clock cycle when deasserting. |

| OD          | Standard open drain.                                                                            |

Note:

The \_l signal name suffix indicates that the signal is asserted when it is at a low voltage level and corresponds to the # suffix in the *PCI Local Bus Specification*, Revision 2.1. If this suffix is not present, the signal is asserted when it is at a high voltage level.

Table 5 describes the primary PCI bus interface signals.

### Table 5. Primary PCI Bus Interface Signals (Sheet 1 of 2)

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _            |      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| p_ad[31:0]   | TS   | <b>Primary PCI interface address/data.</b> These signals are a 32-bit multiplexed address and data bus. During the address phase or phases of a transaction, the initiator drives a physical address on p_ad[31:0]. During the data phases of a transaction, the initiator drives write data, or the target drives read data, on p_ad[31:0]. When the primary PCI bus is idle, the 21554 drives p_ad to a valid logic level when p_gnt_l is asserted.                                                                                                                                                                                                                                                      |

| p_cbe_l[3:0] | TS   | Primary PCI interface command/byte enables. These signals are a multiplexed command field and byte enable field. During the address phase or phases of a transaction, the initiator drives the transaction type on p_cbe_l[3:0]. When there are two address phases, the first address phase carries the dual-address command and the second address phase carries the transaction type. For both read and write transactions, the initiator drives byte enables on p_cbe_l[3:0] during the data phases. When the primary PCI bus is idle, the 21554 drives p_cbe_l to a valid logic level when p_gnt_l is asserted.                                                                                        |

| p_devsel_I   | STS  | Primary PCI interface DEVSEL#. Signal p_devsel_I is asserted by the target, indicating that the device is responding to the transaction. As a target, the 21554 decodes the address of a transaction initiated on the primary bus to determine whether to assert p_devsel_I. As an initiator of a transaction on the primary bus, the 21554 looks for the assertion of p_devsel_I within five clock cycles of p_frame_I assertion; otherwise, the 21554 terminates the transaction with a master abort. Upon completion of a transaction, p_devsel_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                            |

| p_frame_I    | STS  | Primary PCI interface FRAME#. Signal p_frame_I is driven by the initiator of a transaction to indicate the beginning and duration of an access on the primary PCI bus. Signal p_frame_I assertion (falling edge) indicates the beginning of a PCI transaction. While p_frame_I remains asserted, data transfers can continue. The deassertion of p_frame_I indicates the final data phase requested by the initiator. Upon completion of a transaction, p_frame_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                               |

| p_gnt_l      | I    | <b>Primary PCI bus GNT#</b> . When asserted, p_gnt_l indicates to the 21554 that access to the primary bus is granted. The 21554 can start a transaction on the primary bus when the bus is idle and p_gnt_l is asserted. When the 21554 has not requested use of the bus and p_gnt_l is asserted, the 21554 drives p_ad, p_cbe_l, and p_par to valid logic levels.                                                                                                                                                                                                                                                                                                                                        |

| p_idsel      | I    | <b>Primary PCI interface IDSEL.</b> Signal p_idsel is used as the chip select line for Type 0 configuration accesses to 21554 configuration space from the primary bus. When p_idsel is asserted during the address phase of a Type 0 configuration transaction, the 21554 responds to the transaction by asserting p_devsel_l.                                                                                                                                                                                                                                                                                                                                                                            |

| p_inta_l     | OD   | Primary PCI bus interrupt. Signal p_inta_I is asserted by the 21554 when:  A primary doorbell register bit is set.  The I <sub>2</sub> O outbound queue is not empty.  The subsystem event bit is set.  All of these conditions are individually maskable. When the corresponding event bit is cleared or the outbound queue is emptied, p_inta_I is deasserted. Signal p_inta_I is pulled up through an external resistor.                                                                                                                                                                                                                                                                                |

| p_irdy_l     | STS  | Primary PCI interface IRDY#. Signal p_irdy_I is driven by the initiator of a transaction to indicate the initiator's ability to complete the current data phase on the primary PCI bus. During a write transaction, assertion of p_irdy_I indicates that valid write data is being driven on the p_ad bus. During a read transaction, assertion of p_irdy_I indicates that the initiator is able to accept read data for the current data phase. Once asserted during a given data phase, p_irdy_I is not deasserted until the data phase completes. Upon completion of a transaction, p_irdy_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor. |

### Table 5. Primary PCI Bus Interface Signals (Sheet 2 of 2)

| Signal Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p_par       | TS   | Primary PCI interface parity. Signal p_par carries the even parity of the 36 bits of p_ad[31:0] and p_cbe_l[3:0] for both address and data phases. Signal p_par is driven by the same agent that drives the address (for address parity) or the data (for data parity). Signal p_par contains valid parity one clock cycle after the address is valid (indicated by assertion of p_frame_l), or one clock cycle after the data is valid (indicated by assertion of p_irdy_l for write transactions and p_trdy_l for read transactions). Signal p_par is tristated one clock cycle after the p_ad lines are tristated. The device receiving data samples p_par as an input to check for possible parity errors. When the primary PCI bus is idle, the 21554 drives p_par to a valid logic level when p_gnt_l is asserted (one clock cycle after the p_ad bus is parked).                                                  |

| p_perr_I    | STS  | <b>Primary PCI interface PERR#</b> . Signal p_perr_I is asserted when a data parity error is detected for data received on the primary interface. The timing of p_perr_I corresponds to p_par driven one clock cycle earlier, and p_ad and p_cbe_I driven two clock cycles earlier. Signal p_perr_I is asserted by the target during write transactions, and by the initiator during read transactions. Upon completion of a transaction, p_perr_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                            |

| p_req_l     | TS   | <b>Primary PCI bus REQ#</b> . Signal p_req_I is asserted by the 21554 to indicate to the primary bus arbiter that it wants to start a transaction on the primary bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| p_serr_l    | OD   | Primary PCI interface SERR#. Signal p_serr_I can be driven low by any device on the primary bus to indicate a system error condition. The 21554 can conditionally assert p_serr_I for the following reasons:  Primary bus address parity error  Downstream posted write data parity error on secondary bus  Master abort during downstream posted write transaction  Target abort during downstream posted write transaction  Downstream posted write transaction discarded  Downstream delayed write request discarded  Downstream delayed read request discarded  Downstream delayed transaction master timeout  Secondary bus s_serr_I assertion  Signal p_serr_I is pulled up through an external resistor.                                                                                                                                                                                                          |

| p_stop_I    | STS  | <ul> <li>Primary PCI interface STOP#. Signal p_stop_l is driven by the target of a transaction, indicating that the target is requesting the initiator to stop the transaction on the primary bus.</li> <li>When p_stop_l is asserted in conjunction with p_trdy_l and p_devsel_l assertion, a disconnect with data transfer is being signaled.</li> <li>When p_stop_l and p_devsel_l are asserted, but p_trdy_l is deasserted, a target disconnect without data transfer is being signaled. When this occurs on the first data phase, that is, no data is transferred during the transaction, this is referred to as a target retry.</li> <li>When p_stop_l is asserted and p_devsel_l is deasserted, the target is signaling a target abort.</li> <li>Upon completion of a transaction, p_stop_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.</li> </ul> |

| p_trdy_l    | STS  | Primary PCI interface TRDY#. Signal p_trdy_I is driven by the target of a transaction to indicate the target's ability to complete the current data phase on the primary PCI bus. During a write transaction, assertion of p_trdy_I indicates that the target is able to accept write data for the current data phase. During a read transaction, assertion of p_trdy_I indicates that the target is driving valid read data on the p_ad bus. Once asserted during a given data phase, p_trdy_I is not deasserted until the data phase completes. Upon completion of a transaction, p_trdy_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                                                                                                                  |

## 2.1 Primary PCI Bus Interface 64-Bit Extension Signals

Table 6 describes the primary PCI bus interface 64-bit extension signals.

#### Table 6. Primary PCI Bus Interface 64-Bit Extension Signals

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p_ack64_I    | STS  | Primary PCI interface acknowledge 64-bit transfer. Signal p_ack64_l is asserted by the target only when p_req64_l is asserted by the initiator, to indicate the target's ability to transfer data using 64 bits. Signal p_ack64_l has the same timing as p_devsel_l. When deasserting, p_ack64_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| p_ad[63:32]  | TS   | Primary PCI interface address/data upper 32 bits. This multiplexed address and data bus provides an additional 32 bits to the primary interface. During the address phase or phases of a transaction, when the dual-address command is used and p_req64_I is asserted, the initiator drives the upper 32 bits of a 64-bit address; otherwise, these bits are undefined, and the initiator drives a valid logic level onto the pins. During the data phases of a transaction, the initiator drives the upper 32 bits of 64-bit write data, or the target drives the upper 32 bits of 64-bit read data, when p_req64_I and p_ack64_I are both asserted. When not driven, signals p_ad[63:32] are pulled up to a valid logic level through external resistors.                                                                                                                                                                                                                                                                               |

| p_cbe_l[7:4] | TS   | Primary PCI interface command/byte enables upper 4 bits. These signals are a multiplexed command field and byte enable field. During the address phase or phases of a transaction, when the dual-address command is used and p_req64_l is asserted, the initiator drives the transaction type on p_cbe_l[7:4]; otherwise, these bits are undefined, and the initiator drives a valid logic level onto the pins. For both read and write transactions, the initiator drives byte enables for the p_ad[63:32] data bits on p_cbe_l[7:4] during the data phases, when p_req64_l and p_ack64_l are both asserted. When not driven, signals p_cbe_l[7:4] are pulled up to a valid logic level through external resistors.                                                                                                                                                                                                                                                                                                                      |

| p_par64      | TS   | Primary PCI interface upper 32 bits parity. Signal p_par64 carries the even parity of the 36 bits of p_ad[63:32] and p_cbe_[7:4] for both address and data phases. Signal p_par64 is driven by the initiator and is valid one clock cycle after the first address phase when a dual-address command is used and p_req64_l is asserted. Signal p_par64 is also valid one clock cycle after the second address phase of a dual-address transaction when p_req64_l is asserted. Signal p_par64_l is valid one clock cycle after valid data is driven (indicated by assertion of p_irdy_l for write data and p_trdy_l for read data), when both p_req64_l and p_ack64_l are asserted for that data phase. Signal p_par64 is tristated by the device driving read or write data one clock cycle after the p_ad lines are tristated. Devices receiving data sample p_par64 as an input to check for possible parity errors during 64-bit transactions. When not driven, p_par64 is pulled up to a valid logic level through external resistors. |

| p_req64_I    | STS  | Primary PCI interface request 64-bit transfer. Signal p_req64_l is asserted by the initiator to indicate that the initiator is requesting 64-bit data transfer. Signal p_req64_l has the same timing as p_frame_l. When deasserting, p_req64_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor. The 21554 samples p_req64_l during primary bus reset to enable the 64-bit extension signals. If p_req64_l is sampled high during reset, the primary 64-bit extension is disabled and assumed not connected. The 21554 then drives p_ad[63:32], p_cbe_l[7:4], and p_par64 to valid logic levels.                                                                                                                                                                                                                                                                                                                                                                                 |

## 2.2 Secondary PCI Bus Interface Signals

Table 7 describes the secondary PCI bus interface signals.

#### Table 7. Secondary PCI Bus Interface Signals (Sheet 1 of 2)

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_ad[31:0]   | TS   | Secondary PCI interface address/data. These signals are a 32-bit multiplexed address and data bus. During the address phase or phases of a transaction, the initiator drives a physical address on s_ad[31:0]. During the data phases of a transaction, the initiator drives write data, or the target drives read data, on s_ad[31:0]. When the secondary PCI bus is idle, the 21554 drives s_ad to a valid logic level when its secondary bus grant is asserted.                                                                                                                                                                                                                                             |

| s_cbe_l[3:0] | TS   | Secondary PCI interface command/byte enables. These signals are a multiplexed command field and byte enable field. During the address phase or phases of a transaction, the initiator drives the transaction type on s_cbe_[[3:0]. When there are two address phases, the first address phase carries the dual-address command and the second address phase carries the transaction type. For both read and write transactions, the initiator drives byte enables on s_cbe_[[3:0] during the data phases. When the secondary PCI bus is idle, the 21554 drives s_cbe_I to a valid logic level when its secondary bus grant is asserted.                                                                        |

| s_devsel_I   | STS  | Secondary PCI interface DEVSEL#. Signal s_devsel_I is asserted by the target, indicating that the device is responding to the transaction. As a target, the 21554 decodes the address of a transaction initiated on the secondary bus to determine whether to assert s_devsel_I. As an initiator of a transaction on the secondary bus, the 21554 looks for the assertion of s_devsel_I within five clock cycles of s_frame_I assertion; otherwise, the 21554 terminates the transaction with a master abort. Upon completion of a transaction, s_devsel_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                          |

| s_frame_I    | STS  | Secondary PCI interface FRAME#. Signal s_frame_I is driven by the initiator of a transaction to indicate the beginning and duration of an access on the secondary PCI bus. Signal s_frame_I assertion (falling edge) indicates the beginning of a PCI transaction. While s_frame_I remains asserted, data transfers can continue. The deassertion of s_frame_I indicates the final data phase requested by the initiator. Upon completion of a transaction, s_frame_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                               |

| s_idsel      | I    | Secondary PCI interface IDSEL. Signal s_idsel is used as the chip select line for Type 0 configuration accesses to 21554 configuration space from the secondary bus. When s_idsel is asserted during the address phase of a Type 0 configuration transaction, the 21554 responds to the transaction by asserting s_devsel_I.                                                                                                                                                                                                                                                                                                                                                                                   |

| s_inta_I     | OD   | Secondary PCI bus interrupt. Signal s_inta_I is asserted by the 21554 when:  A secondary doorbell register bit is set.  The I <sub>2</sub> O inbound queue is not empty.  A page boundary is reached when performing lookup table address translation.  The 21554 transitions from a D1 or D2 power state to a D0 power state.  All of these conditions are individually maskable. Signal s_inta_I is deasserted when the corresponding event bit is cleared, or when the inbound queue is empty. Signal s_inta_I is pulled up through an external resistor.                                                                                                                                                   |

| s_irdy_l     | STS  | Secondary PCI interface IRDY#. Signal s_irdy_l is driven by the initiator of a transaction to indicate the initiator's ability to complete the current data phase on the secondary PCI bus. During a write transaction, assertion of s_irdy_l indicates that valid write data is being driven on the s_ad bus. During a read transaction, assertion of s_irdy_l indicates that the initiator is able to accept read data for the current data phase. Once asserted during a given data phase, s_irdy_l is not deasserted until the data phase completes. Upon completion of a transaction, s_irdy_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor. |

### Table 7. Secondary PCI Bus Interface Signals (Sheet 2 of 2)

| Signal Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_par       | TS   | Secondary PCI interface parity. Signal s_par carries the even parity of the 36 bits of s_ad[31:0] and s_cbe_l[3:0] for both address and data phases. Signal s_par is driven by the same agent that drives the address (for address parity) or the data (for data parity). Signal s_par contains valid parity one clock cycle after the address is valid (indicated by assertion of s_frame_l), or one clock cycle after the data is valid (indicated by assertion of s_irdy_l for write transactions and s_trdy_l for read transactions). Signal s_par is tristated one clock cycle after the s_ad lines are tristated. The device receiving data samples s_par as an input to check for possible parity errors. When the secondary PCI bus is idle, the 21554 drives s_par to a valid logic level when its secondary bus grant is asserted (one clock cycle after the s_ad bus is parked). |

| s_perr_l    | STS  | Secondary PCI interface PERR#. Signal s_perr_I is asserted when a data parity error is detected for data received on the secondary interface. The timing of s_perr_I corresponds to s_par driven one clock cycle earlier, and s_ad driven two clock cycles earlier. Signal s_perr_I is asserted by the target during write transactions, and by the initiator during read transactions. Upon completion of a transaction, s_perr_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                               |

| s_serr_l    | OD   | Secondary PCI interface SERR#. Signal s_serr_I can be driven low by any device on the secondary bus to indicate a system error condition. The 21554 also samples s_serr_I as an input and conditionally forwards it to the primary bus on p_serr_I. The 21554 can conditionally assert s_serr_I for the following reasons:  • Secondary bus address parity error  • Upstream posted write data parity error on primary bus  • Master abort during upstream posted write transaction  • Target abort during upstream posted write transaction  • Upstream posted write transaction discarded  • Upstream delayed write request discarded  • Upstream delayed transaction master timeout  Signal s_serr_I is pulled up through an external resistor.                                                                                                                                          |

| s_stop_l    | STS  | Secondary PCI interface STOP#. Signal s_stop_I is driven by the target of a transaction, indicating that the target is requesting the initiator to stop the transaction on the secondary bus.  When s_stop_I is asserted in conjunction with s_trdy_I and s_devsel_I assertion, a disconnect with data transfer is being signaled.  When s_stop_I and s_devsel_I are asserted, but s_trdy_I is deasserted, a target disconnect without data transfer is being signaled. When this occurs on the first data phase, that is, no data is transferred during the transaction, this is referred to as a target retry.  When s_stop_I is asserted and s_devsel_I is deasserted, the target is signaling a target abort.  Upon completion of a transaction, s_stop_I is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                    |

| s_trdy_l    | STS  | Secondary PCI interface TRDY#. Signal s_trdy_l is driven by the target of a transaction to indicate the target's ability to complete the current data phase on the secondary PCI bus. During a write transaction, assertion of s_trdy_l indicates that the target is able to accept write data for the current data phase. During a read transaction, assertion of s_trdy_l indicates that the target is driving valid read data on the s_ad bus. Once asserted during a given data phase, s_trdy_l is not deasserted until the data phase completes. Upon completion of a transaction, s_trdy_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                                                                                 |

## 2.3 Secondary PCI Bus Interface 64-Bit Extension Signals

Table 8 describes the secondary PCI bus interface 64-bit extension signals.

#### Table 8. Secondary PCI Bus Interface 64-Bit Extension Signals

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_ack64_I    | STS  | Secondary PCI interface acknowledge 64-bit transfer. Signal s_ack64_l is asserted by the target only when s_req64_l is asserted by the initiator, to indicate the target's ability to transfer data using 64 bits. Signal s_ack64_l has the same timing as s_devsel_l. When deasserting, s_ack64_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| s_ad[63:32]  | TS   | Secondary PCI interface address/data upper 32 bits. This multiplexed address and data bus provides an additional 32 bits to the secondary interface. During the address phase or phases of a transaction, when the dual-address command is used and s_req64_I is asserted, the initiator drives the upper 32 bits of a 64-bit address; otherwise, these bits are undefined, and the initiator drives a valid logic level onto the pins. During the data phases of a transaction, the initiator drives the upper 32 bits of 64-bit write data, or the target drives the upper 32 bits of 64-bit read data, when s_req64_I and s_ack64_I are both asserted. When not driven, signals s_ad[63:32] are pulled up to a valid logic level through external resistors.                                                                                                                                                                                                                                                                              |

| s_cbe_[[7:4] | TS   | Secondary PCI interface command/byte enables upper 4 bits. These signals are a multiplexed command field and byte enable field. During the address phase or phases of a transaction, when the dual-address command is used and s_req64_l is asserted, the initiator drives the transaction type on s_cbe_l[7:4]; otherwise, these bits are undefined, and the initiator drives a valid logic level onto the pins. For both read and write transactions, the initiator drives byte enables for the s_ad[63:32] data bits on s_cbe_l[7:4] during the data phases, when s_req64_l and s_ack64_l are both asserted. When not driven, signals s_cbe_l[7:4] are pulled up to a valid logic level through external resistors.                                                                                                                                                                                                                                                                                                                       |

| s_par64      | TS   | Secondary PCI interface upper 32 bits parity. Signal s_par64 carries the even parity of the 36 bits of s_ad[63:32] and s_cbe_l[7:4] for both address and data phases. Signal s_par64 is driven by the initiator and is valid one clock cycle after the first address phase when a dual-address command is used and s_req64_l is asserted. Signal s_par64 is also valid one clock cycle after the second address phase of a dual-address transaction when s_req64_l is asserted. Signal s_par64_l is valid one clock cycle after valid data is driven (indicated by assertion of s_irdy_l for write data and s_trdy_l for read data), when both s_req64_l and s_ack64_l are asserted for that data phase. Signal s_par64 is tristated by the device driving read or write data one clock cycle after the s_ad lines are tristated. Devices receiving data sample s_par64 as an input to check for possible parity errors during 64-bit transactions. When not driven, s_par64 is pulled up to a valid logic level through external resistors. |

| s_req64_I    | STS  | Secondary PCI interface request 64-bit transfer. Signal s_req64_l is asserted by the initiator to indicate that the initiator is requesting 64-bit data transfer. Signal s_req64_l has the same timing as s_frame_l. If the 21554 is the secondary bus central function, it will assert s_req64_l low during secondary bus reset to indicate that a 64-bit bus is supported. When deasserting, s_req64_l is driven to a deasserted state for one clock cycle and is then sustained by an external pull-up resistor. The 21554 samples s_req64_l during secondary bus reset to enable the 64-bit extension signals. If s_req64_l is sampled high during reset, the secondary 64-bit extension is disabled and assumed not connected. The 21554 then drives s_ad[63:32], s_cbe_l[7:4], and s_par64 to valid logic levels.                                                                                                                                                                                                                      |

## 2.4 Secondary PCI Bus Arbitration Signals

Table 9 describes the secondary PCI bus arbitration signals.

#### Table 9. Secondary PCI Bus Arbitration Signals

| Signal Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|