## AURIX<sup>™</sup> TC37x errata sheet

Marking/Step: (E)ES-AA, AA

10525AERRA

## About this document

#### Scope and purpose

This document describes the deviations of the device from the current user documentation, to support the assessment of the effects of these deviations on your custom hardware and software implementations.

Please take note of the following information:

- This errata sheet applies to all temperature and frequency versions and to all memory size variants, unless explicitly noted otherwise. For a derivative synopsis, see the latest datasheet or user manual

- Multiple device variants are covered in this one document. If an issue is related to a particular module, and this module is not specified for a specific device variant, then the issue does not apply to that device variant

- For example, issues with the identifier "EMEM" (extension memory) do not apply to devices for which no extension memory is specified ("EMEM" is used only as a generic example and may not be a feature of the device that this document covers)

- Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics and are therefore only suitable for evaluation

- The specific test conditions for EES and ES are documented in a separate status sheet

- Some of the errata have workarounds which may be supported by the tool vendors. Some corresponding compiler switches may need to be set. Please refer to the respective documentation of your compiler

- To understand the effect of issues relating to the on-chip debug system, please refer to the respective debug tool vendor documentation

#### Table 1 Current documentation

| AURIX™ TC3xx User's Manual                             | V2.0.0 | 2021-02    |

|--------------------------------------------------------|--------|------------|

| AURIX™ TC37x Appendix to User's Manual                 | V2.0.0 | 2021-02    |

| TC37x AA-Step Data Sheet                               | V1.1   | 2021-03    |

| TriCore <sup>™</sup> TC1.6.2 Core Architecture Manual: |        |            |

| Core Architecture (Vol. 1)                             | V1.2.2 | 2020-01-15 |

| Instruction Set (Vol. 2)                               | V1.2.2 | 2020-01-15 |

| AURIX™ TC3xx Safety Manual                             | V2.0   | 2021-05-03 |

Newer versions replace older versions, unless specifically stated otherwise.

Please always refer to the corresponding documentation for this device available in the category 'Documents' at www.infineon.com/AURIX<sup>™</sup> and www.myInfineon.com.

#### Conventions used in this document

Each erratum identifier follows the pattern [Module]\_[Arch].[Type][Number]:

- [Module] = subsystem, peripheral, or function affected by the erratum

- [Arch] = microcontroller architecture where the erratum was initially detected

- AI = Architecture Independent

- TC = TriCore™

- [Type] = category of deviation

- [none] = Functional deviation

#### About this document

- P = Parametric deviation

- H = Application hint

- [Number] = ascending sequential number within the three previous fields

- **Note:** [Number] As this sequence is used over several derivatives, including already solved deviations, gaps can occur inside this numbering sequence

Table of contents

## **Table of contents**

|   | About this document   | 1   |

|---|-----------------------|-----|

|   | Table of contents     | 3   |

| 1 | Errata overview       |     |

| 2 | Functional deviations | 19  |

| 3 | Parametric deviations | 145 |

| 4 | Application hints     | 148 |

|   | Revision history      | 226 |

|   | Disclaimer            |     |

## 1 Errata overview

List of errata referenced in this document.

| Table 2 | Functional deviations |

|---------|-----------------------|

|         |                       |

| Issue title                                                                                                                                                 | Change  | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [ADC_TC.095] Ramp trigger ignored when ramp ends                                                                                                            |         | 19   |

| [BROM_TC.013] CAN BSL does not send error message if no valid baudrate is detected                                                                          |         | 19   |

| [BROM_TC.014] Lockstep comparator alarm for CPU0 after warm PORST, system or application reset if lockstep is disabled                                      |         | 19   |

| [BROM_TC.016] Uncorrectable ECC error in Boot Mode Headers                                                                                                  |         | 20   |

| [CCU_TC.005] ASC and CAN bootstrap loaders may not work if external clock is missing                                                                        |         | 20   |

| [CPU_TC.130] Data Corruption when ST.B to local DSPR coincides with external access to same address                                                         |         | 20   |

| [CPU_TC.131] Performance issue when MADD or MSUB instructions use E0 or D0 register as accumulator                                                          |         | 21   |

| [CPU_TC.132] Unexpected PSW values used upon Fast Interrupt entry                                                                                           |         | 22   |

| [CPU_TC.133] Test sequence for DTAG single or double bit errors                                                                                             |         | 23   |

| [DAP_TC.005] DAP client_read: dirty bit feature of Cerberus' Triggered Transfer Mode                                                                        |         | 23   |

| [DAP_TC.007] Incomplete client_blockread telegram in DXCM mode when using the<br>"read CRCup" option                                                        |         | 24   |

| [DMA_TC.059] ACCEN Protection not implemented for ERRINTRr                                                                                                  |         | 24   |

| [DMA_TC.066] DMA double buffering operations - Update address pointer                                                                                       |         | 24   |

| [DMA_TC.067] DMA Double Buffering Software Switch buffer overflow                                                                                           |         | 25   |

| [DMA_TC.068] DMA Double Buffering lost DMA request                                                                                                          |         | 25   |

| [DMA_TC.071] Daisy Chain request is lost when repeat triggers too soon                                                                                      | new     | 26   |

| [EDSADC_TC.004] Hardware bug in Integrator + FIFO use case creating unexpected service request                                                              | changed | 26   |

| [FLASH_TC.053] Erase size limit for PFLASH                                                                                                                  |         | 27   |

| [FLASH_TC.055] Multi-bit errors detected by PFlash are not communicated to SPB masters                                                                      |         | 28   |

| [FLASH_TC.056] Reset value for register HF_ECCC is 0x0000 0000 - Documentation correction                                                                   |         | 28   |

| [FlexRay_AI.087] After reception of a valid sync frame followed by a valid non-sync<br>frame in the same static slot the received sync frame may be ignored |         | 29   |

| [FlexRay_AI.088] A sequence of received WUS may generate redundant SIR.WUPA/B<br>events                                                                     |         | 29   |

| [FlexRay_AI.089] Rate correction set to zero in case of SyncCalcResult=MISSING_TERM                                                                         |         | 30   |

| [FlexRay_AI.090] Flag SFS.MRCS is set erroneously although at least one valid sync frame pair is received                                                   |         | 30   |

|                                                                                                                                                             | -       |      |

### Table 2 (continued) Functional deviations

| Issue title                                                                                                                                                                             | Change | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [FlexRay_AI.091] Incorrect rate and / or offset correction value if second Secondary<br>Time Reference Point (STRP) coincides with the action point after detection of a valid<br>frame |        | 31   |

| [FlexRay_AI.092] Initial rate correction value of an integrating node is zero if<br>pMicroInitialOffsetA,B = 0x00                                                                       |        | 31   |

| [FlexRay_AI.093] Acceptance of start-up frames received after reception of more than gSyncNodeMax sync frames                                                                           |        | 31   |

| [FlexRay_AI.094] Sync frame overflow flag EIR.SFO may be set if slot counter is greater<br>than 1024                                                                                    |        | 32   |

| [FlexRay_AI.095] Register RCV displays wrong value                                                                                                                                      |        | 32   |

| [FlexRay_AI.096] Noise following a dynamic frame that delays idle detection may fail to stop slot                                                                                       |        | 33   |

| [FlexRay_AI.097] Loop back mode operates only at 10 MBit/s                                                                                                                              |        | 33   |

| [FlexRay_AI.099] Erroneous cycle offset during start-up after abort of start-up or normal operation                                                                                     |        | 33   |

| [FlexRay_AI.100] First WUS following received valid WUP may be ignored                                                                                                                  |        | 34   |

| [FlexRay_AI.101] READY command accepted in READY state                                                                                                                                  |        | 34   |

| [FlexRay_AI.102] Slot status vPOC!SlotMode is reset immediately when entering HALT state                                                                                                |        | 35   |

| [FlexRay_Al.103] Received messages not stored in Message RAM when in Loop Back<br>Mode                                                                                                  |        | 35   |

| [FlexRay_AI.104] Missing start-up frame in cycle 0 at coldstart after FREEZE or READY command                                                                                           |        | 36   |

| [FlexRay_AI.105] RAM select signals of IBF1/IBF2 and OBF1/OBF2 in RAM test mode                                                                                                         |        | 36   |

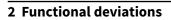

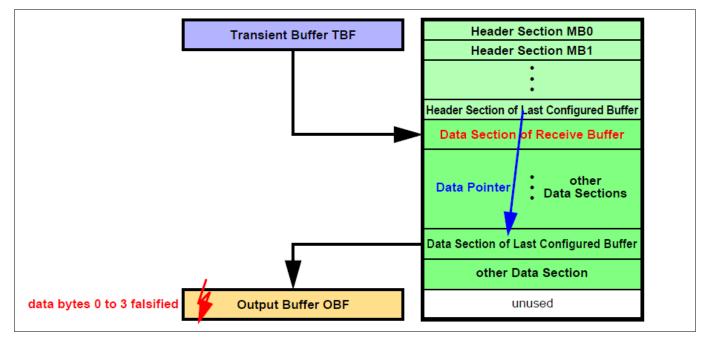

| [FlexRay_AI.106] Data transfer overrun for message transfers Message RAM to Output<br>Buffer (OBF) or from Input Buffer (IBF) to Message RAM                                            |        | 37   |

| [GETH_AI.001] Packets with Destination Address (DA) mismatch are delayed until EOP<br>is received in threshold (cut-through) mode                                                       |        | 39   |

| [GETH_AI.008] Application Error Along with Start-of-Packet Can Corrupt the FCS Field of the Previous Frame in the MAC Pipeline                                                          |        | 40   |

| [GETH_AI.009] Corrupted Rx Descriptor Write Data                                                                                                                                        |        | 40   |

| [GETH_AI.010] Fatal Bus Error Interrupt Might Be Generated for Incorrect DMA Channe                                                                                                     | l      | 41   |

| [GETH_AI.011] Receive Queue Overflow at End of Frame Along with SPRAM Read-Write<br>Conflict Can Cause Data Loss                                                                        | 2      | 41   |

| [GETH_AI.012] Incorrect Flexible PPS Output Interval When Fine Time Correction<br>Method is Used                                                                                        |        | 42   |

| [GETH_AI.013] False Dribble and CRC Error Reported in RMII PHY 10 Mbps Mode                                                                                                             |        | 42   |

| Table 2 | (continued) Functional deviations |

|---------|-----------------------------------|

|---------|-----------------------------------|

| Issue title                                                                                                                                                                 | Change  | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [GETH_AI.014] Receive DMA Channel Generates Spurious Receive Watchdog Timeout<br>Interrupt                                                                                  |         | 43   |

| [GETH_AI.015] MAC Receive VLAN Tag Hash Filter Always Operates in Default Mode                                                                                              |         | 44   |

| [GETH_AI.016] Receive DMA Header Split Function Incorrectly Overruns the Allocated Header Buffer                                                                            |         | 45   |

| [GETH_AI.017] Carrier-Sense Signal Not Generated When False Carrier Detected in RGMII 10/100 Mbps Mode                                                                      |         | 45   |

| [GETH_TC.002] Initialization of RGMII interface                                                                                                                             |         | 46   |

| [GTM_AI.254] TIM TDU: TDU_STOP=b101 not functional                                                                                                                          |         | 47   |

| [GTM_AI.262] SPEC-DPLL: PSSC/PSTC behavior description incorrect                                                                                                            |         | 47   |

| [GTM_AI.263] DPLL: DPLL_STATUS.LOCK1 flag (0 ->1) delayed after direction change when DPLL operating in DPLL_CTRL_0.RMO = 1                                                 |         | 49   |

| [GTM_AI.304] MCS: Scheduling modes Single Prioritization and Multiple Prioritization are not functional                                                                     |         | 49   |

| [GTM_AI.306] DPLL: DPLL_NUTC.syn_t_old, DPLL_NUSC.syn_s_old not updated according specification                                                                             |         | 50   |

| [GTM_AI.307] IRQ: AEI_IM_ADDR is not set in GTM_IRQ_NOTIFY register if cluster 0 is disabled                                                                                |         | 50   |

| [GTM_AI.308] TIM, ARU: Limitation that back-to-back TIM data transfers at full ARU clock rate cannot be transferred correctly with ARU dynamic routing feature              |         | 51   |

| [GTM_AI.318] MCS: NARD(I) instruction reports unexpected status STA.SAT                                                                                                     | changed | 51   |

| [GTM_AI.319] (A)TOM: Unexpected (A)TOM_CCU1TCx_IRQ in up/down counter mode                                                                                                  |         | 52   |

| [GTM_AI.320] ATOM: Unexpected restart of a SOMS oneshot cycle while<br>ATOM[i]_CH[x]_CM0 is zero                                                                            |         | 52   |

| [GTM_AI.322] DPLL: PSTC, PSSC not updated correctly after fast pulse correction completed (DPLL_CTRL1.PCM1/2 = 0)                                                           |         | 53   |

| [GTM_AI.323] DPLL: Registers DPLL_NUTC.SYN_T and DPLL_NUSC.SYN_S are<br>updated by the profile (ADT_T.NT/ADT_S.NS) before the DPLL is synchronized<br>(DPLL_STATUS.SYT/S=0) |         | 54   |

| [GTM_AI.325] TIM: Bits ACB[2:1] lost on interface to ARU (always zero)                                                                                                      |         | 54   |

| [GTM_AI.326] TIM: ARU bit ACB[0] (signal level) incorrect in case a second ARU request occurs while the actual request is just acknowledged                                 |         | 55   |

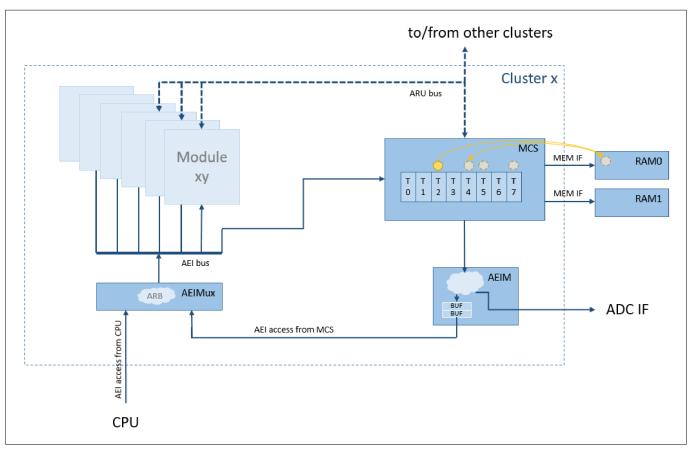

| [GTM_AI.329] Interference of MCS to AEI/ADC and CPU to AEI traffic within the same cluster could result in incorrect MCS program execution                                  |         | 56   |

| [GTM_AI.331] GTM_TIM[i]_AUX_IN_SRC and GTM_EXT_CAP_EN_[i] register: wrong status 2 by AEI write access if cluster 0 is disabled                                             |         | 62   |

| [GTM_AI.332] Access to registers GTM_TIM[i]_AUX_IN_SRC and GTM_EXT_CAP_EN_[i] via legacy address space: read data always 0 for AEI read access while cluster 0 is disabled  |         | 63   |

| Table 2 | (continued) | ) Functional deviations |

|---------|-------------|-------------------------|

|         |             |                         |

| Issue title                                                                                                                                             | Change | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [GTM_AI.333] MCS bus master interface: a not word aligned address access to DPLL<br>ram region can cause incorrect execution of MCS channel code        |        | 63   |

| [GTM_AI.334] DPLL RAM content of single address can be corrupted after leaving debug mode                                                               |        | 64   |

| [GTM_AI.335] TOM output signal to SPE not functional if up/down counter mode is configured                                                              |        | 64   |

| [GTM_AI.336] GTM Bus Bridge: Incorrect AEI access execution in case the previous AEI access was aborted with the access timeout abort function          |        | 65   |

| [GTM_AI.339] DPLL: Control bits DPLL_CTRL_11.PCMF1 and DPLL_CTRL_11.PCMF2 are not reset to 0 after a pulse correction is completed                      |        | 65   |

| [GTM_AI.340] TOM/ATOM: Generation of TRIG_CCU0/TRIG_CCU1 trigger signals skipped in initial phase of A/TOM SOMP one-shot mode                           |        | 66   |

| [GTM_AI.341] TOM/ATOM: False generation of TRIG_CCU1 trigger signal in SOMP one-<br>shot mode with OSM_TRIG=1 when CM1 is set to value 1                |        | 67   |

| [GTM_AI.344] DPLL: Incorrect AEI_STATUS on internal MCS2DPLL interface on valid and implemented address accesses                                        |        | 68   |

| [GTM_AI.345] SPE: Incorrect behaviour of direction change control via<br>SPE_CMD.SPE_CTRL_CMD bits                                                      |        | 69   |

| [GTM_AI.346] ATOM SOMS mode: Shift cycle is not executed correctly in case the reload condition is deactivated with ATOM[i]_AGC_GLB_CTRL.UPEN = 0       |        | 69   |

| [GTM_AI.347] TOM/ATOM: Reset of (A)TOM[i]_CH[x]_CN0 with TIM_EXT_CAPTURE are not correctly synchronized to selected CMU_CLK/CMU_FXCLK                   |        | 70   |

| [GTM_AI.348] DPLL: Correction of missing pulses delayed after start of pulse generation                                                                 |        | 70   |

| [GTM_AI.349] TOM-SPE: OSM-Pulse width triggered by SPE_NIPD for selected<br>CMU_FXCLK not correct                                                       |        | 71   |

| [GTM_AI.350] TOM-SPE: Update of SPE[i]_OUT_CTRL triggered by SPE_NIPD not<br>working for a delay value 1 in TOM[i]_CH[x]_CM1                            |        | 72   |

| [GTM_AI.351] MAP: Disable of input lines by MAP_CTRL register not implemented for input signals TSPP0 TIM0_CHx(48) (x=02) and TSPP1 TIM0_CHx(48) (x=35) |        | 72   |

| [GTM_AI.352] ATOM: Wrong reload of data from ARU in SOMS and SOMP mode if<br>TIM_EXT_CAPTURE(x) or TRIGIN(x) is selected as clock source                |        | 73   |

| GTM_AI.353] SPEC-ATOM: Specification of the smallest possible PWM period in SOMP mode wrong, when ARU_EN=1                                              |        | 74   |

| GTM_AI.354] MCS: Unresolved hazard resulting from RAW (Read After Write) dependency                                                                     |        | 75   |

| GTM_AI.357] MCS: instructions XCHB, SETB, and CLRB do not suppress register write                                                                       |        | 75   |

| [GTM_AI.358] TOM/ATOM: Synchronous update of working register for RST_CCU0=1<br>and UDMODE=01 <sub>B</sub> not correct                                  |        | 76   |

### Table 2 (continued) Functional deviations

| Issue title                                                                                                                                                                                         | Change  | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [GTM_AI.359] TOM: Both edges on TOM_OUT_T at unexpected times for RST_CCU0=1 and UDMODE>0                                                                                                           |         | 77   |

| [GTM_AI.360] SPEC-(A)TOM: PCM mode (BITREV=1) is only available for UDMODE=0                                                                                                                        |         | 77   |

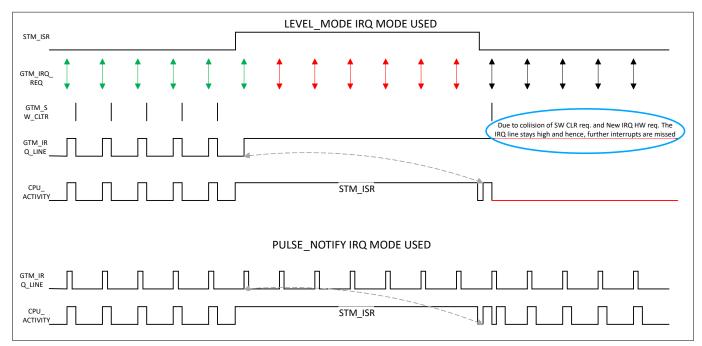

| [GTM_AI.361] IRQ: Missing pulse in single-pulse interrupt mode on simultaneous interrupt and clear event                                                                                            |         | 78   |

| [GTM_AI.362] MCS: Using wrong WURM mask during execution of instruction WURMX or WURCX                                                                                                              |         | 78   |

| [GTM_AI.364] ATOM: ARU read request does not start at expected timepoint in<br>UDMODE = 1 and UDMODE = 3                                                                                            |         | 79   |

| [GTM_AI.367] MCS: Instructions WURMX and WURCX implement invalid extended register set for argument A                                                                                               |         | 80   |

| [GTM_AI.370] TOM/ATOM: Unexpected reset of CN0 in up-down counter mode and CM0 = 2                                                                                                                  |         | 80   |

| [GTM_AI.371] MCS: Instruction MWRIL applies unexpected address offset calculation                                                                                                                   |         | 81   |

| [GTM_AI.374] SPEC-ATOM: Statement on timing of duty cycle output level change not correct for SOMP up/down-counter mode                                                                             |         | 82   |

| [GTM_AI.375] ATOM: Data from ARU are read only once in SOMC mode even though<br>ARU blocking mode is disabled while FREEZE = 1 and ENDIS = 0                                                        |         | 82   |

| [GTM_AI.376] TOM/ATOM: Interrupt trigger signals CCU0TC_IRQ and CCU1TC_IRQ are delayed by one CMU_CLK period related to the output signals                                                          |         | 83   |

| [GTM_AI.387] DPLL: Wrong calculation of pulse generator frequency for<br>DPLL_CTRL_0.AMT/S=1 and DPLL_CTRL_11.ADT/S=1 when number of pulses<br>(DPLL_CTRL_0.MLT or DPLL_MLS1/2.MLS1/2) is too small |         | 83   |

| [GTM_AI.398] DPLL: Incorrect DPLL_THVAL calculation leading to a false direction decision in case tbu_ts0 wraps around                                                                              |         | 84   |

| [GTM_AI.400] MCS-RTL: Division instruction may produce unexpected memory overflow and wrong results                                                                                                 |         | 84   |

| [GTM_AI.404] MCS-RTL: Division instruction reports unrelated ECC error                                                                                                                              |         | 85   |

| [GTM_AI.406] (A)TOM: FREEZE mode has no effect on (A)TOM_OUT_T in up-down counter mode with RST_CCU0 = 1                                                                                            |         | 85   |

| [GTM_AI.408] (A)TOM-RTL: Missing edge on output signal (A)TOM_OUT when CN0 is reset with force update event                                                                                         |         | 86   |

| [GTM_AI.409] DPLL: Flags of register DPLL_STA_FLAG are not set                                                                                                                                      |         | 87   |

| [GTM_AI.410] GTM_AEI: The AEI bridge might not execute an accepted write transaction                                                                                                                | changed | 87   |

| [GTM_AI.411] A change of the BRIDGE_MODE register might be delayed indefinitely                                                                                                                     |         | 88   |

| [GTM_AI.419] TIM: Potentially wrong capture values                                                                                                                                                  |         | 88   |

| [GTM_AI.421] GTM_AEI: Changing BRIDGE_MODE.MSK_WR_RSP in pipeline mode can lead to violation of pipeline protocol                                                                                   |         | 90   |

### Table 2 (continued) Functional deviations

| Issue title                                                                                                                        | Change  | Page |

|------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [GTM_AI.422] DPLL: Wrong DPLL_RDT_S_ACT/DPLL_RDT_T_ACT value in case of overflow correction                                        |         | 90   |

| [GTM_AI.428] DPLL: Pulse correction is executed twice                                                                              |         | 91   |

| [GTM_AI.429] TIM: Missing glitch detection interrupt event                                                                         |         | 91   |

| [GTM_AI.430] TIM: Unexpected increment of filter counter                                                                           |         | 92   |

| [GTM_AI.431] TIM: Glitch detection interrupt event of filter is not a single cycle pulse                                           |         | 93   |

| [GTM_AI.441] DPLL: Missing pulse correction in case of DPLL_CTRL_1.SMC=1                                                           |         | 93   |

| [GTM_AI.442] GTM Top Level: GTM_HALT mode not functional when cluster 0 clock is disabled                                          |         | 94   |

| [GTM_AI.450] DPLL: Stored time stamp values do not consider filter delays                                                          |         | 94   |

| [GTM_AI.451] DPLL: Wrong measured position stamps in RAM                                                                           |         | 95   |

| [GTM_AI.454] (A)TOM: No output if trigger generation feature is used                                                               |         | 95   |

| [GTM_AI.456] DPLL: No action calculation                                                                                           |         | 96   |

| [GTM_AI.458] DPLL: Missing TOR or SOR interrupt and status flag                                                                    | changed | 96   |

| [GTM_AI.461] MCS: Unexpected behavior of instruction WUCE                                                                          |         | 97   |

| [GTM_AI.462] (A)TOM: Missing CCU0TC_IRQ interrupt signal                                                                           |         | 97   |

| [GTM_AI.463] DPLL: DPLL_PVT not cleared after direction change                                                                     |         | 98   |

| [GTM_AI.464] DPLL: Pulse correction executed twice when DPLL_CTRL_11.INCF1/2 is activated                                          |         | 99   |

| [GTM_AI.465] (A)TOM: Missing CCU0TC_IRQ interrupt signal for UDMODE > 0                                                            |         | 99   |

| [GTM_AI.466] TOM: Unexpected behavior of TOM_OUT_T for UDMODE>0                                                                    |         | 100  |

| [GTM_AI.474] DPLL: DPLL_PSTC, DPLL_PSSC erroneously modified                                                                       |         | 100  |

| [GTM_AI.475] DPLL: Incorrect values of DPLL_RCDT_TX, DPLL_RCDT_SX                                                                  |         | 101  |

| [GTM_AI.476] MCS: Unexpected instruction execution while disabling of MCS channel                                                  |         | 101  |

| [GTM_AI.477] DPLL: DPLL_DCGI interrupt not triggered                                                                               |         | 102  |

| [GTM_AI.478] DPLL: Incorrect calculation of DPLL_THVAL, DPLL_THVAL2                                                                |         | 102  |

| [GTM_AI.483] DPLL: Malfunction on changing DPLL_PVT.PVT                                                                            |         | 103  |

| [GTM_AI.487] GTM_AEI: Changing BRIDGE_MODE[2:0] in pipeline mode can lead to violation of pipeline protocol                        |         | 104  |

| [GTM_AI.488] GTM_AEI: Turning off BRIDGE_MODE.MSK_WR_RSP in asynchronous mode might lead to following transactions being corrupted |         | 104  |

| [GTM_AI.490] TOP: Interrupt from DPLL not detected in MCS0                                                                         |         | 104  |

| [GTM_AI.492] DPLL: Wrong value of DPLL_INC_CNT1.INC_CNT1 upon switching to normal mode                                             |         | 105  |

| [GTM_AI.507] DPLL: Irregular pulse generation and wrong PMT results                                                                |         | 106  |

| Issue title                                                                                                                                                                                      | Change             | Dago     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|

| [GTM_AI.516] SPE-RTL: IRQ raised on disabled inputs                                                                                                                                              | Change             | Page 106 |

| [GTM_AI.516] SPE-RTL: RQ Taised on disabled inputs<br>[GTM_AI.517] (A)TOM: Missing edge on output signal (A)TOM_OUT                                                                              | changed            | 108      |

| [GTM_AI.517] (A)TOM: Missing edge on output signal (A)TOM_OUT<br>[GTM_AI.522] (A)TOM: Edge at output signal (A)TOM_OUT does not oc                                                               |                    | 107      |

| [GTM_AI.522] (A) TOM. Edge at output signal (A) TOM_OUT does not oc<br>[GTM_AI.527] GTM-ARCH: CPU bus access is not acknowledged                                                                 |                    | 108      |

| [GTM_AI.327] GTM-ARCH. CFO bus access is not acknowledged<br>[GTM_TC.018] DPLLRAM trace data can be wrong                                                                                        | new                | 108      |

| [GTM_TC.019] ARU can not be traced if GTM cluster 5 is disabled                                                                                                                                  |                    | 109      |

| [GTM_TC.020] Debug/Normal read access control via bit-field ODA.DR                                                                                                                               |                    | 109      |

| [GTM_TC.025] Register DPLL_IRQ_NOTIFY - Documentation update fo                                                                                                                                  |                    | 110      |

| [GTM_TC.026] Table "GTM IP Application Constraints" #1 (DPLL) - Doc correction                                                                                                                   | umentation         | 110      |

| [GTM_TC.028] Incorrect MCS behavior when SSH registers are accesse running                                                                                                                       | ed while MCS is    | 111      |

| [GTM_TC.031]Connections of ADC_TRIG4 signals - Correction in TC3x                                                                                                                                | k appendix         | 111      |

| [HSCT_TC.012] HSCT sleep mode not supported                                                                                                                                                      |                    | 113      |

| [HSCT_TC.013] Internal loopback mode not reliable                                                                                                                                                |                    | 113      |

| [MCMCAN_AI.015] Edge filtering causes mis-synchronization when fal<br>input pin coincides with end of integration phase                                                                          | ling edge at Rx    | 113      |

| [MCMCAN_AI.017] Retransmission in DAR mode due to lost arbitration identifier bits                                                                                                               | n at the first two | 114      |

| [MCMCAN_AI.018] Tx FIFO message sequence inversion                                                                                                                                               |                    | 115      |

| [MCMCAN_AI.019] Unexpected High Priority Message (HPM) interrupt                                                                                                                                 |                    | 116      |

| [MCMCAN_AI.022] Message order inversion when transmitting from d<br>Buffers configured with same Message ID                                                                                      | edicated Tx        | 117      |

| [MCMCAN_AI.023] Incomplete description in section "Dedicated Tx Bu<br>Queue" of the M_CAN documentation in the user manual related to tr<br>multiple buffers configured with the same Message ID |                    | 118      |

| [MCMCAN_AI.024] Frame transmitted despite confirmed transmit can                                                                                                                                 | cellation          | 119      |

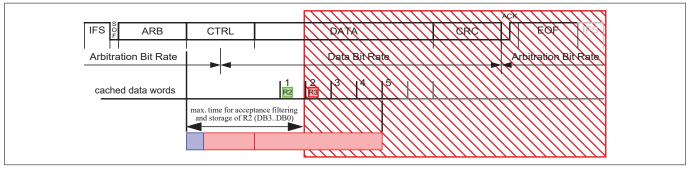

| [MCMCAN_AI.025] Sporadic data corruption (payload) in case accepta<br>not finished before reception of data R3 (DB7DB4) is completed                                                             | nce filtering is   | 120      |

| [MCMCAN_TC.006] MCMCAN specific access protection mechanisms                                                                                                                                     |                    | 122      |

| [miniMCDS_TC.005] TriCore <sup>™</sup> wrap around write access causes redund<br>message                                                                                                         | dant miniMCDS      | 123      |

| [miniMCDS_TC.006] Selection of SRI trace sources                                                                                                                                                 |                    | 123      |

| [miniMCDS_TC.007] Selection of CPU trace sources                                                                                                                                                 |                    | 124      |

| [miniMCDS_TC.008] MCDS kernel reset shall not be used                                                                                                                                            |                    | 124      |

\_\_\_\_

| Issue title                                                                                                                                                  | Change  | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [MSC_TC.027] De-feature of ABRA for MSC                                                                                                                      | new     | 124  |

| [MTU_TC.012] Security of CPU cache memories during runtime is limited                                                                                        |         | 125  |

| [MTU_TC.017] Unexpected alarms after application reset                                                                                                       |         | 125  |

| [MTU_TC.018] Gated SRAM alarms                                                                                                                               |         | 125  |

| [PADS_TC.011] Pull-ups activate on specific analog inputs upon PORST                                                                                         |         | 126  |

| [PADS_TC.013] Buffer type definition for P21.2: no ES functionality - Data Sheet documentation correction                                                    |         | 127  |

| [PADS_TC.016] Pull-ups active on P33 and P34 pins in standby mode when SCR is disabled and VEXT not supplied                                                 |         | 127  |

| [PER_PLL_TC.002] Peripheral PLL K3 Divider Operation                                                                                                         | changed | 128  |

| [PMS_TC.005] Voltage rise at P33 and P34 up to V <sub>EVRSB</sub> during start-up and up to V <sub>LVDRSTSB</sub> during power-down                          |         | 128  |

| [PMS_TC.006] PORST not released during cold power-on reset until V <sub>DDM</sub> is available                                                               |         | 129  |

| [PMS_TC.007] VDDP3 or VDD Overvoltage during start-up may not be detected by<br>PBIST                                                                        |         | 129  |

| [PMS_TC.011] VEXT supplied PU2 and PD2 pads always in tristate after standby entry -<br>Documentation correction                                             |         | 130  |

| [PMS_TC.013] Minimum V <sub>DD</sub> supply voltage for f <sub>SRI</sub> > 200 MHz on TC375TI                                                                |         | 131  |

| [PMS_TC.014] Parasitic coupling on shared ADC pins depending on supply voltages                                                                              |         | 131  |

| [PMS_TC.015] EVRC synchronization – Documentation update for register<br>EVRSDCTRL11 (PMS) and EVRSDCTRL2 (PMSLE)                                            |         | 132  |

| [PSI5_TC.005] Incorrect read pointer upon two consecutive RDFn read operations if two or more channels are configured                                        |         | 132  |

| [QSPI_TC.006] Baud rate error detection in slave mode (error indication in current frame)                                                                    |         | 133  |

| [QSPI_TC.009] USR Events for PT1=2 (SOF: Start of Frame)                                                                                                     |         | 133  |

| [QSPI_TC.010] Move Counter Mode - USR Events for PT1=4 (RBF: Receive Buffer Filled)                                                                          |         | 133  |

| [QSPI_TC.013] Slave: No RxFIFO write after transmission upon change of BACON.MSB                                                                             |         | 134  |

| [QSPI_TC.014] Slave: Incorrect parity bit upon TxFIFO underflow                                                                                              |         | 134  |

| [QSPI_TC.016] Master: Move Counter Mode - Counter underflows when data is present<br>in the TXFIFO while in the last TRAIL state of the previous transaction |         | 134  |

| [QSPI_TC.017] Slave: Reset when receiving an unexpected number of bits                                                                                       |         | 135  |

| [SAFETY_TC.023] MCU infrastructure Safety Related Function - Documentation update                                                                            |         | 135  |

| [SAFETY_TC.024] Clock alive monitor for <i>f</i> <sub>SPB</sub> - Documentation update                                                                       |         | 135  |

| [SAFETY_TC.025] Wrong alarm listed in safety mechanism                                                                                                       |         | 136  |

[SAFETY\_TC.025] Wrong alarm listed in safety mechanism SM[HW]:SRI:SRI\_TRANSACTION\_INTEGRITY

(table continues...)

\_\_\_\_

\_\_\_\_

| Table 2 | continued | ) Functional deviations |

|---------|-----------|-------------------------|

|         |           |                         |

| Issue title                                                                                                                   | Change  | Page |

|-------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [SAFETY_TC.026] Alarm for SM[HW]:IR:CFG_MONITOR - Documentation update                                                        |         | 136  |

| [SAFETY_TC.027] Single point fault detection for lockstep CPUs - Documentation update                                         |         | 136  |

| [SCR_TC.015] Bit SCU_PMCON1.WCAN_DIS does not disable WCAN PCLK input                                                         |         | 137  |

| [SCR_TC.016] DUT response to first telegram has incorrect C_START value                                                       |         | 137  |

| [SCR_TC.018] SSC Receive FIFO not working                                                                                     |         | 137  |

| [SCR_TC.019] Accessing the XRAM while SCR is in reset state                                                                   |         | 138  |

| [SCR_TC.020] Stored address in mon_RETH may be wrong after a break event                                                      |         | 138  |

| [SCR_TC.021] RTC not counting after reset if P33.10 is high                                                                   |         | 138  |

| [SCR_TC.022] Effect of application or system reset and warm PORST on MC77_ECCD and MC78_ECCD for SCR RAMs                     |         | 139  |

| [SCR_TC.023] External interrupts EXINT0, EXINT1 may get locked                                                                |         | 139  |

| [SCR_TC.024] Field ADRES in register ADCOMP_RES - Documentation correction                                                    |         | 140  |

| [SCU_TC.031] Bits SCU_STSTAT.HWCFGx (x=1-5) could have an unexpected value in application if pins HWCFGx are left unconnected |         | 140  |

| [SCU_TC.033] TESTMODE pin shall be held at static level during LBIST                                                          |         | 141  |

| [SCU_TC.036] Concurrent reset requests from CERBERUS do not result in all reset requests captured in reset status register    |         | 141  |

| [SMU_TC.012] Unexpected alarms when registers FSP or RTC are written                                                          |         | 142  |

| [SMU_TC.013] Unexpected setting of Alarm Missed Event bit xAEM in Alarm Executed Status register SMU_AEX                      |         | 143  |

| [SMU_TC.015] SMU alarm emulation might trigger unwanted active alarm reaction                                                 | changed | 144  |

#### Table 3Parametric deviations

| Issue title                                                                                                                 | Change | Page |

|-----------------------------------------------------------------------------------------------------------------------------|--------|------|

| [ADC_TC.P009] Increased TUE for G10 when using Alternate Reference                                                          |        | 145  |

| [ADC_TC.P015] Increased RMS noise for TC374* and TC375* devices                                                             |        | 145  |

| [CCU_TC.P001] Back-up clock accuracy after trimming - Disregard datasheet footnote                                          |        | 146  |

| [FLASH_TC.P003] Program Flash Erase Time per Multi-Sector Command                                                           |        | 146  |

| [PADS_TC.P011] High performance LVDS pads - Documentation update to Data Sheet                                              |        | 147  |

| [PADS_TC.P014] Electrical characteristics for P20.2/TESTMODE                                                                |        | 147  |

| [PORST_TC.P002] <i>V</i> <sub>IH</sub> and <i>V</i> <sub>IL</sub> definition for PORST pad - Additional Data Sheet footnote |        | 147  |

Table 4Application hints

| Issue title                                                                                                                           | Change | Page |

|---------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [ADC_TC.H026] Additional waiting phase in slow standby mode                                                                           |        | 148  |

| [ADC_TC.H032] ADC accuracy parameters - Definition                                                                                    |        | 148  |

| [ADC_TC.H033] Basic initialization sequence for primary and secondary EVADC groups                                                    |        | 148  |

| [ADC_TC.H035] Effect of input leakage current on Broken Wire Detection                                                                |        | 149  |

| [ADC_TC.H043] Information on supervision signal V <sub>ANACOMM</sub> not relevant -<br>Documentation update                           |        | 150  |

| [ADC_TC.H044] Start-up calibration timing in synchronized mode - Documentation update                                                 |        | 150  |

| [ADC_TC.H045] Level selection for broken wire detection feature                                                                       |        | 151  |

| [ADC_TC.H048] EVADC sampling time setting below 300 ns lead to V <sub>DDK</sub> signal conversion inaccuracy                          | new    | 151  |

| [ASCLIN_TC.H001] Bit field FRAMECON.IDLE in LIN slave tasks                                                                           |        | 152  |

| [ASCLIN_TC.H006] Sample point position when using three samples per bit                                                               |        | 152  |

| [ASCLIN_TC.H007] Handling TxFIFO and RxFIFO interrupts in single move mode                                                            |        | 152  |

| [ASCLIN_TC.H008] SPI master timing – Additional information to Data Sheet characteristics                                             |        | 153  |

| [BROM_TC.H009] Re-enabling lockstep via BMHD                                                                                          |        | 153  |

| [BROM_TC.H014] SSW behavior in case of wrong state or uncorrectable error in UCBs -<br>Documentation Update                           |        | 154  |

| [BROM_TC.H015] Different initial values for CPU0_PMEM SSH registers in MTU after cold PORST if SOTA/SWAP is enabled                   |        | 154  |

| [BROM_TC.H020] Processing in case no valid BMHD found                                                                                 |        | 155  |

| [CCU6_TC.H001] CCU6 module clock source information - Documentation Update                                                            |        | 155  |

| [CCU_TC.H012] Configuration of the Oscillator- Documentation Update                                                                   |        | 155  |

| [CLC_TC.H001] Description alignment for bits DISR, DISS, EDIS in register CLC -<br>Documentation Update                               |        | 155  |

| [CPU_TC.H019] Semaphore handling for shared memory resources                                                                          |        | 156  |

| [CPU_TC.H021] Resource update failure despite correct SW synchronization upon retried FPI write transactions by CAN and E-Ray modules |        | 158  |

| [CPU_TC.H022] Store buffering and the effect of bit SMACON.IODT                                                                       |        | 159  |

| [CPU_TC.H023] CPU_SYSCON register safety protection description clarification                                                         |        | 160  |

| [DAM_TC.H002] Triggering DAM MEMCON.RMWERR and INTERR flags                                                                           |        | 160  |

| [DMA_TC.H018] Maximum size of circular buffers is 32 Kbytes                                                                           |        | 160  |

| [DTS_TC.H002] Unexpected alarms after start-up/wake-up when temperature is close<br>to lower/upper limit<br>(table continues)         |        | 161  |

### Table 4 (continued) Application hints

| Issue title                                                                                                        | Change | Page |

|--------------------------------------------------------------------------------------------------------------------|--------|------|

| [EDSADC_TC.H001] Auxiliary filter cleared with start of integration window -<br>Additional information             |        | 161  |

| [EDSADC_TC.H004] CIC3 filter properties - Documentation update                                                     |        | 161  |

| [EDSADC_TC.H005] Incorrect configuration in the section "Stopping the Integration<br>Window"                       |        | 162  |

| [EDSADC_TC.H006] Hardware bug in Integrator + FIFO use case creating unexpected service request                    | new    | 162  |

| [EVR_TC.H001] External input capacitor value - Additional Data Sheet footnote                                      |        | 162  |

| [FLASH_TC.H021] Flash Wait State configuration                                                                     |        | 163  |

| [FLASH_TC.H024]PFLASH erase and program time is affected by time slicing but not clearly documented                |        | 163  |

| [FLASH_TC.H026] Additional information about Test Pass Marker                                                      | new    | 163  |

| [FlexRay_AI.H004] Only the first message can be received in External Loop Back mode                                |        | 164  |

| [FlexRay_AI.H005] Initialization of internal RAMs requires one eray_bclk cycle more                                |        | 164  |

| [FlexRay_AI.H006] Transmission in ATM/Loopback mode                                                                |        | 164  |

| [FlexRay_AI.H007] Reporting of coding errors via TEST1.CERA/B                                                      |        | 164  |

| [FlexRay_Al.H009] Return from test mode operation                                                                  |        | 165  |

| [FlexRay_AI.H010] Driver software must launch CLEAR_RAMS command before reading from E-Ray RAMs                    |        | 165  |

| [FlexRay_Al.H011] Behavior of interrupt flags in FlexRay™ Protocol Controller (E-Ray)                              |        | 165  |

| [FlexRay_TC.H003] Initialization of E-Ray RAMs - Documentation update                                              |        | 166  |

| [FlexRay_TC.H004] Bit WRECC in register TEST2 has no function                                                      |        | 166  |

| [FlexRay_TC.H005] E-Ray OTGB2 trigger set active even if disabled                                                  |        | 167  |

| [FPI_TC.H003] Burst write access may lead to data corruption                                                       |        | 167  |

| [GETH_AI.H001] Preparation for Software Reset                                                                      |        | 167  |

| [GETH_AI.H003] Undefined behavior when LD bit is set and buffer length B1L or B2L is zero - Additional information |        | 168  |

| [GETH_AI.H004] MAC address 0 configuration sequence                                                                |        | 168  |

| [GETH_TC.H002] Stopping and Starting Transmission - Additional information                                         |        | 169  |

| [GPT12_TC.H002] Bits TxUD and TxUDE in incremental interface mode - Additional information                         |        | 170  |

| [GTM_AI.H425] MCS: Instructions BRDI and BWRI evaluate unused address bits                                         |        | 170  |

| [GTM_AI.H473] SPEC-FIFO: Wrong description of FIFO flush operation                                                 |        | 171  |

| [GTM_AI.H480] SPEC-TIM: Wrong action description for TPIM mode                                                     |        | 172  |

| [GTM_AI.H481] SPEC-TIM: Wrong description for TBCM mode<br>(table continues)                                       |        | 172  |

| Table 4 (continued) Application hin |

|-------------------------------------|

|-------------------------------------|

| Issue title                                                                                              | Change  | Page |

|----------------------------------------------------------------------------------------------------------|---------|------|

| [GTM_AI.H482] SPEC-TIM: Wrong description in TBCM mode regarding<br>TIM[i]_CH[x]_CTRL.GPR1_SEL bit field |         | 173  |

| [GTM_AI.H497] SPEC-SPE wiring in figure is wrong                                                         |         | 174  |

| [GTM_AI.H502] SPEC-DPLL input selection for SUB_INC1 is incomplete                                       |         | 174  |

| [GTM_AI.H512] SPEC-SPE: Wrong signal names                                                               | new     | 175  |

| [GTM_AI.H515] SPEC-MCS: Incomplete usage of term CPU in MCS chapter                                      |         | 175  |

| [GTM_AI.H519] SPEC-(A)TOM: Misleading description of Continuous Counting Up<br>Mode                      |         | 176  |

| [GTM_AI.H520] SPEC-(A)TOM: Description for 100% duty cycle incorrect                                     |         | 176  |

| [GTM_AI.H521] SPEC-ATOM: Missing information for SOMB mode                                               |         | 177  |

| [GTM_AI.H525] SPEC-(A)TOM: Description for 0% duty cycle incorrect                                       |         | 177  |

| [GTM_AI.H526] SPEC-(A)TOM: Missing information for SOMP mode                                             |         | 178  |

| [GTM_AI.H528] Spec-(A)TOM: Missing priority information                                                  | new     | 179  |

| [GTM_AI.H803] SPEC-(A)TOM: Missing priority information for register update                              | changed | 179  |

| [GTM_TC.H010] Trigger Selection for EVADC and EDSADC                                                     |         | 180  |

| [GTM_TC.H019] Register GTM_RST - Documentation Update                                                    |         | 180  |

| [GTM_TC.H021] Interrupt strategy mode selection in IRQ_MODE                                              |         | 180  |

| [GTM_TC.H027] Register ODA (OCDS Debug Access) - Documentation update                                    |         | 181  |

| [GTM_TC.H034] Correction to figure GTM to MSC Connections, 1st Level Muxes<br>Overview                   |         | 182  |

| [GTM_TC.H035] Type of bit-fields for xxx_IRQ_NOTIFY registers should be marked as rwh                    | new     | 182  |

| [HSCT_TC.H009] High speed dividers five phase clock sequence ordering                                    |         | 183  |

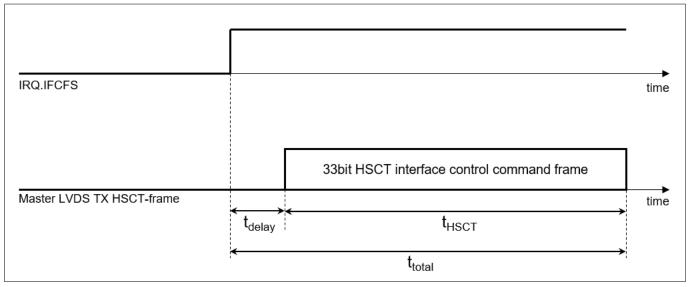

| [HSCT_TC.H010] Interface control command timing on the LVDS ports                                        |         | 184  |

| [I2C_TC.H008] Handling of RX FIFO Overflow in Slave Mode                                                 |         | 185  |

| [I2C_TC.H009] Connections of Serial Clock Inputs                                                         |         | 185  |

| [INT_TC.H006] Number of SRNs supporting external interrupt/service requests –<br>Documentation update    |         | 185  |

| [INT_TC.H007] Interrupt router SRC_xxx register is not always read with correct value                    |         | 186  |

| [LBIST_TC.H003] Update reset behavior of LBISTCTRL0 and LBISTCTRL3 register -<br>Additional information  |         | 186  |

| [LBIST_TC.H005] Effects of LBIST execution on P33.8                                                      |         | 187  |

| [MBIST_TC.H001] Destructive MBIST requires DSPR0 initialization                                          |         | 187  |

| [MBIST_TC.H002] Time for 4N non-destructive test                                                         |         | 187  |

| [MCMCAN_AI.H001] Behavior of interrupt flags in CAN Interface (MCMCAN)                                   |         | 188  |

| Issue title                                                                                                                        | Change | Page |

|------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [MCMCAN_AI.H002] Bus off recovery                                                                                                  | enunge | 188  |

| MCMCAN_TC.H001] Behavior of undefined data bytes read from Receive Buffer                                                          |        | 189  |

| [MCMCAN_TC.H006] Unintended behavior of receive timeout interrupt                                                                  |        | 189  |

| [MCMCAN_TC.H007] Delayed time triggered transmission of frames                                                                     |        | 189  |

| [MCMCAN_TC.H008] Parameter "CAN Frequency" - Documentation update to symbol<br>in Data Sheet                                       |        | 190  |

| [miniMCDS_TC.H001] Program trace of CPUx (x > 0) program start not correct                                                         |        | 190  |

| [MSC_TC.H014] Symbol <i>T<sub>A</sub></i> in specification of FCLPx clock period in Data Sheet -<br>Additional information         |        | 191  |

| MTU_TC.H015] ALM7[0] may be triggered after cold PORST                                                                             |        | 191  |

| MTU_TC.H016] MCi_FAULTSTS.OPERR[2] may be triggered at power-up in case LBIST s not run                                            |        | 191  |

| MTU_TC.H019] Application reset value of register SRC_MTUDONE different to<br>locumentation                                         |        | 192  |

| MTU_TC.H020] SIQ 53 - ALM7[1] unexpectedly raised after an application reset                                                       | new    | 192  |

| NVM_TC.H001] References to DMU_HP_PROCONTP – Typo in TC3xx user manual                                                             |        | 192  |

| OCDS_TC.H014] Avoiding failure of key exchange command due to overwrite of COMDATA by firmware                                     |        | 193  |

| OCDS_TC.H015] System or Application Reset while OCDS and lockstep monitoring are enabled                                           |        | 193  |

| OCDS_TC.H016] Release of application reset via OJCONF may fail                                                                     |        | 194  |

| OCDS_TC.H018] Unexpected stop of Startup Software after system or application eset                                                 |        | 194  |

| OSC_TC.H002] Split the external crystal mode and the external input clock mode parameters of MHz oscillator in the TC3xx datasheet | new    | 194  |

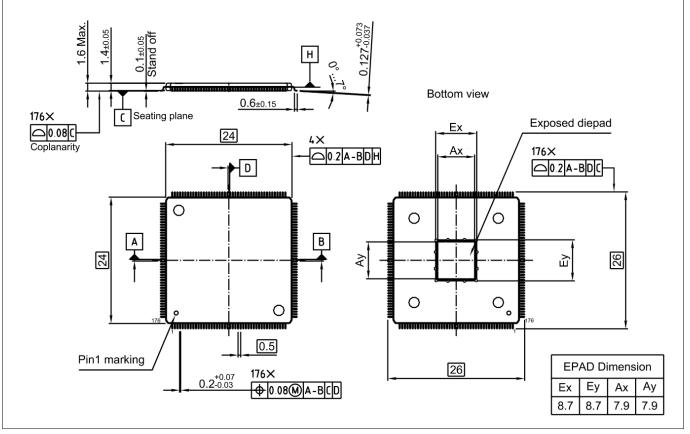

| PACKAGE_TC.H004] Exposed pad dimensions and package outlines for QFP packages<br>Updates to TC37x Data Sheet                       |        | 195  |

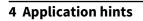

| PADS_TC.H008] Overload coupling for LVDS RX pads – Additional information                                                          |        | 196  |

| PMS_TC.H003] V <sub>DDPD</sub> voltage monitoring limits                                                                           |        | 197  |

| PMS_TC.H008] Interaction of interrupt and power management system - Additional nformation                                          |        | 198  |

| PMS_TC.H009] Interaction of warm reset and standby mode transitions                                                                |        | 199  |

| PMS_TC.H011] Supply mode and topology selection - Allowed combinations of VEXT and VDDM - Documentation update                     |        | 200  |

| PMS_TC.H018] Bit SWDLVL in register EVRSTAT is always 1 when EVRC is OFF                                                           |        | 200  |

| [PMS_TC.H019] Limitation of power-cycles - Additional datasheet footnote                                                           |        | 200  |

| [PORTS_TC.H018] Misleading footnote on pad driver mode selection table                                                             |        | 201  |

| Table 4 | (continued) | Ap | plication | hints |

|---------|-------------|----|-----------|-------|

|         |             |    |           |       |

| Issue title                                                                                                                     | Change | Page |

|---------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [PSI5_TC.H001] No communication error in case of payload length mismatch                                                        |        | 201  |

| [QSPI_TC.H008] Details of the baud rate and phase duration control - Documentation update                                       |        | 201  |

| [QSPI_TC.H011] Missing information on SLSI misplaced inactivation enable error                                                  |        | 202  |

| [RESET_TC.H006] Certain registers may have different reset values than documented in TC3xx User's Manual - Documentation update |        | 202  |

| [RESET_TC.H007] Cold Power on Reset Boot Time – Additional information                                                          |        | 204  |

| [SAFETY_TC.H013] ESM[SW]:SYS:MCU_FW_CHECK - Access to MC40 FAULTSTS register<br>– Additional information                        |        | 205  |

| [SAFETY_TC.H017] Safety Mechanisms requiring initialization - Documentation update                                              |        | 205  |

| [SAFETY_TC.H019] SM[HW]:NVM.FSIRAM:REG_MONITOR_TEST should not be<br>considered                                                 |        | 207  |

| [SAFETY_TC.H020] Test of SM[HW]:VMT:REG_MONITOR is missing - Documentation update                                               |        | 208  |

| [SCR_TC.H009] RAM ECC Alarms in Standby Mode                                                                                    |        | 208  |

| [SCR_TC.H010] HRESET command erroneously sets RRF flag                                                                          |        | 208  |

| [SCR_TC.H011] Hang-up when warm PORST is activated during Debug Monitor Mode                                                    |        | 208  |

| [SCR_TC.H012] Reaction in case of XRAM ECC Error                                                                                |        | 209  |

| [SCR_TC.H014] Details on WDT pre-warning period                                                                                 |        | 209  |

| [SCR_TC.H016] SCR current consumption in IDLE mode and 70 kHz clock                                                             |        | 209  |

| [SCU_TC.H019] Connection on ERU input E_REQ7(5)                                                                                 |        | 210  |

| [SCU_TC.H020] Digital filter on ESRx pins - Documentation update                                                                |        | 210  |

| [SCU_TC.H021] LBIST execution affected by TCK/DAP0 state                                                                        |        | 210  |

| [SCU_TC.H023] Behavior of bit RSTSTAT.PORST after wake-up from standby mode                                                     |        | 210  |

| [SCU_TC.H025] Field EEA in register CHIPID - Additional information                                                             |        | 211  |

| [SCU_TC.H026] Unexpected alarm ALM0[1] during warm reset                                                                        |        | 211  |

| [SCU_TC.H027] Bit field INP0 and INP1 in register EICRi - Documentation correction                                              |        | 211  |

| [SCU_TC.H028] ERU configuration changes may lead to ERU reactions                                                               |        | 212  |

| [SCU_TC.H029] Non-master CPUs can wake-up unexpectedly when exiting from sleep mode                                             |        | 213  |

| [SENT_TC.H006] Parameter V <sub>ILD</sub> on pads used as SENT inputs                                                           |        | 213  |

| [SENT_TC.H007] Range for divider value DIV - Documentation correction                                                           |        | 220  |

| [SENT_TC.H009] Unexpected NNI error behavior                                                                                    |        | 220  |

| [SMU_TC.H010] Clearing individual SMU flags: use only 32-bit writes                                                             |        | 221  |

| [SMU_TC.H012] Handling of SMU alarms ALM7[1] and ALM7[0]<br>(table continues)                                                   |        | 221  |

| Issue title                                                                                                             | Change | Page |

|-------------------------------------------------------------------------------------------------------------------------|--------|------|

| [SMU_TC.H013] Increased Fault Detection for SMU Bus Interface (SMU_CLC Register)                                        |        | 222  |

| [SMU_TC.H016] SMU_stdby restriction for using P33.8 as Emergency Stop input                                             |        | 222  |

| [SMU_TC.H017] Handling of ALM21[7] when safety flip-flop self-test is executed                                          |        | 222  |

| [SRI_TC.H001] Using LDMST and SWAPMSK.W instructions on SRI mapped peripheral registers (range 0xF800 0000-0xFFFF FFFF) |        | 223  |

| [SRI_TC.H003] Incorrect information in SRI error capture registers for HSM transactions                                 |        | 223  |

| [SRI_TC.H005] Clarification of effects for setting PECONx.SETPE                                                         | new    | 224  |

| [SSW_TC.H001] Security hardening measure for the startup behavior                                                       |        | 224  |

| [STM_TC.H004] Access to STM registers while STMDIV = 0                                                                  |        | 225  |

## 2 Functional deviations

## 2.1 [ADC\_TC.095] Ramp trigger ignored when ramp ends

#### Description

The Fast Compare Channels can automatically generate ramps (see section "Ramp Mode" in the EVADC chapter). A ramp can be started by a hardware trigger.

- A trigger that occurs while the ramp is running will restart the ramp from its defined starting level

- A trigger that occurs exactly at the time when the ramp is completed (corner case) will be ignored and lead to no action

#### Workaround

Make sure the ramp trigger is activated while the ramp is not running (this will be the usual case). Avoid trigger intervals with the same duration as the ramp itself.

## 2.2 [BROM\_TC.013] CAN BSL does not send error message if no valid baudrate is detected

#### Description

If the CAN Bootstrap loader (BSL) is unable to determine the baudrate from the initialization message sent by the host, it does not send the error message as defined in table "Error message (No baudrate detected)" in chapter "AURIX™ TC3xx Platform Firmware" in TC3xx User's Manual, but enters an endless loop with no activity on external pins.

#### Workaround

If the external host does not receive Acknowledgment Message 1 from the CAN BSL within the expected time (~5 ms), it should check the integrity of the connection, and then may reset the TC3xx to restart the boot procedure.

## 2.3 [BROM\_TC.014] Lockstep comparator alarm for CPU0 after warm PORST, system or application reset if lockstep is disabled

#### Description

Lockstep monitoring may be disabled in the Boot Mode Header structure (BMHD) for each CPUx with lockstep functionality (including CPU0). The startup software (SSW) will initially re-enable lockstep upon the next reset trigger.

If lockstep is disabled for CPU0, and the next reset is a warm PORST, system or application reset, a lockstep comparator alarm will be raised for CPU0.

*Note:* This effect does not occur for CPUx, x>0.

#### Workaround

Do not disable lockstep for CPU0, always keep lockstep on CPU0 enabled. Non-safety applications may ignore the lockstep comparator alarm for CPU0.

## 2.4 [BROM\_TC.016] Uncorrectable ECC error in Boot Mode Headers

#### Description

If one or more boot mode headers UCB\_BMHDx\_ORIG or UCB\_BMHDx\_COPY contain an uncorrectable ECC error (4-bit error) in the BMI, BMHDID, STAD, CRCBMHD or CRCBMHD\_N fields, firmware will end up in an irrecoverable state resulting in a device not being able to boot anymore.

This may happen in the following scenarios:

- Power-loss during BMHD reprogramming or erase

- Over-programming of complete BMHD contents

#### Workaround

- Ensure continuous power-supply during BMHD reprogramming and erase using power monitoring including appropriate configuration

- Avoid over-programming of BMHD contents

- Ensure that also in any BMHDx\_ORIG or \_COPY unused in the application, the above fields are in a defined ECC-error free state (for example clear them to 0)

## 2.5 [CCU\_TC.005] ASC and CAN bootstrap loaders may not work if external clock is missing

#### Description

When using the ASC or CAN bootstrap loader (BSL) with internal clocking ( $f_{BACK}$ ), and no supply noise or other source of signal level transition is present on the XTAL1 input during device power-up, the device does not respond to the zero byte (ASC BSL) or initialization frame (CAN BSL).

#### Effects

No code download for initial device programming is started.

**Note**: This problem may only occur for initial start-up of unprogrammed devices. For TC3xx, if automatic start of the external crystal oscillation is programed in UCB DFLASH, the problem will not occur.

#### Workaround

Trigger reset and retry if bootstrap loader does not respond.

If connection to the device is possible through a debug tool, use the tool to reconfigure OSCCON.MODE =  $00_B$  (when using an external crystal), and then trigger reset.

## 2.6 [CPU\_TC.130] Data Corruption when ST.B to local DSPR coincides with external access to same address

#### Description

Under certain conditions, when a CPU accesses its local DSPR using "store byte" (ST.B) instructions, at the same time as stores from another bus master (such as remote CPU or DMA for example) to addresses containing the same byte, the result is the corruption of data in the adjacent byte in the same halfword.

- All the following conditions must be met for the issue to be triggered:

- CPU A executes a ST.B targeting its local DSPR

- Remote bus master performs a write of 16-bit or greater targeting CPU A DSPR

- Both internal and external accesses target the same byte without synchronization

*Note:* Although single 8-bit write accesses by the remote bus master do not trigger the problem, 16-bit bus writes from a remote CPU could occur from a sequence of two 8-bit writes merged by the store buffers into one 16-bit access.

When the above conditions occur, the value written by the external master to the adjacent byte (to that written by CPU A) is lost, and the prior value is retained.

#### Workaround 1

Ensure mutually exclusive accesses to the memory location. A semaphore or mutex can be put in place in order to ensure that Core A and other bus masters have exclusive access to the targeted DSPR location.

#### **Workaround 2**

When sharing objects without synchronization between multiple cores, use objects of at least halfword in size.

#### Workaround 3

When two objects, being shared without synchronization between multiple cores, are of byte granularity, locate these objects in a memory which is not a local DSPR to either of the masters (LMU, PSPR, or other DSPR for example).

## 2.7 [CPU\_TC.131] Performance issue when MADD or MSUB instructions use E0 or D0 register as accumulator

#### Description

*Note:* Consider the following notes for TC26x, TC27x, TC29x:

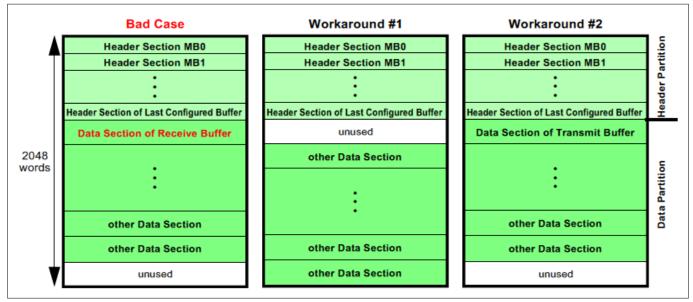

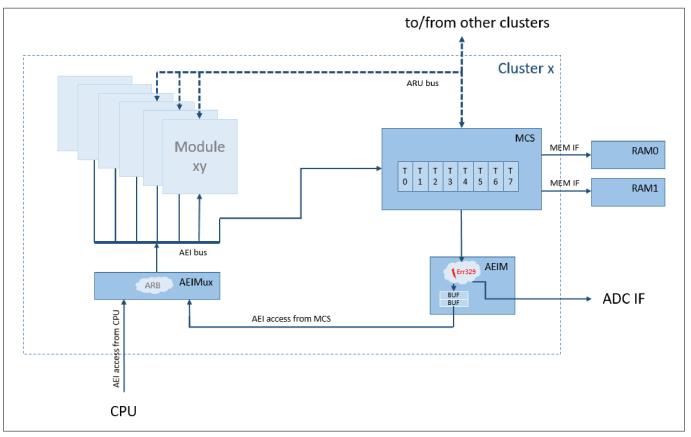

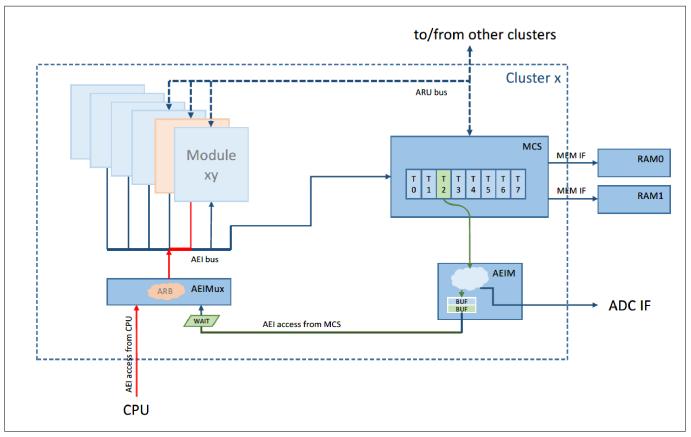

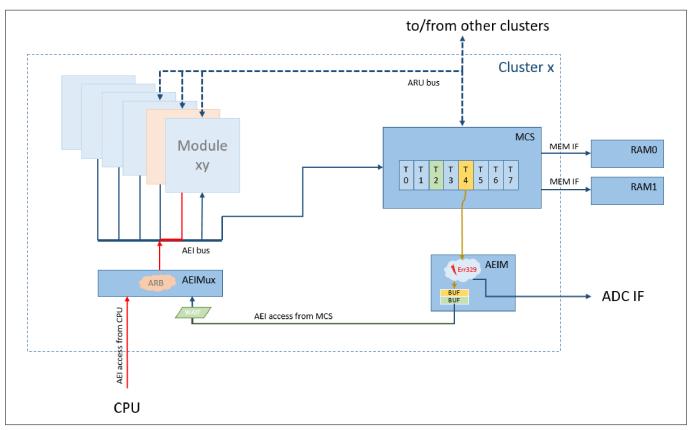

- **TC26x**: In TC26x devices, this problem only affects the TC1.6P processor (CPU1). The TC1.6E processor (CPU0) is not affected by this problem.