May 2001

File Number

3134.3

# Quad SPST, CMOS RF/Video Switch

The IH5352 is a quad SPST, CMOS monolithic switch which uses a "Series/Shunt" ("T" switch) configuration to obtain high OFF isolation while maintaining good frequency response in the ON condition.

Construction of remote and portable video equipment with extended battery life is facilitated by the extremely low current requirements. Switching speeds are typically  $t_{ON} = 150$ ns and  $t_{OFF} = 80$ ns. "Break-Before-Make" switching is guaranteed.

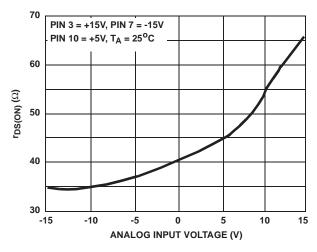

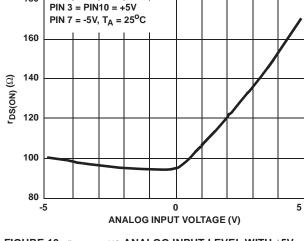

Switch ON resistance is typically  $40\Omega$  -  $50\Omega$  with  $\pm 15$ V power supplies, increasing to typically  $175\Omega$  for  $\pm 5$ V supplies.

# Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |  |

|-------------|---------------------|------------|-------------|--|

| IH5352CPE   | 0 to 70             | 16 Ld PDIP | E16.3       |  |

| IH5352CBP   | 0 to 70             | 20 Ld SOIC | M20.3       |  |

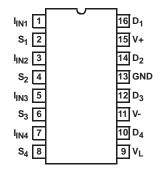

#### **Pinouts**

IH5352 (SOIC) TOP VIEW

#### **Features**

| • | $r_{DS(ON)}$                                              |

|---|-----------------------------------------------------------|

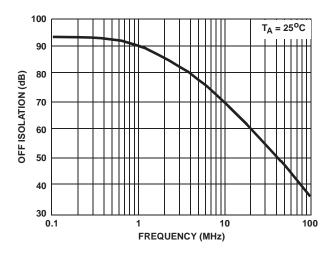

| • | Switch Attenuation Varies Less Than 3dB From DC to 100MHz |

| • | OFF Isolation at 10MHz >70dB                              |

| • | Crosstalk Isolation at 10MHz >60dB                        |

| • | Compatible With TTL, CMOS Logic                           |

| • | Wide Operating Power Supply Range                         |

|   |                                                           |

## "Break-Before-Make" Switching

# • Fast Switching (Typ)......80ns/150ns

# **Applications**

- Video Switch

- · Communications Equipment

- Disk Drives

- Instrumentation

- CATV

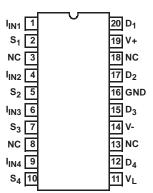

# Functional Diagram

SWITCH STATE SHOWN FOR LOGIC "0" INPUT

**TRUTH TABLE**

| LOGIC | SWITCHES |

|-------|----------|

| 0     | Off      |

| 1     | On       |

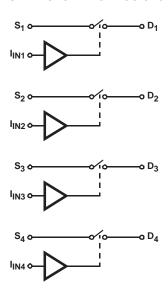

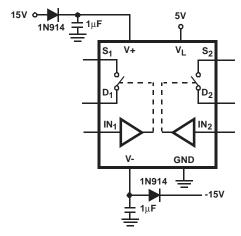

# Schematic Diagram

<sup>1</sup>/<sub>4</sub> IH5352

## **Absolute Maximum Ratings**

| V+ to Ground                  | / |

|-------------------------------|---|

| V- to Ground18\               | / |

| V <sub>L</sub> to Ground      | - |

| Logic Control Voltage V+ to V | - |

| Analog Input Voltage V+ to V  | - |

| Current (Any Terminal)50mA    | ١ |

# **Operating Conditions**

| Temperature Range    | 0°C to 70°C |

|----------------------|-------------|

| Supply Voltage Range |             |

| V+, V <sub>L</sub>   | 5V to 15V   |

| V                    | 5V to -15V  |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)            | $\theta_{JA}$ (°C/W) |

|-------------------------------------------------|----------------------|

| SOIC Package                                    | 90                   |

| PDIP Package                                    |                      |

| Maximum Junction Temperature (Plastic Packages) | 150 <sup>0</sup> C   |

| Maximum Storage Temperature Range65             |                      |

| Maximum Lead Temperature (Soldering, 10s)       | 300°C                |

| (SOIC - Lead Tips Only)                         |                      |

|                                                 |                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** V+ = +15V, $V_L = +5V$ , V- = -15V, Unless Otherwise Specified

| PARAMETER                                                              |                                                                                       | (NOTE 2)    | (NOTE 4) |      |      |       |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------|----------|------|------|-------|

|                                                                        | TEST CONDITIONS                                                                       | TYP<br>25°C | 0°C      | 25°C | 70°C | UNITS |

| DYNAMIC CHARACTERISTICS                                                |                                                                                       | -1          | ı        |      |      |       |

| Turn ON Time, t <sub>ON</sub>                                          | Figure 1                                                                              | 150         | -        | -    | -    | ns    |

| Turn OFF Time, t <sub>OFF</sub>                                        |                                                                                       | 80          | -        | -    | -    | ns    |

| OFF Isolation, OIRR                                                    | Figure 2                                                                              | 70          | -        | -    | -    | dB    |

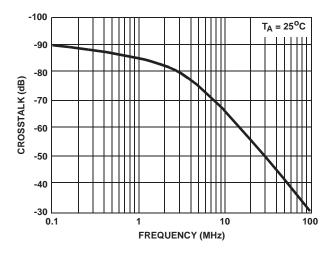

| Crosstalk, CCRR                                                        | Figure 3                                                                              | -60         | -        | -    | -    | dB    |

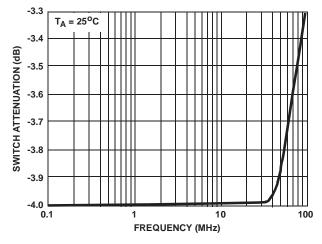

| Switch Attenuation 3dB Frequency, f <sub>3dB</sub>                     | Figure 4                                                                              | 100         | -        | -    | -    | MHz   |

| DIGITAL INPUT CHARACTERISTICS                                          |                                                                                       |             |          |      |      |       |

| Logic "1" Input Voltage, V <sub>IH</sub>                               |                                                                                       | >2.4        | -        | -    | -    | V     |

| Logic "0" Input Voltage, V <sub>IL</sub>                               |                                                                                       | <0.8        | -        | -    | -    | V     |

| Input Logic Current, I <sub>IN</sub>                                   | V <sub>IN</sub> > 2.4V or < 0V                                                        | 0.1         | ±1       | ±1   | 10   | μА    |

| ANALOG SWITCH CHARACTERISTICS                                          |                                                                                       |             |          |      |      |       |

| Drain-Source ON Resistance, r <sub>DS(ON)</sub>                        | $V_D = \pm 5V, I_S = 10 \text{mA}, V_{IN} \ge 2.4V$                                   | 50          | 75       | 75   | 100  | Ω     |

|                                                                        | $V_D = \pm 10V, I_S = 10mA, V_{IN} \ge 2.4V$                                          | 100         | 150      | 150  | 175  | Ω     |

|                                                                        | $V+ = V_L = +5V$ , $V_{IN} = 3V$ , $V- = -5V$ , $V_D = \pm 3V$ , $I_S = 10 \text{mA}$ | 175         | 300      | 300  | 350  | Ω     |

| On Resistance Match Between Channels, $\Delta r_{DS(ON)}$              | $I_S = 10 \text{mA}, V_D = \pm 5 \text{V}$                                            | 5           | -        | -    | -    | Ω     |

| Switch OFF Leakage Current, I <sub>D(OFF)</sub> or I <sub>S(OFF)</sub> | $V_{S/D} = \pm 5V$ or $\pm 14V$ , $V_{IN} \le 0.8V$ (Note 3)                          | -           | -        | ±2   | 100  | nA    |

| Switch ON Leakage Current, I <sub>D(ON)</sub> + I <sub>S(ON)</sub>     | $V_{S/D} = \pm 5V \text{ or } \pm 14V, V_{IN} \ge 2.4V$                               | -           | -        | ±2   | 100  | nA    |

| POWER SUPPLY CHARACTERISTICS                                           |                                                                                       | -           |          |      |      |       |

| Positive Supply Quiescent Current, I+                                  | V <sub>IN</sub> = 0V or +5V                                                           | 0.1         | 1        | 1    | 10   | μА    |

| Negative Supply Quiescent Current, I-                                  |                                                                                       | 0.1         | 1        | 1    | 10   | μΑ    |

| Logic Supply Quiescent Current, I <sub>L</sub>                         |                                                                                       | 0.1         | 1        | 1    | 10   | μА    |

## NOTES:

- 2. Typical values are not tested in production. They are given as a design aid only.

- 3. Positive and negative voltages applied to opposite sides of switch, in both directions successively.

- 4. Min or Max value, unless otherwise specified.

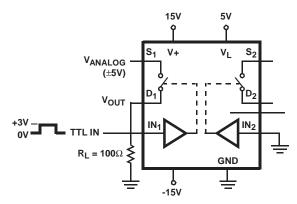

## Test Circuits and Waveforms

NOTE: Only one channel shown. Others act identically.

FIGURE 1A. TEST CIRCUIT

FIGURE 1B. MEASUREMENT POINTS

FIGURE 1. ton AND toff

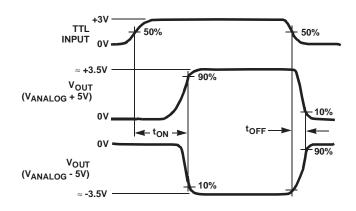

$$V_{IN} = \pm 5V(10V_{P-P})$$

at f = 10MHz

$$OIRR = 20Log \frac{V_{IN}}{V_{OUT}}$$

NOTE: Only one channel shown. Others act identically.

FIGURE 2. OFF ISOLATION TEST CIRCUIT

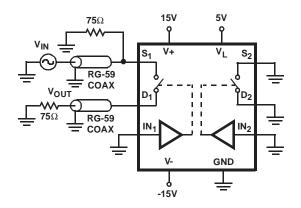

$$V_{IN} = 225 mV_{RMS}$$

at  $f = 10 MHz$

$$CCRR = 20Log \frac{V_{OUT}}{V_{IN}}$$

#### FIGURE 3. CROSSTALK TEST CIRCUIT

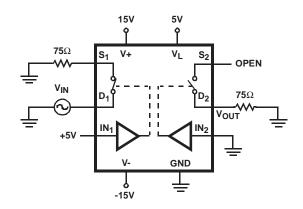

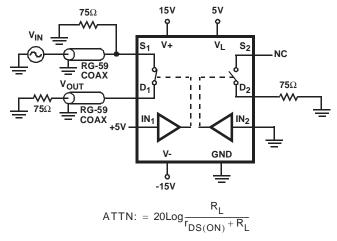

Nominally, at DC, ATTN equals -4dB. When the attenuation reaches -1dB, the frequency at which this occurs is  $f_{3dB}$ . NOTE: Only one channel shown. Others act identically.

FIGURE 4. SWITCH ATTENUATION TEST CIRCUIT

## **Detailed Description**

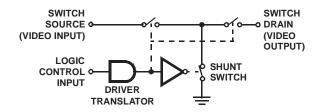

Figure 5 shows the internal circuit of one channel of the IH5352. Here, a shunt switch is closed, and the two series switches are open when the video switch channel is open or off. This provides much better isolation between the input and output terminals than a simple series switch does, especially at high frequencies. The result is excellent offisolation in the Video and RF frequency ranges when compared to conventional analog switches.

The control input level shifting circuitry is very similar to that of the IH5140 series of Analog Switches, and gives very high speed, guaranteed "Break-Before-Make" action, low static power consumption and TTL compatibility.

NOTE: 1 channel of 4 shown.

FIGURE 5. INTERNAL SWITCH CONFIGURATION

# Typical Applications

#### Charge Compensation Techniques

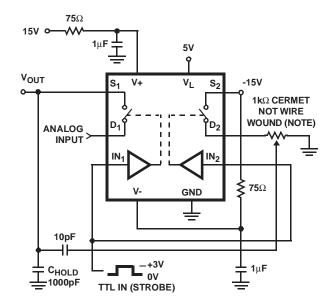

Charge injection results from the signals out of the level translation circuit being coupled through the gate-channel and gate-source/drain capacitances to the switch inputs and outputs. This feedthrough is particularly troublesome in Sample-and-Hold or Track-and-Hold applications, as it causes a Sample (Track) to Hold offset. The IH5352 has a typical injected charge of 30pC-50pC (corresponding to 30mV-50mV on a 1000pF capacitor), at V<sub>S-D</sub> of about 0V.

This Sample (Track) to Hold offset can be compensated by bringing in a signal equal in magnitude but of the opposite polarity. The circuit of Figure 6 accomplishes this charge injection compensation by using one side of the device as a S & H (T & H) switch, and the other side as a generator of a compensating signal. The  $1k\Omega$  potentiometer allows the user to adjust the net injected charge to exactly zero for any analog voltage in the -5V to +5V range.

Since individual parts are very consistent in their charge injection, it is possible to replace the potentiometer with a pair of fixed resistors, and achieve less than 5mV error for all devices without adjustment.

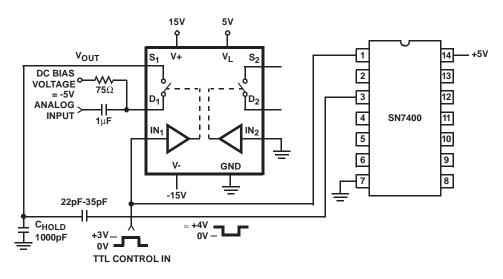

An alternative arrangement, using a standard TTL inverter to generate the required inversion, is shown in Figure 7. The capacitor needs to be increased, and becomes the only method of adjustment. A fixed value of 22pF is good for analog values referred to ground, while 35pF is optimum for AC coupled signals referred to -5V as shown in the figure. The choice of -5V is based on the virtual disappearance at this analog level of the transient component of switching charge injection. This combination will lead to a virtually "glitch-free" switch.

NOTE: Adjust pot for  $0mV_{P-P}$  step at  $V_{OUT}$  with no analog (AC) signal present.

FIGURE 6. CHARGE INJECTION COMPENSATION

FIGURE 7. ALTERNATIVE COMPENSATION CIRCUIT

#### Overvoltage Protection

If sustained operation with no supplies but with analog signals applied is possible, it is recommended that diodes (such as 1N914) be inserted in series with the supply lines to the IH5352. Such conditions can occur if these signals come from a separate power supply or another location, for example. The diodes will be reverse biased under this type of operation, preventing heavy currents from flowing from the analog source through the IH5352.

The same method of protection will provide over  $\pm 25 \text{V}$  overvoltage protection on the analog inputs when the supplies are present. The schematic for this connection is shown in Figure 8.

FIGURE 8. OVERVOLTAGE PROTECTION

180

# **Typical Performance Curves**

FIGURE 9.  $r_{\mbox{DS(ON)}}$  vs analog input voltage with  $\pm 15 \mbox{V}$  Power supplies

FIGURE 10.  $r_{DS(ON)}$  vs analog input level with  $\pm 5V$  power supplies

FIGURE 11. OFF ISOLATION vs FREQUENCY (SEE FIGURE 2)

FIGURE 12. CROSSTALK vs FREQUENCY (SEE FIGURE 3)

FIGURE 13. SWITCH ATTENUATION vs FREQUENCY (R  $_{L}$  = 75  $\!\Omega,$  SEE FIGURE 4)

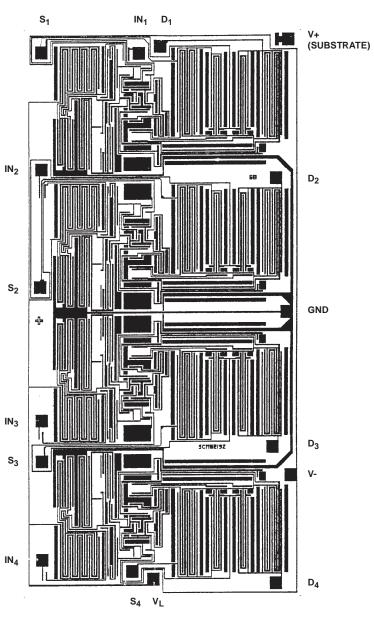

#### Die Characteristics

**DIE DIMENSIONS:**

2617μm x 5233μm

#### **METALLIZATION:**

Type: Al

Thickness: 10kÅ ±1kÅ

#### **PASSIVATION:**

Type: PSG/Nitride

PSG Thickness: 7kÅ ±1.4kÅ Nitride Thickness: 8kÅ ±1.2kÅ

#### **WORST CASE CURRENT DENSITY:**

$9.1 \times 10^4 \text{ A/cm}^2$

# Metallization Mask Layout

IH5352

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com