## **CYUSB3610**

## EZ-USB GX3: SuperSpeed USB to Gigabit Ethernet Bridge Controller

## Features

■ Low-power single chip USB 3.0 to 10/100/1000M Gigabit Ethernet Bridge Controller with Energy Efficient Ethernet (EEE)

#### Gigabit Ethernet Controller

- □ Supports IEEE 802.3az (Energy Efficient Ethernet)

- □ IEEE 802.3, 802.3u, and 802.3ab compatible

- □ Integrates 10/100/1000Mbps Gigabit Ethernet MAC/PHY

- Supports dynamic cable length detection and dynamic power adjustment Green Ethernet (Gigabit mode only)

- □ Supports parallel detection and automatic polarity correction

- □ Supports crossover detection and auto-correction

- □ Supports IPv4/IPv6 packet Checksum Offload Engine (COE) to reduce CPU loading, including IPv4 IP/TCP/UDP/ICMP/IGMP & IPv6 TCP/UDP/ICMPv6 checksum check & generation

- Supports TCP Large Send Offload V1

- Supports full duplex operation with IEEE 802.3x flow control and half duplex operation with back-pressure flow control.

- Supports IEEE 802.1P Layer 2 Priority Encoding and Decoding

- Supports IEEE 802.1Q VLAN tagging and 2 VLAN ID filtering; received VLAN Tag (4 bytes) can be stripped off or preserved

- Supports Jumbo frame

- PHY loop-back diagnostic capability

- USB Device Controller

- □ Integrates on-chip USB 3.0 PHY and controller

- □ Supports USB 3.0 power saving modes (U0, U1, U2, and U3)

- High performance packet transfer rate over USB bus using burst transfer mechanism

- Advanced Power Management Features

- □ Supports power management offload (ARP & NS)

- Supports dynamic power management to reduce power dissipation during idle or light traffic

- Supports AutoDetach power saving. Soft-disconnect from USB host when Ethernet cable is unplugged

- Supports advanced link down power saving when Ethernet cable is unplugged

- Wake-on-LAN Feature

- Supports suspend mode and remote wakeup via link-change, Magic Packet, Microsoft wakeup frame and external wakeup pin

- Supports Bonjour wake-on-demand

- Supports serial EEPROM (93C56/66) for storing USB Descriptors, Node-ID, etc

- Supports automatic loading of USB Device Descriptors, Node-ID, etc. from internal memory or external EEPROM after power-on initialization

- Single 25 MHz clock input from crystal or oscillator source

- Integrates on-chip power-on reset circuit

- Integrates pipelined RISC SoC (System on Chip) for handling protocol and control functions

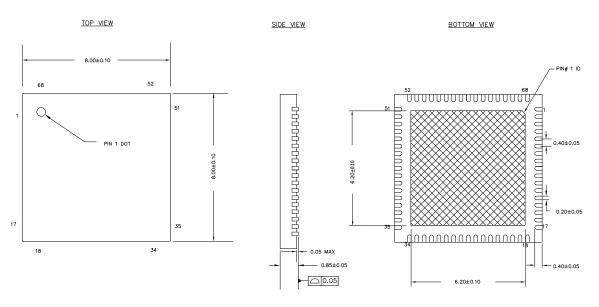

- 68-pin QFN 8 mm × 8 mm RoHS/REACH compliant package

- Operating temperature: 0 °C to 70 °C

## **Target Applications**

- Docking Station

- USB Dongle

- Embedded systems

- Network Printer

- USB Port Replicator

- POS, Card Reader

- Netbook, UMPC, MID

- Ultrabook

- IP STB, IP TV

- Gaming Console

## **Functional Description**

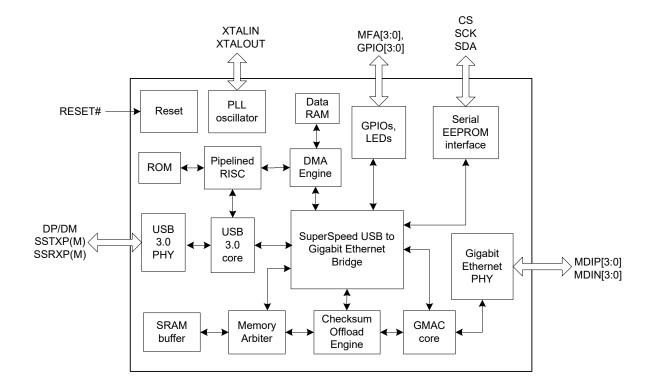

The GX3 SuperSpeed USB to 10/100/1000M Gigabit Ethernet Bridge Controller is a high-performance and highly integrated controller that enables low-cost design, small form-factor, and simple plug-and-play Gigabit Ethernet network connection capability for docking stations, desktops, notebook PCs, Ultrabooks, gaming consoles, digital-home appliances, and any embedded system using a standard USB port.

GX3 implements a 10/100/1000Mbps Ethernet LAN function based on IEEE802.3, IEEE802.3u, and IEEE802.3ab standards with embedded SRAMs for packet buffering. It also integrates an on-chip 10/100/1000Mbps EEE-compliant Ethernet PHY to simplify system design. It features a USB interface to communicate with a USB Host Controller and is compliant with USB specification v3.0.

**Cypress Semiconductor Corporation** Document Number: 001-94768 Rev. \*C 198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised May 31, 2018

## **Block Diagram**

## Contents

| Pin Configurations                         | 4  |

|--------------------------------------------|----|

| Signal Description                         |    |

| Pin Description                            |    |

| Settings                                   |    |

| Hardware Setting                           |    |

| for Operation Mode and Multi-Function Pins | 8  |

| Functional Overview                        | 9  |

| USB Core and Interfaces                    | 9  |

| Energy Efficient Ethernet (EEE)            | 9  |

| 10/100/1000M Ethernet PHY                  | 9  |

| MAC Core                                   | 9  |

| Checksum Offload Engine (COE)              | 9  |

| Memory Arbiter                             | 9  |

| USB to Ethernet Bridge                     | 9  |

| SEEPROM Loader Interface                   | 10 |

| GPIOs and LED                              | 10 |

| PLL Clock Generator                        | 10 |

| Reset Generation                           |    |

| Default Wake-On-LAN (DWOL) Ready Mode      | 11 |

| Procedure to Enable Default WOL Ready Mode | 11 |

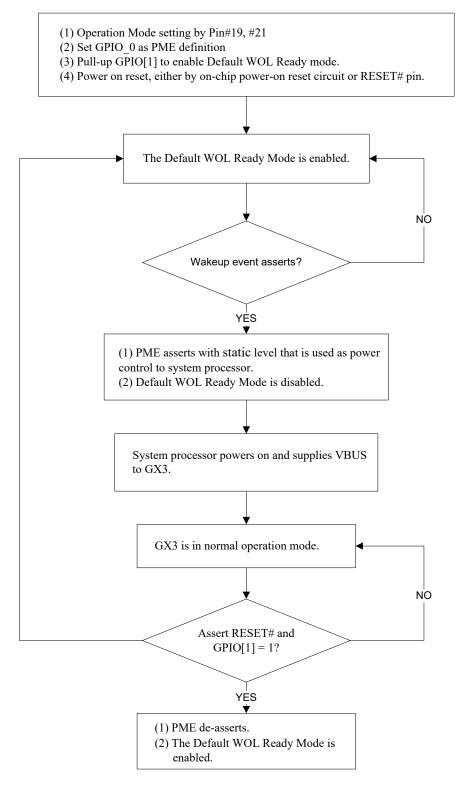

| Flow Chart of Default WOL Ready Mode       | 13 |

| Serial EEPROM Memory Map                   | 14 |

| Detailed Description                       | 15 |

|                                            |    |

| Electrical Specifications       21         DC Characteristics       21         Thermal Characteristics       24         Power Consumption       25         Power-up Sequence       27         AC Timing Characteristics       28         Package Information       30         68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       30         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         PsoC® Solutions       35         Cypress Developer Community       35 | USB Configuration Structure             | 20 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|

| DC Characteristics       21         Thermal Characteristics       24         Power Consumption       25         Power-up Sequence       27         AC Timing Characteristics       28         Package Information       30         68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       31         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         Products       35         PSoC® Solutions       35                                                               | -                                       |    |

| Thermal Characteristics       24         Power Consumption       25         Power-up Sequence       27         AC Timing Characteristics       28         Package Information       30         68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       31         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         PsoC® Solutions       35                                                                                                                             |                                         |    |

| Power-up Sequence       27         AC Timing Characteristics       28         Package Information       30         68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       30         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         PSoC® Solutions       35                                                                                                                                                                                                         |                                         |    |

| Power-up Sequence       27         AC Timing Characteristics       28         Package Information       30         68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       30         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         PSoC® Solutions       35                                                                                                                                                                                                         | Power Consumption                       | 25 |

| AC Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                       |    |

| Package Information       30         68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       30         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         PsoC® Solutions       35                                                                                                                                                                                                                                                                                       |                                         |    |

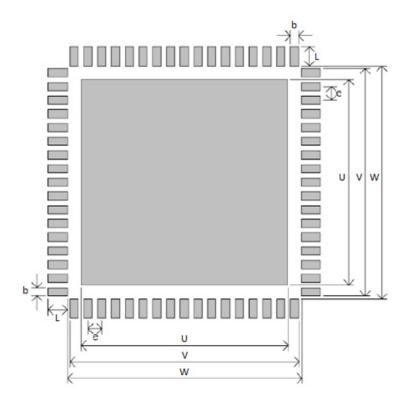

| 68-pin QFN 8 × 8 package       30         Recommended PCB Footprint       31         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         PsoC® Solutions       35                                                                                                                                                                                                                                                                                                                            | -                                       |    |

| Recommended PCB Footprint         for 68-pin QFN 8x8 package       31         Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         Products       35         PSoC® Solutions       35                                                                                                                                                                                                                                                                                                                                                     | •                                       |    |

| for 68-pin QFN 8x8 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |    |

| Ordering Information       32         Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         Products       35         PSoC® Solutions       35                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         | 31 |

| Acronyms       33         Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         Products       35         PSoC® Solutions       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |    |

| Document Conventions       33         Units of measure       33         Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         Products       35         PSoC® Solutions       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |    |

| Document History Page       34         Sales, Solutions, and Legal Information       35         Worldwide Sales and Design Support       35         Products       35         PSoC® Solutions       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |    |

| Sales, Solutions, and Legal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Units of measure                        | 33 |

| Worldwide Sales and Design Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Document History Page                   | 34 |

| Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sales, Solutions, and Legal Information | 35 |

| PSoC® Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Worldwide Sales and Design Support      | 35 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Products                                | 35 |

| Cypress Developer Community35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PSoC® Solutions                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Cypress Developer Community             | 35 |

| Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |    |

## **Pin Configurations**

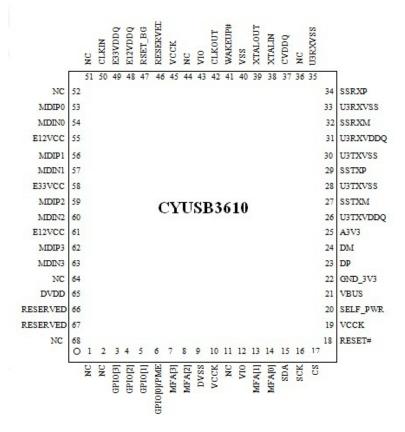

Figure 1. 68-pin QFN pinout

## **Signal Description**

The following abbreviations apply to the following pin description table.

| Signal Name | Signal Description                           | Signal Name | Signal Description         |

|-------------|----------------------------------------------|-------------|----------------------------|

| 112         | Input, 1.2 V                                 | AI          | Analog Input               |

| 13          | Input, 3.3 V                                 | AO          | Analog Output              |

| 15          | Input, 3.3 V with 5 V tolerance              | AB          | Analog Bi-directional I/O  |

| O3          | Output, 3.3 V                                | PU          | Internal Pull Up (75 kΩ)   |

| B5          | Bi-directional I/O, 3.3 V with 5 V tolerance | PD          | Internal Pull Down (75 kΩ) |

| B3          | Bi-directional I/O, 3.3 V                    | S           | Schmitt Trigger            |

| Р           | Power/GND                                    | Т           | Tri-stateable              |

## **Pin Description**

| Pin Name     | Туре        | Pin No.     | Pin Description                                                                                                                                         |  |  |  |

|--------------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| USB Interfac | e           |             |                                                                                                                                                         |  |  |  |

| DP           | AB          | 23          | USB 2.0 D+ pin.                                                                                                                                         |  |  |  |

| DM           | AB          | 24          | JSB 2.0 D– pin.                                                                                                                                         |  |  |  |

| SSTXP        | AB          | 29          | USB 3.0 SSTX+ pin.                                                                                                                                      |  |  |  |

| SSTXM        | AB          | 27          | USB 3.0 SSTX-pin.                                                                                                                                       |  |  |  |

| SSRXP        | AB          | 34          | USB 3.0 SSRX+ pin.                                                                                                                                      |  |  |  |

| SSRXM        | AB          | 32          | USB 3.0 SSRX- pin.                                                                                                                                      |  |  |  |

| VBUS         | I5/PD/S     | 21          | VBUS pin input. Please connect to USB bus power.                                                                                                        |  |  |  |

| Gigabit EEE  | Ethernet PH | Y Interface |                                                                                                                                                         |  |  |  |

| RSET_BG      | AO          | 47          | For Ethernet PHY's internal biasing. Please connect to GND through a 2.49 k $\Omega$ ±1% resistor.                                                      |  |  |  |

| MDIP0        | AB          | 53          | In MDI mode, this is the first pair in 1000Base-T, i.e. the BI_DA+/- pair, and is the transmit                                                          |  |  |  |

| MDIN0        | AB          | 54          | pair in 10Base-T and 100Base-TX.<br>In MDI crossover mode, this pair acts as the BI_DB+/- pair, and is the receive pair in<br>10Base-T and 100Base-TX.  |  |  |  |

| MDIP1        | AB          | 56          | In MDI mode, this is the second pair in 1000Base-T, i.e. the BI_DB+/- pair, and is the receive                                                          |  |  |  |

| MDIN1        | AB          | 57          | pair in 10Base-T and 100Base-TX.<br>In MDI crossover mode, this pair acts as the BI_DA+/- pair, and is the transmit pair in<br>10Base-T and 100Base-TX. |  |  |  |

| MDIP2        | AB          | 59          | In MDI mode, this is the third pair in 1000Base-T, i.e., the BI_DC+/- pair.                                                                             |  |  |  |

| MDIN2        | AB          | 60          | In MDI crossover mode, this pair acts as the BI_DD+/- pair.                                                                                             |  |  |  |

| MDIP3        | AB          | 62          | In MDI mode, this is the fourth pair in 1000Base-T, i.e., the BI_DD+/- pair.                                                                            |  |  |  |

| MDIN3        | AB          | 63          | In MDI crossover mode, this pair acts as the BI_DC+/- pair.                                                                                             |  |  |  |

| Clock Pins   |             | I           |                                                                                                                                                         |  |  |  |

| XTALIN       | 13          | 38          | 25 MHz ± 0.005% crystal or oscillator clock input.                                                                                                      |  |  |  |

| XTALOUT      | O3          | 39          | 25 MHz crystal or oscillator clock output.                                                                                                              |  |  |  |

| CLKOUT       | O3          | 42          | A controllable 25MHz clock output.<br>Please connect it to CLKIN pin with a 22 Ohm termination resistor near to CLKOUT pin.                             |  |  |  |

| CLKIN        | 13          | 50          | 25 MHz clock input.<br>Please connect it to CLKOUT pin with a 22 Ohm termination resistor.                                                              |  |  |  |

## Pin Description (continued)

| Pin Name     | Туре       | Pin No.                   | Pin Description                                                                                                                                                                                                                               |  |

|--------------|------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Serial EEPRO |            | )                         |                                                                                                                                                                                                                                               |  |

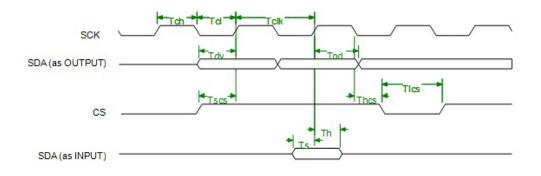

| SCK          | B5/PD/T    | 16                        | EEPROM Clock. SCK is an output clock to EEPROM to provide timing reference for the transfer of CS, and SDA signals. SCK only drive high / low only while accessing EEPROM otherwise it is tri-stated and internally pulled down.              |  |

| CS           | B5/PD/T    | 17                        | EEPROM Chip Select. CS is asserted high synchronously with respect to rising edge of SCK as chip select signal. CS drives high / low only while accessing EEPROM otherwise it is tri-stated and internally pulled down.                       |  |

| SDA          | B5/PU/T    | 15                        | EEPROM Data. SDA is the serial output data to EEPROM's data input pin and is<br>synchronous with respect to the rising edge of SCK. SDA drives high / low only while<br>accessing EEPROM otherwise it is tri-stated and internally pulled up. |  |

| Misc. Pins   |            |                           |                                                                                                                                                                                                                                               |  |

| RESET#       | I5/PU/S    | 18                        | Extrernal chip reset input. Active low. This input feeds to the internal power-on reset circuitry, which provides the main reset source of this chip.                                                                                         |  |

| WAKEUP#      | I3/PU/S    | 41                        | Remote-wakeup trigger from external pin. WAKEUP# should be asserted low for more than 2 cycles of 25 MHz clock to be effective.                                                                                                               |  |

| SLF_PWR      | I5/PD/S    | 20                        | Self_power Indication Input.<br>0: will indicate to Host that this device is a bus-powered device.<br>1: will indicate to Host that this device is a self-powered device.                                                                     |  |

| GPIO[3]      | B3/PD      | 3                         | General Purpose Input/Output Pin 3.                                                                                                                                                                                                           |  |

| GPIO[2]      | B3/PD      | 4                         | General Purpose Input/Output Pin 2.                                                                                                                                                                                                           |  |

| GPIO[1]      | B3/PD      | 5                         | General Purpose Input/Output Pin 1.                                                                                                                                                                                                           |  |

| GPIO[0]/PME  | B3/PD      | 6                         | General Purpose Input/Output Pin 0 or PME (Power Management Event). This pin is an input pin by default after power-on reset. GPIO[0] also can be defined as PME output to indicate wake up event detected.                                   |  |

| MFA[3]       | B3         | 7                         | It is a multi-function pin. It acts as a USB SuperSpeed indicator on power up. It can be defined as a GPIO pin. Please refer to Table 3 on page 8.                                                                                            |  |

| MFA[2]       | B3         | 8                         | It is a multi-function pin. It acts as an Ethernet PHY LED indicator (Link 10/100/1000+Active) by default. It can be defined as a GPIO pin. Please refer to Table 3 on page 8.                                                                |  |

| MFA[1]       | B3         | 13                        | It is a multi-function pin. It acts as an Ethernet PHY LED indicator (Link 10/100/1000) by default and can be a GPIO pin. Please refer to Table 3 on page 8.                                                                                  |  |

| MFA[0]       | B3         | 14                        | It is a multi-function pin. It acts as an Ethernet PHY LED indicator (Active) and can be a GPIO pin. Please refer to Table 3 on page 8.                                                                                                       |  |

| NC           | I3/PD/S    | 68                        | Test pin. User can keep this pin NC.                                                                                                                                                                                                          |  |

| NC           | I3/PD      | 1                         | Test pin. User can keep this pin NC.                                                                                                                                                                                                          |  |

| NC           | I3/PD      | 2                         | Test pin. User can keep this pin NC.                                                                                                                                                                                                          |  |

| RESERVED     | 13/S       | 66                        | Test pin. User should pull down this pin.                                                                                                                                                                                                     |  |

| RESERVED     | 13/S       | 67                        | Test pin. User should pull down this pin.                                                                                                                                                                                                     |  |

| RESERVED     | 13         | 46                        | Test pin. User should pull down this pin.                                                                                                                                                                                                     |  |

| NC           | O3         | 11, 36, 44,<br>51, 52, 64 | Test pin. NC.                                                                                                                                                                                                                                 |  |

| Power and G  | round Pins |                           |                                                                                                                                                                                                                                               |  |

| A3V3         | Р          | 25                        | Analog Power for USB 3.0 transceiver. 3.3 V.                                                                                                                                                                                                  |  |

| GND_3V3      | Р          | 22                        | Analog Ground for USB 3.0 transceiver.                                                                                                                                                                                                        |  |

| U3TXVDDQ     | Р          | 26                        | Analog Power for USB 3.0 transceiver. 1.2 V.                                                                                                                                                                                                  |  |

| U3TXVSS      | Р          | 28, 30                    | Analog Ground for USB 3.0 transceiver.                                                                                                                                                                                                        |  |

## Pin Description (continued)

| Pin Name | Туре | Pin No.           | Pin Description                              |  |

|----------|------|-------------------|----------------------------------------------|--|

| U3RXVDDQ | Р    | 31                | Analog Power for USB 3.0 transceiver. 1.2 V. |  |

| U3RXVSS  | Р    | 33, 35            | Analog Ground for USB 3.0 transceiver.       |  |

| E12VDDQ  | Р    | 48                | Analog Power for Ethernet PHY. 1.2 V.        |  |

| E33VDDQ  | Р    | 49                | Analog Power for Ethernet PHY. 3.3 V.        |  |

| E12VCC   | Р    | 55, 61            | Analog Power for Ethernet PHY. 1.2 V.        |  |

| E33VCC   | Р    | 58                | Analog Power for Ethernet PHY. 3.3 V.        |  |

| CVDDQ    | Р    | 37                | Digital I/O Power for Clock pins. 3.3 V.     |  |

| VSS      | Р    | 40                | Digital Ground for clock pins.               |  |

| DVDD     | Р    | 10, 19, 45,<br>65 | Digital Core Power. 1.2 V.                   |  |

| DVSS     | Р    | 9                 | Digital Ground to E-pad                      |  |

| VIO      | Р    | 12, 43            | Digital I/O Power. 3.3 V.                    |  |

## Settings

#### Hardware Setting for Operation Mode and Multi-Function Pins

The following hardware settings define the desired operation mode and some multi-function pin configurations. The logic levels shown on setting the pins below are sampled from the chip I/O pins during power on reset based on the setting of the pin's pull-up or pull-down resistor in the schematic.

■ EEPROM Offset 05h, Flag[4]: Defines the multi-function pin GPIO[0] / PME

GPIO[0] is a general purpose I/O normally controlled by vendor commands. User can change this pin to operate as a PME (Power Management Event) for remote wake up. Please refer to Flag (EEPROM: 05h) on page 15 for detailed description of "Flag" of bit 4 (PME\_PIN).

GPIO[1] pin: Determines whether this chip will go to Default WOL (Wake-On-LAN) Ready Mode after power on reset.

#### Table 1. GPIO[1] Description

| GPIO[1] | Description                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Normal operation mode. By default, internal pull-up resistor (4.7 K $\Omega$ ) is enabled.                                                                                                 |

|         | Enable Default WOL Ready Mode. Notice that the external pulled-up resistor must be 4.7 K $\Omega$ .<br>For more details, please refer to Default Wake-On-LAN (DWOL) Ready Mode on page 11. |

■ GPIO[2] pin: Determines whether SSTXP swaps with SSTXM and SSRXP swaps with SSRXM for USB3.0 PHY.

#### Table 2. GPIO[2] Description

| GPIO[2] | Description                                                                           |

|---------|---------------------------------------------------------------------------------------|

| 0       | Disable swapping. By default, internal pull-up resistor (4.7 K $\Omega$ ) is enabled. |

| 1       | Enable swapping. Notice that the external pulled-up resistor must be 4.7 K $\Omega$ . |

■ MFA[3] ~ MFA[0] pins: There are 4 multi-function pins. They can be used either for driving indicator LEDs or as normal GPIOs controlled by vendor command PIN Control Register MFA\_EN.

#### Table 3. MFA\_3 ~ MFA\_0 pin configuration

| PIN Name | Default Definition                         | Section LED Mode<br>(EEPROM: 42h) on<br>page 16 | MFA Control Register |

|----------|--------------------------------------------|-------------------------------------------------|----------------------|

| MFA[3]   | LED_USB indicator (Super-speed)            | LED_3                                           | MFAIO_3              |

| MFA[2]   | Programmable LED (Link 10/100/1000+Active) | LED_2                                           | MFAIO_2              |

| MFA[1]   | Programmable LED (Link 10/100/1000)        | LED_1                                           | MFAIO_1              |

| MFA[0]   | Programmable LED (Active)                  | LED_0                                           | MFAIO_0              |

### **Functional Overview**

#### USB Core and Interfaces

The USB core is made up of USB 3.0 PHY and Device Controller. The USB 3.0 PHY processes USB Physical layer signals. The USB 3.0 Device Controller is interfaced with USB 3.0 PHY by PIPE/UTMI buses and it processes packets of link layer and protocol layer. The USB 3.0 Device Controller supports Bulk IN, Bulk OUT and Interrupt IN transfers for data transactions.

#### **Energy Efficient Ethernet (EEE)**

GX3 supports IEEE 802.3az, also known as Energy Efficient Ethernet (EEE) at 10Mbps, 100Mbps and 1000Mbps. It also supports EEE specified negotiation method to enable link partner to determine whether EEE is supported and to select the best set of parameters common to both devices. It provides a protocol to coordinate transitions to/from a lower power consumption level (Low Power Idle mode) based on link utilization. When no packets are being transmitted, the system goes to Low Power Idle mode to save power. Once packets need to be transmitted, the system returns to normal mode, and starts transmitting packets without changing the link status and without dropping/corrupting frames.

During the Low Power Idle mode, most of the circuits are disabled to save power. However, the transition time to/from Low Power Idle mode is kept small enough to be transparent to the upper layer protocols and applications.

#### 10/100/1000M Ethernet PHY

The 10/100/1000M Ethernet PHY is compliant with 10Base-T, 100Base-TX, and 1000Base-T IEEE 802.3 standards. It provides all the necessary physical layer functions to transmit and receive Ethernet packets over CAT 5 UTP cable or CAT 3 UTP (10 Mbps only) cable. It uses state-of-the-art DSP technology and an Analog Front End (AFE) to enable high-speed data transmission and reception over UTP cable. Crossover Detection & Auto-Correction, polarity correction, adaptive equalization, cross-talk cancellation, echo cancellation, timing recovery, and error correction functions are also implemented.

#### MAC Core

The MAC core supports IEEE 802.3, IEEE 802.3u and IEEE 802.3ab MAC sub-layer functions, such as basic MAC frame receive and transmit, CRC checking and generation, filtering, forwarding, flow-control in full-duplex mode, and collision-detection and handling in half-duplex mode, etc. It supports virtual local area network (VLAN)-tagged frames according to IEEE 802.1Q specification in both transmit and receive functions. The MAC core also implements CRC-32 checking at full-speed using a multi-stage, cyclic redundancy code (CRC) calculation architecture with optional forwarding of the frame check sequence (FCS) field to the user application CRC-32 generation and append on transmit.

#### Checksum Offload Engine (COE)

The Checksum Offload Engine (COE) supports IPv4, IPv6, layer 4 (TCP, UDP, ICMP, ICMPv6 and IGMP) header processing functions and real time checksum calculation in the hardware.

The COE supports the following features in layer 3:

- IP header parsing, including IPv4 and IPv6

- IPv6 routing header type 0 supported

- IPv4 header checksum check and generation (There is no checksum field in IPv6 header)

- Detecting on RX direction for IP packets with error header checksum

- The COE supports the following features in layer 4:

- TCP and UDP checksum check and generation for non-fragmented packet

- TCP Large Send Offload V1

- ICMP, ICMPv6 and IGMP message checksum check and generation for non-fragmented packet

#### Memory Arbiter

The memory arbiter block stores received MAC frames into on-chip SRAM (packet buffer) and then forward it to the USB bus upon request from the USB host via Bulk IN transfer. It also monitors the packet buffer usage in full-duplex mode for triggering PAUSE frame (or in half-duplex mode to activate Back pressure jam signal) transmission out on transmit (TX) direction. The memory arbiter block is also responsible for storing MAC frames received from the USB host via Bulk OUT transfer and scheduling transmission out towards Ethernet network.

#### USB to Ethernet Bridge

The USB to Ethernet bridge block converts Ethernet MAC frames into USB packets or vice-versa. This block supports burst transfer mechanism to offload software burden and to offer very high packet transfer throughput over USB bus.

#### SEEPROM Loader Interface

The SEEPROM loader interface is responsible for reading configuration data automatically from the external serial EEPROM after power-on reset.

If the content of EEPROM offset 05h (low byte) is equal to (0xFF - SUM [EEPROM offset 03h ~ 04h]), the EEPROM is the first candidate for SEEEPROM loader.

#### GPIOs and LED

There are 4 GPIO pins (GPIO[0/1/2/3]) and 4 multi-function pins group A (MFA[0/1/2/3]) provided by this chip. The MFA[0/1/2/3] pins are also used for LED indication. Please refer to LED Mode (EEPROM: 42h) on page 16 for details.

#### PLL Clock Generator

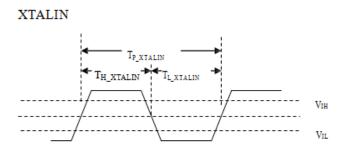

GX3 includes an on-chip internal oscillator circuit for 25 MHz which allows the chip to operate cost effectively with just external 25 MHz crystals.

The external 25 MHz crystal or oscillator, via pins XTALIN/XTALOUT, provides the reference clock to internal oscillator circuit to generate clock for the embedded Ethernet PHY, embedded USB PHY, and base clock for the ASIC.

The external 25 MHz Crystal spec is listed in below table. For more details on crystal timing, please refer to Clock Timing on page 28 and CYUSB3610 demo board reference schematic.

#### Table 4. External 25 MHz Crystal Units specifications

| Parameter                                            | Symbol         | Typical Value       |

|------------------------------------------------------|----------------|---------------------|

| Nominal Frequency                                    | f <sub>O</sub> | 25.000000 MHz       |

| Oscillation Mode                                     |                | Fundamental         |

| Frequency Tolerance (@25 °C)                         |                | <u>+</u> 30 ppm     |

| Frequency Stability Over Operating Temperature Range |                | <u>+</u> 30 ppm     |

| Equivalent Series Resistance                         | ESR            | 70 Ω max.           |

| Load Capacitance                                     | CL             | 12 pF               |

| Drive Level                                          |                | 350 µW              |

| Operation Temperature Range                          |                | 0 °C∼ +70 °C        |

| Aging                                                |                | <u>+</u> 3 ppm/year |

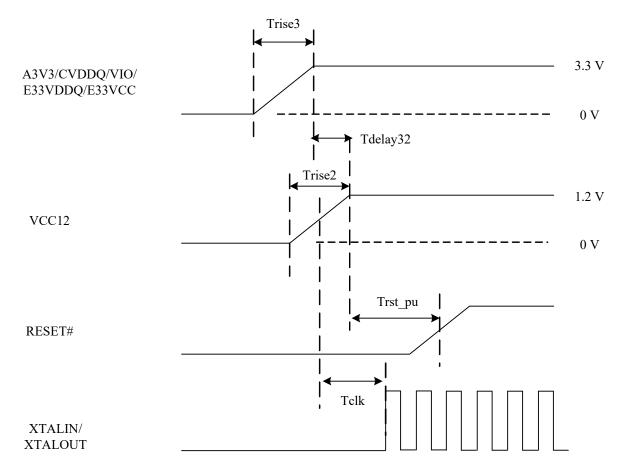

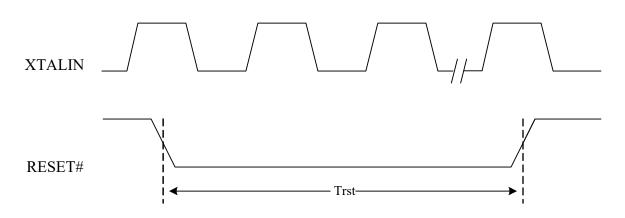

#### **Reset Generation**

GX3 integrates an on-chip power-on-reset circuit, which simplifies the external reset circuitry on the board. The power-on-reset circuit generates a reset pulse after 1.2 V core power ramps up to 0.72 V (typical threshold). The external reset pin, RESET#, can be directly connected to the input of the power-on-reset circuit and can also be used as an additional hardware reset source. For more details on RESET# timing, please refer to Reset Timing on page 28.

## Default Wake-On-LAN (DWOL) Ready Mode

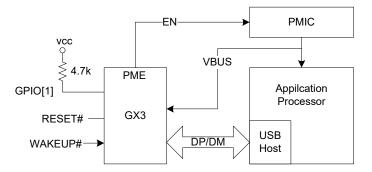

This Default WOL Ready Mode application is different from normal operation where GX3 Suspend/Resume state usually has to be configured by software driver during normal system operation. This application applies to a system that uses a predefined remote wakeup event to turn on the system power supply and its peripheral circuits without having any system software running in the beginning. This is quite useful when a system has been powered down already and a user needs to power on the system remotely.

GX3 can be configured to support Default WOL Ready Mode, where no system driver is required to configure its WOL related settings after power on reset. A system design usually partitions its power supply into two or more groups and the GX3 is supplied with an independent power separated from the system processor. The power supply of GX3 is usually available as soon as power plug is connected. The power supply of system processor remains off initially when power plug is connected and is controlled by GX3's PME pin, which can be activated whenever GX3 detects a pre-defined wakeup event such as valid Magic Packet reception or the WAKEUP# pin trigger. To reduce power consumption, initially the USB host controller communicating with GX3 can also be unpowered as the system processor.

The PME pin of GX3 can control the power management IC (PMIC) to power up the system processor along with the USB host controller, which will perform USB transactions with GX3 after both have been initialized. The pin polarity of PME is configured as high active when enabling Default WOL Ready Mode. Note that the GX3 must be in self-power (via setting EEPROM Flag [0]) mode for this function.

#### Procedure to Enable Default WOL Ready Mode

To enable Default WOL Ready Mode, configure GPIO[0] pin as PME (via setting EEPROM Flag [12]) and have GPIO[1] pulled-up with a 4.7K resistor. After power on reset, GX3 will disable most functions including USB transceiver (see Note 2) but enable Magic Packet detector logic, internal Ethernet PHY and its auto-negotiation function to be ready to

receive Magic Packet. When a valid Magic Packet is received, GX3 will assert the PME pin to indicate to system processor the wakeup event. The PME pin, when being configured as static level output signal (via setting EEPROM Flag [15], see Note 3), can be used to control the power management IC to enable system power supply. After asserting the PME pin, GX3 will also exit from the Default WOL Ready Mode and revert back to normal operation mode to start normal USB device detection, handshaking, and enumeration.

The PME pin, when being configured as static level output signal, maintains its signal level until RESET# is asserted again. If RESET# to GX3 is asserted with GPIO[1] pulled-up, the Default WOL Ready Mode will be re-entered. Otherwise (GPIO[1] being pulled-down), it will enter into normal operation mode and the normal USB device detection, handshaking and enumeration process should take place right after RESET# negation.

Notes

- For complete truth table of wakeup events supported, please refer to below on the "GPIO[1] = 1" setting. When the Default WOL Ready Mode is enabled, the DP/DM pins of GX3 will be in tri-state. 1

- 2

- Please refer to Flag (EEPROM: 05h) on page 15. The bit [15:12] of Flag (PME\_IND, PME\_TYP, PME\_POL, PME\_PIN) = 0111. 3.

It is recommended that VBUS pin be connected to system power group directly. This way the VBUS will become HIGH when power management IC enables the 4 system power supply.

# COPPRESS EMEDDED IN TOMORROW

Table 5. Remote Wakeup Truth Table

|                                                |                                             | change EX- Device<br>change TWAKE_N wakes up<br>stected On pin<br>PHY pin | EX-<br>TWAKE_N<br>pin | TWAKE_N<br>pin | TWAKE_N<br>pin × | TWAKE_N<br>pin   | TWAKE_N<br>pin   | TWAKE_N<br>pin             | Twake_n<br>pin_            |

|------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------|-----------------------|----------------|------------------|------------------|------------------|----------------------------|----------------------------|

|                                                | LINK status<br>change<br>detected On<br>PHY |                                                                           |                       |                |                  |                  |                  |                            |                            |

| Link status<br>change<br>detected On<br>PHY    |                                             |                                                                           |                       | ×              | ×                | ×                | X<br>Yes         | X                          | Y                          |

|                                                |                                             |                                                                           | ×                     |                |                  | Yes              | Yes              | Yes                        | , Yes                      |

| ing a<br>sup<br>ne                             |                                             |                                                                           |                       | Yes            |                  | Ye               | , Ye             | ×                          | €                          |

|                                                |                                             | ×                                                                         |                       | Yes            |                  |                  |                  |                            |                            |

| Host sends<br>resume<br>signal<br>J-> K        | Ч-<br>Ч                                     |                                                                           |                       |                |                  |                  |                  |                            |                            |

| RWLC         GPIO_1 <sup>[5]</sup> X         0 | 0                                           |                                                                           | 0                     | 0              |                  | 0                | 0 0              | 0 0 0                      | 0000                       |

| RWLC                                           |                                             | ×                                                                         | ×                     | 0              |                  | 0                | - 0              | 0                          | 0 X                        |

|                                                | KWWI                                        | ×                                                                         | ×                     | 0              |                  | <u> </u>         | - 0              | 0 0                        | - 0 0 X                    |

|                                                | RWWF RWMP                                   | ×                                                                         | ×                     | <del>.</del>   | ¢                | 5                | - o              |                            | - • • ×                    |

| Cot Footure                                    | standard<br>command                         | ×                                                                         | 0                     | ~              |                  | -                |                  |                            |                            |

|                                                | RWU bit of<br>Flag byte in<br>EEPROM        | ×                                                                         | 0                     | -              |                  | <del>.    </del> | ~ ~              |                            |                            |

|                                                | Waken Up<br>by                              | USB Host                                                                  | Device                | Device         |                  | Device           | Device<br>Device | Device<br>Device<br>Device | Device<br>Device<br>Device |

Note 5. About Default WOL Ready Mode, please refer to GPIOs and LED on page 10.

Document Number: 001-94768 Rev. \*C

#### Flow Chart of Default WOL Ready Mode

## Serial EEPROM Memory Map

#### Table 6. Serial EEPROM Memory Map

| EEPROM OFFSET | HIGH BYTE                              | LOW BYTE                                 |  |  |  |

|---------------|----------------------------------------|------------------------------------------|--|--|--|

| 00h           | Node ID 1                              | Node ID 0 (Note 6)                       |  |  |  |

| 01h           | Node ID 3                              | Node ID 2                                |  |  |  |

| 02h           | Node ID 5                              | Node ID 4                                |  |  |  |

| 03h           | PID_HB                                 | PID_LB                                   |  |  |  |

| 04h           | VID_HB                                 | VID_LB                                   |  |  |  |

| 05h           | Flag                                   | EEPROM Checksum (Note 7)                 |  |  |  |

| 06h           | Reserved                               | Reserved                                 |  |  |  |

| 07h           | Max. Power for Self Power              | Max. Power for Bus Power                 |  |  |  |

| 08h           | EndPoint1 for SS/HS                    | EndPoint1 for FS                         |  |  |  |

| 09h           | Language ID High Byte                  | Language ID Low Byte                     |  |  |  |

| 0Ah           | Length of Product String (bytes)       | Offset of Product String (0Eh)           |  |  |  |

| 0Bh           | Length of Manufacturer String (bytes)  | Offset of Manufacturer String (1Ah)      |  |  |  |

| 0Ch           | Length of Serial Number String (bytes) | Offset of Serial Number String (26h)     |  |  |  |

| 0Dh           | Length of BOS-type Descriptor (bytes)  | Offset of BOS-type Descriptor (2Dh)      |  |  |  |

| 19~0Eh        | Product String:                        | (Max.) 24 bytes                          |  |  |  |

| 25~1Ah        | Manufacturer Strin                     | ng: (Max.) 24 bytes                      |  |  |  |

| 2C~26h        | Serial Number String: (Max.) 14 bytes  |                                          |  |  |  |

| 3B~2Dh        | BOS-type Descriptor: (Max.) 30 bytes   |                                          |  |  |  |

| 3Ch           | Reserved                               | Max. Burst: [7:4] for EP3, [3:0] for EP2 |  |  |  |

| 41~3Dh        | Fixed_patte                            | rn (10 bytes)                            |  |  |  |

| 42h           | LED_Mode_HB                            | LED_Mode_LB                              |  |  |  |

Notes

- The Node ID 0 value cannot be set to 0xFF and 1st bit of Node ID 0 cannot be set to "1" (i.e. cannot be set to multicast MAC address).

The value of EEPROM Checksum field located at EEPROM offset 05h (low byte). The correct value must be equal to (0xFF SUM [EEPROM offset 03h ~ 04h]). If SUM [EEPROM offset 03h ~ 04h] has carry, please add '1' to its result.

Total usage is about 134 bytes.

#### **Detailed Description**

The following sections provide detailed descriptions for some of the fields in memory maps of serial EEPROM.

#### Node ID (00~02h)

The Node ID 0 to 5 bytes represent the MAC address of the device, for example, if MAC address = 04-23-45-67-89-AB, then Node ID 0 = 04h, Node ID 1 = 23h, Node ID 2 = 45h, Node ID 3 = 67h, Node ID 4 = 89h, and Node ID 5 = ABh. Default values: Node ID  $\{0, 1, 2, 3, 4, 5\} = 00-0E-C6-F9-D0-00$ .

#### Flag (EEPROM: 05h)

#### Table 7. Flag (EEPROM: 05h)

| Bit 7   | Bit 6    | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---------|---------|-------|-------|-------|-------|

| PME_IND | PME_TYPE | PME_POL | PME_PIN | 0     | 0     | WOLLP | RWU   |

#### RWU: Remote Wakeup support.

1: Indicate that this device supports Remote Wakeup (default).

0: Not supported.

WOLLP: Wake-On-LAN Low Power function.

1: Enabled (default).

0: Disabled.

PME\_PIN: PME / GPIO[0].

1: Set GPIO[0] pin as PME (default).

0: GPIO[0] pin is controlled by vendor command.

PME\_POL: PME pin active Polarity.

1: PME active high (default).

0: PME active low.

PME\_TYP: PME I/O Type.

1: PME output is a Push-Pull driver (default).

0: PME output to function as an open-drain buffer.

PME\_IND: PME indication.

1: A 1.363 ms pulse active when detecting wake-up event.

0: A static signal active when detecting wake-up event (default).

#### Max. Power for Self/Bus Power (07h)

They are Max power values' setting of powered device for EEPROM at offset 07h.

The default value of Bus Power is 3Eh.

For USB 3.0, the power value is 496 mA (Unit = 8 mA).

For USB 2.0, the power value is 248mA (Unit = 4 mA).

Self power setting follows conversion above.

#### EndPoint1 for SS/HS/FS (EEPROM:08h)

The time interval (named "bInterval") for polling Interrupt IN endpoint 1 for data transfers of SuperSpeed/High-Speed/Full-Speed is stored at EEPROM offset 08h. It is expressed in frames or microframes depending on the device operating speed (i.e. either 1 millisecond or 125 µs units).

The default "bInterval" value is 0Bh for Super-Speed/High-Speed (the polling time of endpoint  $1 = 2^{(11-1)} \times 125 \ \mu s = 128 \ m s$ ) and is 80h for Full-Speed (the polling time of endpoint  $1 = 128 \times 1 \ m s = 128 \ m s$ ).

#### Max. Burst for EP3/EP2 (EEPROM: 3Ch)

This value is bMaxBurst field in SS endpoint companion descriptor.

#### LED Mode (EEPROM: 42h)

LED Mode defines the indication setting for LED\_0/1/2/3 function of MFA[0/1/2/3] pins.

#### Table 8. Bit 7~Bit 0: LED\_Mode\_LB

| Bit7     | Bit6    | Bit5        | Bit4        | Bit3      | Bit2     | Bit1    | Bit0        |

|----------|---------|-------------|-------------|-----------|----------|---------|-------------|

| LED1_100 | LED1_10 | LED1_Active | LED0_Duplex | LED0_1000 | LED0_100 | LED0_10 | LED0_Active |

#### Table 9. Bit 15~Bit 8: LED\_Mode\_HB

| Bit15 | Bit14       | Bit13     | Bit12    | Bit11   | Bit10       | Bit9        | Bit8      |

|-------|-------------|-----------|----------|---------|-------------|-------------|-----------|

| 1     | LED2_Duplex | LED2_1000 | LED2_100 | LED2_10 | LED2_Active | LED1_Duplex | LED1_1000 |

Note: Bit 15 must be '1' to enable the LED\_mode setting; otherwise, it will work at default LED mode. The LED mode table is as below:

#### Table 10. LED Mode Setting Table

|       | Full duplex | Lin  | k speed (Mi | ops) | Active  | Description of Indication                                                      |

|-------|-------------|------|-------------|------|---------|--------------------------------------------------------------------------------|

|       | Full duplex | 1000 | 100         | 10   | (TX/RX) | Description of indication                                                      |

| Bit   | 4           | 3    | 2           | 1    | 0       |                                                                                |

| _ED_0 | 0           | 0    | 0           | 0    | 0       | USB3.0 Super Speed: It turns ON when device<br>operates at USB3.0 Super Speed. |

|       | 0           | 0    | 0           | 0    | 1       | Active (Default for LED0)                                                      |

|       | 0           | 0    | 0           | 1    | 0       | Link 10                                                                        |

|       | 0           | 0    | 0           | 1    | 1       | Link 10+Active                                                                 |

|       | 0           | 0    | 1           | 0    | 0       | Link 100                                                                       |

|       | 0           | 0    | 1           | 0    | 1       | Link 100+Active                                                                |

|       | 0           | 0    | 1           | 1    | 0       | Link 100/10                                                                    |

|       | 0           | 0    | 1           | 1    | 1       | Link 100/10+Active                                                             |

|       | 0           | 1    | 0           | 0    | 0       | Link 1000                                                                      |

|       | 0           | 1    | 0           | 0    | 1       | Link 1000+Active                                                               |

|       | 0           | 1    | 0           | 1    | 0       | Link 1000/10                                                                   |

|       | 0           | 1    | 0           | 1    | 1       | Link 1000/10+Active                                                            |

|       | 0           | 1    | 1           | 0    | 0       | Link 1000/100                                                                  |

|       | 0           | 1    | 1           | 0    | 1       | Link 1000/100+Active                                                           |

|       | 0           | 1    | 1           | 1    | 0       | Link 1000/100/10                                                               |

|       | 0           | 1    | 1           | 1    | 1       | Link 1000/100/10+Active                                                        |

|       | 1           | 0    | 0           | 0    | 0       | Full duplex                                                                    |

| Bit   | 9           | 8    | 7           | 6    | 5       |                                                                                |

| _ED_1 | 0           | 0    | 0           | 0    | 0       | USB3.0 Super Speed: It turns ON when device operates at USB3.0 Super Speed.    |

|       | 0           | 0    | 0           | 0    | 1       | Active                                                                         |

|       | 0           | 0    | 0           | 1    | 0       | Link 10                                                                        |

|       | 0           | 0    | 0           | 1    | 1       | Link 10+Active                                                                 |

|       | 0           | 0    | 1           | 0    | 0       | Link 100                                                                       |

|       | 0           | 0    | 1           | 0    | 1       | Link 100+Active                                                                |

|       | 0           | 0    | 1           | 1    | 0       | Link 100/10                                                                    |

|       | 0           | 0    | 1           | 1    | 1       | Link 100/10+Active                                                             |

|       | 0           | 1    | 0           | 0    | 0       | Link 1000                                                                      |

|       | 0           | 1    | 0           | 0    | 1       | Link 1000+Active                                                               |

|       | 0           | 1    | 0           | 1    | 0       | Link 1000/10                                                                   |

|       | 0           | 1    | 0           | 1    | 1       | Link 1000/10+Active                                                            |

|       | 0           | 1    | 1           | 0    | 0       | Link 1000/100                                                                  |

|       | 0           | 1    | 1           | 0    | 1       | Link 1000/100+Active                                                           |

|       | 0           | 1    | 1           | 1    | 0       | Link 1000/100/10                                                               |

|       |             | 1    | t .         | 4    | 1       | Link 1000/100/10+Active                                                        |

|       | 0           | 1    | 1           | 1    |         |                                                                                |

#### Table 10. LED Mode Setting Table (continued)

|       | Full duplex | Lin  | k speed (Mk | ops) | Active  | Description of Indication                                                                                                                                                                                         |

|-------|-------------|------|-------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Full duplex | 1000 | 100         | 10   | (TX/RX) | Description of indication                                                                                                                                                                                         |

| Bit   | 14          | 13   | 12          | 11   | 10      |                                                                                                                                                                                                                   |

| LED_2 | 0           | 0    | 0           | 0    | 0       | USB3.0 Super Speed: It turns ON when device operates at USB3.0 Super Speed.                                                                                                                                       |

|       | 0           | 0    | 0           | 0    | 1       | Active                                                                                                                                                                                                            |

|       | 0           | 0    | 0           | 1    | 0       | Link 10                                                                                                                                                                                                           |

|       | 0           | 0    | 0           | 1    | 1       | Link 10+Active                                                                                                                                                                                                    |

|       | 0           | 0    | 1           | 0    | 0       | Link 100                                                                                                                                                                                                          |

|       | 0           | 0    | 1           | 0    | 1       | Link 100+Active                                                                                                                                                                                                   |

|       | 0           | 0    | 1           | 1    | 0       | Link 100/10                                                                                                                                                                                                       |

|       | 0           | 0    | 1           | 1    | 1       | Link 100/10+Active                                                                                                                                                                                                |

|       | 0           | 1    | 0           | 0    | 0       | Link 1000                                                                                                                                                                                                         |

|       | 0           | 1    | 0           | 0    | 1       | Link 1000+Active                                                                                                                                                                                                  |

|       | 0           | 1    | 0           | 1    | 0       | Link 1000/10                                                                                                                                                                                                      |

|       | 0           | 1    | 0           | 1    | 1       | Link 1000/10+Active                                                                                                                                                                                               |

|       | 0           | 1    | 1           | 0    | 0       | Link 1000/100                                                                                                                                                                                                     |

|       | 0           | 1    | 1           | 0    | 1       | Link 1000/100+Active                                                                                                                                                                                              |

|       | 0           | 1    | 1           | 1    | 0       | Link 1000/100/10                                                                                                                                                                                                  |

|       | 0           | 1    | 1           | 1    | 1       | Link 1000/100/10+Active                                                                                                                                                                                           |

|       | 1           | 0    | 0           | 0    | 0       | Full duplex                                                                                                                                                                                                       |

|       |             |      |             |      |         |                                                                                                                                                                                                                   |

| Bit   | 4           | 3    | 2           | 1    | 0       |                                                                                                                                                                                                                   |