# Reprogrammable 2048 x 8 Registered PROM

#### **Features**

- Windowed for reprogrammability

- CMOS for optimum speed/power

- High speed

- 25 ns max set-up

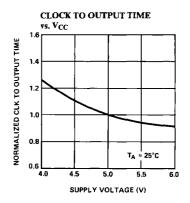

- 12 ns clock to output

- Low power

- 330 mW (commercial) for

- -35 ns, -45 ns

- 660 mW (military)

- Programmable synchronous or asynchronous output enable

- On-chip edge-triggered registers

- Programmable asynchronous register (INIT)

- EPROM technology, 100% programmable

- Slim, 300 mil, 24 pin plastic or hermetic DIP

- 5V ±10% V<sub>CC</sub>, commercial and military

- TTL compatible I/O

- Direct replacement for bipolar PROMs

- Capable of withstanding greater than 2000V static discharge

#### **Selection Guide**

|                         |                              |            | 7C245-25 | 7C245-35 | 7C245-45 |

|-------------------------|------------------------------|------------|----------|----------|----------|

| Maximum Setup Time (ns) |                              |            | 25       | 35       | 45       |

| Maximum Clock to Outp   | Maximum Clock to Output (ns) |            | 12       | 15       | 25       |

| Maximum Operating       | STD                          | Commercial | 90       | 90       | 90       |

| Current (mA)            | 315                          | Military   |          | 120      | 120      |

|                         | L                            | Commercial |          | 60       | 60       |

## **Product Characteristics**

The CY7C245 is a high performance 2048 word by 8 bit electrically Programmable Read Only Memory packaged in a slim 300 mil plastic or hermetic DIP. The ceramic package may be equipped with an erasure window; when exposed to UV light the PROM is erased and can then be reprogrammed. The memory cells utilize proven EPROM floating gate technology and byte-wide intelligent programming algorithms.

The CY7C245 replaces bipolar devices and offers the advantages of lower power, reprogrammability, superior performance and high programming yield. The EPROM cell requires only 13.5V for the supervoltage and low current requirements allow for gang programming. The EPROM cells allow for each memory location to be tested 100%, as each location is written into, erased, and repeatedly exercized prior to encapsulation. Each PROM is also tested for AC performance to guarantee that after customer programming the product will meet AC specification limits.

The CY7C245 has an asynchronous initialize function (INIT). This function acts as a 2049th 8-bit word loaded into the on-chip register. It is user programmable with any desired word or may be used as a PRESET or CLEAR function on the outputs.

#### **Maximum Ratings**

| guidelines, not tested.)                                           |

|--------------------------------------------------------------------|

| Storage Temperature $\dots -65^{\circ}C$ to $+150^{\circ}C$        |

| Ambient Temperature with Power Applied55°C to + 125°C              |

| Supply Voltage to Ground Potential (Pin 24 to Pin 12)0.5V to +7.0V |

| DC Voltage Applied to Outputs<br>in High Z State                   |

(Above which the useful life may be impaired. For user

DC Input Voltage

-3.0V to +7.0V

DC Program Voltage (Pins 7, 18, 20)

13.0V

UV Erasure

.7258 Wsec/cm²

Static Discharge Voltage

> 2001V

(Per MIL-STD-883 Method 3015)

Latchup Current

> 200 mA

#### **Operating Range**

|   | Range       | Ambient<br>Temperature | v <sub>cc</sub> |  |

|---|-------------|------------------------|-----------------|--|

| C | Commercial  | 0°C to +70°C           | 5V ± 10%        |  |

| N | Iilitary[7] | -55°C to +125°C        | 5V ± 10%        |  |

#### Electrical Characteristics Over Operating Range<sup>[6]</sup>

| D               | Description                     | Test Conditions                                                      |            | 7C245I          | 35, 45 | 7C245-25        |      | 7C245-35, 45    |      | 71    |

|-----------------|---------------------------------|----------------------------------------------------------------------|------------|-----------------|--------|-----------------|------|-----------------|------|-------|

| Parameters      | Description                     | 1 est Condit                                                         | ions       | Min.            |        | Min.            | Max. | Min.            | Max. | Units |

| V <sub>OH</sub> | Output HIGH Voltage             | $V_{CC} = Min., I_{OH} = -V_{IN} = V_{IH} \text{ or } V_{IL}$        | 2.4        |                 | 2.4    |                 | 2.4  |                 | v    |       |

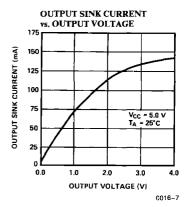

| $v_{OL}$        | Output LOW Voltage              | $V_{CC} = Min., I_{OL} = 16$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ |            | 0.4             |        | 0.4             |      | 0.4             | v    |       |

| $v_{IH}$        | Input HIGH Level                | Guaranteed Input Logic<br>Voltage for All Inputs <sup>[1]</sup>      | 2.0        | v <sub>cc</sub> | 2.0    | v <sub>cc</sub> | 2.0  | v <sub>cc</sub> | v    |       |

| V <sub>IL</sub> | Input LOW Level                 | Guaranteed Input Logic<br>Voltage for All Inputs[1                   |            | 0.8             |        | 0.8             |      | 0.8             | v    |       |

| I <sub>IX</sub> | Input Leakage Current           | $GND \leq V_{IN} \leq V_{CC}$                                        |            | -10             | + 10   | - 10            | +10  | - 10            | +10  | μА    |

| $v_{CD}$        | Input Clamp Diode<br>Voltage    | Note 5                                                               |            | Note 5          |        |                 |      |                 |      |       |

| I <sub>OZ</sub> | Output Leakage Current          | $GND \le V_O \le V_{CC}$<br>Output Disabled <sup>[3]</sup>           | -40        | + 40            | -40    | + 40            | -40  | +40             | μА   |       |

| Ios             | Output Short Circuit<br>Current | $V_{CC} = Max., V_{OUT} = 0.0V^{[2]}$                                |            | -20             | -90    | -20             | -90  | -20             | -90  | mA    |

| I <sub>CC</sub> | Power Supply Current            | $GND \leq V_{IN} \leq V_{CC}$                                        | Commercial |                 | 60     | _               | 90   |                 | 90   | mA    |

| 100             | z sc. supply current            | V <sub>CC</sub> = Max. Military                                      |            |                 |        |                 |      |                 | 120  |       |

# Capacitance<sup>[4]</sup>

| Parameters       | Description Test Conditions |                                | Max. | Units |

|------------------|-----------------------------|--------------------------------|------|-------|

| C <sub>IN</sub>  | Input Capacitance           | $T_A = 25^{\circ}C, f = 1 MHz$ | 5    | p.F   |

| C <sub>OUT</sub> | Output Capacitance          | $V_{CC} \approx 5.0V$          | 8    | ] "   |

#### Notes:

- These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment (see Notes on Testing).

- For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

- 3. For devices using the synchronous enable, the device must be clocked after applying these voltages to perform this measurement.

- Tested initially and after any design or process changes that may affect these parameters.

- The CMOS process does not provide a clamp diode. However, the CY7C245 is insensitive to -3V dc input levels and -5V undershoot pulses of less than 10 ns (measured at 50% point).

- See the last page of this specification for Group A subgroup testing information.

- 7. TA is the "instant on" case temperature.

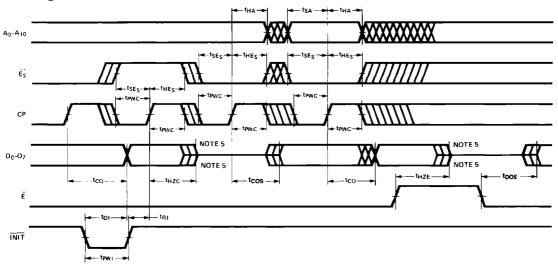

## Switching Characteristics Over Operating Range<sup>[8]</sup>

| Parameters       | Description                                    | 7C245-25 |      | 7C245-35 |      | 7C245-45 |      | Units |

|------------------|------------------------------------------------|----------|------|----------|------|----------|------|-------|

| I ai aiiictei 3  | Description                                    | Min.     | Max. | Min.     | Max. | Min.     | Max. | l     |

| t <sub>SA</sub>  | Address Setup to Clock HIGH                    | 25       |      | 35       |      | 45       |      | ns    |

| tHA              | Address Hold from Clock HIGH                   | 0        |      | 0        |      | 0        |      | ns    |

| tco              | Clock HIGH to Valid Output                     |          | 12   |          | 15   |          | 25   | ns    |

| tpwc             | Clock Pulse Width                              | 15       |      | 20       |      | 20       |      | ns    |

| t <sub>SES</sub> | E <sub>S</sub> Setup to Clock HIGH             | 12       |      | 15       |      | 15       |      | ns    |

| tHES             | Es Hold from Clock HIGH                        | 5        |      | 5        |      | 5        |      | ns    |

| t <sub>DI</sub>  | Delay from INIT to Valid Output                |          | 20   |          | 20   |          | 35   | ns    |

| tRI              | INIT Recovery to Clock HIGH                    | 15       |      | 20       |      | 20       |      | ns    |

| tpwi             | INIT Pulse Width                               | 15       |      | 20       |      | 25       |      | ns    |

| t <sub>COS</sub> | Valid Output from<br>Clock HIGH <sup>[1]</sup> |          | 15   |          | 20   |          | 30   | ns    |

| tHZC             | Inactive Output from Clock HIGH[1, 3]          |          | 15   |          | 20   |          | 30   | ns    |

| tDOE             | Valid Output from E LOW[2]                     |          | 15   |          | 20   |          | 30   | ns    |

| t <sub>HZE</sub> | Inactive Output from E HIGH <sup>[2, 3]</sup>  |          | 15   |          | 20   |          | 30   | ns    |

#### Notes:

- 1. Applies only when the synchronous (Es) function is used.

- 2. Applies only when the asynchronous (E) function is used.

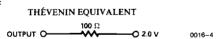

- Transition is measured at steady state High level 500 mV or steady state Low level + 500 mV on the output from the 1.5V level on the input with loads shown in Figure 1b.

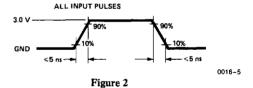

- 4. Tests are performed with rise and fall times of 5 ns or less.

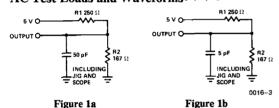

# AC Test Loads and Waveforms[5, 6, 7]

Equivalent to:

## **Functional Description**

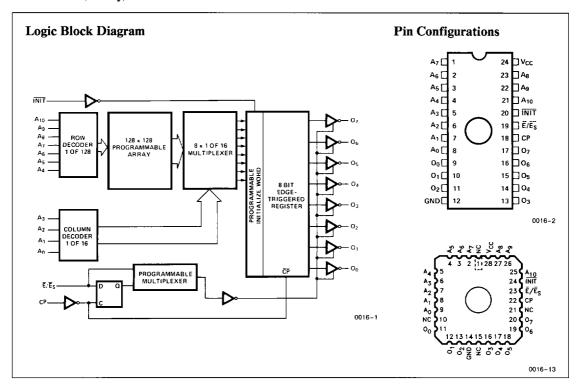

The CY7C245 is a CMOS electrically Programmable Read Only Memory organized as 2048 words x 8-bits and is a pin-for-pin replacement for bipolar TTL fusible link PROMs. The CY7C245 incorporates a D-type, master-slave register on chip, reducing the cost and size of pipelined microprogrammed systems and applications where accessed PROM data is stored temporarily in a register. Additional flexibility is provided with a programmable synchronous (Es) or asynchronous (E) output enable and asynchronous initialization (INIT).

Upon power-up the state of the outputs will depend on the programmed state of the enable function ( $\overline{E}_S$  or  $\overline{E}$ ). If the synchronous enable ( $\overline{E}_S$ ) has been programmed, the register will be in the set condition causing the outputs

- 5. See Figure 1a for all switching characteristics except tHZ.

- 6. See Figure 1b for tHZ.

- 7. All device test loads should be located within 2" of device outputs.

- See the last page of this specification for Group A subgroup testing information.

$(O_0-O_7)$  to be in the OFF or high impedance state. If the asynchronous enable (E) is being used, the outputs will come up in the OFF or high impedance state only if the enable (E) input is at a HIGH logic level. Data is read by applying the memory location to the address inputs  $(A_0-A_{10})$  and a logic LOW to the enable input. The stored data is accessed and loaded into the master flip-flops of the data register during the address set-up time. At the next LOW-to-HIGH transition of the clock (CP), data is transferred to the slave flip-flops, which drive the output buffers, and the accessed data will appear at the outputs  $(O_0-O_7)$ .

If the asynchronous enable (E) is being used, the outputs may be disabled at any time by switching the enable to a

0016-6

### Functional Description (Continued)

logic HIGH, and may be returned to the active state by switching the enable to a logic LOW.

If the synchronous enable (E<sub>S</sub>) is being used, the outputs will go to the OFF or high impedance state upon the next positive clock edge after the synchronous enable input is switched to a HIGH level. If the synchronous enable pin is switched to a logic LOW, the subsequent positive clock edge will return the output to the active state. Following a positive clock edge, the address and synchronous enable inputs are free to change since no change in the output will occur until the next low to high transition of the clock. This unique feature allows the CY7C245 decoders and sense amplifiers to access the next location while previously addressed data remains stable on the outputs.

System timing is simplified in that the on-chip edge triggered register allows the PROM clock to be derived directly from the system clock without introducing race conditions. The on-chip register timing requirements are similar to those of discrete registers available in the market. The CY7C245 has an asynchronous initialize input (INIT). The initialize function is useful during power-up and timeout sequences and can facilitate implementation of other sophisticated functions such as a built-in "jump start" address. When activated the initialize control input causes the contents of a user programmed 2049th 8-bit word to be loaded into the on-chip register. Each bit is programmable and the initialize function can be used to load any desired combination of "1"s and "0"s into the register. In the unprogrammed state, activating INIT will generate a register CLEAR (all outputs LOW). If all the bits of the initialize word are programmed, activating INIT performs a register PRESET (all outputs HIGH).

Applying a LOW to the INIT input causes an immediate load of the programmed initialize word into the master and slave flip-flops of the register, independent of all other inputs, including the clock (CP). The initialize data will appear at the device outputs after the outputs are enabled by bringing the asynchronous enable (E) LOW.

#### **Switching Waveforms**

#### Notes on Testing

Incoming test procedures on these devices should be carefully planned, taking into account the high performance and output drive capabilities of the parts. The following notes may be useful.

- Ensure that adequate decoupling capacitance is employed across the device V<sub>C</sub> and ground terminals. Multiple capacitors are recommended, including a 0.1 μF or larger capacitor and a 0.01 μF or smaller capacitor placed as close to the device terminals as possible. Inadequate decoupling may result in large variations of power supply voltage, creating erroneous function or transient performance failures.

- 2. Do not leave any inputs disconnected (floating) during any tests.

- 3. Do not attempt to perform threshold tests under AC conditions. Large amplitude, fast ground current transients normally occur as the device outputs discharge the load capacitances. These transients flowing through the parasitic inductance between the device ground pin and the test system ground can create significant reductions in observable input noise immunity.

- 4. Output levels are measured at 1.5V reference levels.

- Transition is measured at steady state HIGH level -- 500 mV or steady state LOW level +- 500 mV on the output from the 1.5V level on inputs with load shown in Figure 1b.

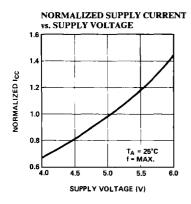

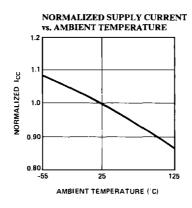

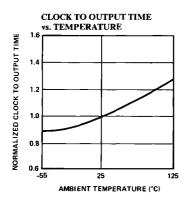

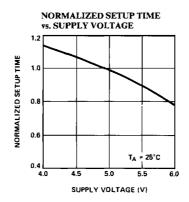

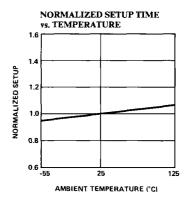

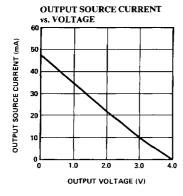

## Typical DC and AC Characteristics

#### **Erasure Characteristics**

Wavelengths of light less than 4000 Angstroms begin to erase the 7C245. For this reason, an opaque label should be placed over the window if the PROM is exposed to sunlight or fluorescent lighting for extended periods of time.

The recommended dose for erasure is ultraviolet light with a wavelength of 2537 Angstroms for a minimum dose (UV intensity  $\times$  exposure time) of 25 Wsec/cm². For an ultraviolet lamp with a 12 mW/cm² power rating the exposure time would be approximately 30–35 minutes. The 7C245 needs to be within 1 inch of the lamp during erasure. Permanent damage may result if the PROM is exposed to high intensity UV light for an extended period of time. 7258 Wsec/cm² is the recommended maximum dosage.

## **Device Programming**

#### **OVERVIEW:**

There are three independent programmable functions contained in the 7C245 CMOS 2K x 8 Registered PROM; the 2K x 8 array, the initial byte, and the synchronous enable bit. All of the programming elements are "EPROM" cells, and are in an erased state when the device is shipped. This erased state manifests itself differently in each case. The erased state for ENABLE bit is the "ASYNCHRONOUS ENABLE" mode. The erased state for the "INITIAL BYTE" is all "0's" or "LOW". The "INITIAL BYTE" may be accessed operationally thru the use of the initialize function. The 2K x 8 array uses a differential memory cell, with differential sensing techniques. In the erased state the cell contains neither a one nor a zero. The erased state of this array may be verified by using the "BLANK CHECK ONES" and "BLANK CHECK ZEROS" function, see Table 3.

## **DC** Programming Parameters $T_A = 25^{\circ}C$

#### Table 1

| Parameter           | Description                | Min. | Max. | Units |

|---------------------|----------------------------|------|------|-------|

| V <sub>PP</sub> [1] | Programming Voltage        | 12.0 | 13.0 | v     |

| V <sub>CCP</sub>    | Supply Voltage             | 4.75 | 5.25 | v     |

| V <sub>IHP</sub>    | Input High Voltage         | 3.0  |      | v     |

| V <sub>ILP</sub>    | Input Low Voltage          |      | 0.4  | v     |

| V <sub>OH</sub> [2] | Output High Voltage        | 2.4  |      | v     |

| V <sub>OL</sub> [2] | Output Low Voltage         |      | 0.4  | v     |

| Грр                 | Programming Supply Current |      | 50   | mA    |

#### AC Programming Parameters $T_A = 25^{\circ}C$

#### Table 2

| TUNIC M                             |                         |      |        |       |  |  |  |  |

|-------------------------------------|-------------------------|------|--------|-------|--|--|--|--|

| Parameter                           | Description             | Min. | Max.   | Units |  |  |  |  |

| tpp                                 | Programming Pulse Width | 100  | 10,000 | μs    |  |  |  |  |

| t <sub>AS</sub>                     | Address Setup Time      | 1.0  |        | μs    |  |  |  |  |

| t <sub>DS</sub>                     | Data Setup Time         | 1.0  |        | μs    |  |  |  |  |

| t <sub>AH</sub>                     | Address Hold Time       | 1.0  |        | μs    |  |  |  |  |

| t <sub>DH</sub>                     | Data Hold Time          | 1.0  |        | μs    |  |  |  |  |

| t <sub>R</sub> , t <sub>F</sub> [3] | Vpp Rise and Fall Time  | 1.0  |        | μs    |  |  |  |  |

| t <sub>VD</sub>                     | Delay to Verify         | 1.0  |        | µs    |  |  |  |  |

| tvp                                 | VP Verify Pulse Width   |      |        | μs    |  |  |  |  |

| t <sub>DV</sub>                     | Verify Data Valid       |      | 1.0    | μs    |  |  |  |  |

| t <sub>DZ</sub>                     | Verify HIGH to High Z   |      | 1.0    | μs    |  |  |  |  |

#### Notes:

- 1. V<sub>CCP</sub> must be applied prior to V<sub>PP</sub>.

- 2. During verify operation.

- 3. Measured 10% and 90% points.

### **Mode Selection**

Table 3

|            |                             |                  |                  | Pin Function                                               |                  |                 |               |

|------------|-----------------------------|------------------|------------------|------------------------------------------------------------|------------------|-----------------|---------------|

| Mode       | Read or Output Disable      | A <sub>2</sub>   | CP               | $\overline{\mathbf{E}}/\overline{\mathbf{E}}_{\mathbf{S}}$ | ĪNIT             | A <sub>1</sub>  | Outputs       |

| Wiode      | Other                       | A <sub>2</sub>   | PGM              | VFY                                                        | V <sub>PP</sub>  | A <sub>1</sub>  | (9-11, 13-17) |

|            | Pin                         | (6)              | (18)             | (19)                                                       | 20               | (7)             |               |

| Read[2,3]  |                             | X                | X                | $v_{IL}$                                                   | V <sub>IH</sub>  | X               | Data Out      |

| Output D   | isable <sup>[5]</sup>       | X                | X                | V <sub>IH</sub>                                            | $v_{IH}$         | X               | High Z        |

| Program[   | 1,4]                        | X                | V <sub>ILP</sub> | V <sub>IHP</sub>                                           | V <sub>PP</sub>  | X               | Data In       |

| Program '  | Verify <sup>[1,4]</sup>     | X                | $v_{IHP}$        | V <sub>ILP</sub>                                           | V <sub>PP</sub>  | X               | Data Out      |

| Program    | Inhibit <sup>[1,4]</sup>    | X                | V <sub>IHP</sub> | V <sub>IHP</sub>                                           | V <sub>PP</sub>  | X               | High Z        |

| Intelligen | t Program <sup>[1,4]</sup>  | X                | V <sub>ILP</sub> | VIHP                                                       | Vpp              | X               | Data In       |

| Program S  | Synch Enable <sup>[4]</sup> | V <sub>IHP</sub> | V <sub>ILP</sub> | V <sub>IHP</sub>                                           | V <sub>PP</sub>  | V <sub>PP</sub> | High Z        |

| Program    | Initial Byte <sup>[4]</sup> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>IHP</sub>                                           | V <sub>PP</sub>  | V <sub>PP</sub> | Data In       |

| Blank Che  | eck Ones[1,4]               | X                | V <sub>PP</sub>  | V <sub>ILP</sub>                                           | V <sub>ILP</sub> | Х               | Ones          |

| Blank Che  | eck Zeros[1,4]              | X                | V <sub>PP</sub>  | V <sub>(HP</sub>                                           | V <sub>ILP</sub> | X               | Zeros         |

#### Notes:

- 1. X = Don't care but not to exceed  $V_{PP}$ .

- During read operation, the output latches are loaded on a "0" to "1" transition of CP.

- If the registered device is being operated in a synchronous mode, pin 19 must be LOW prior to the "0" to "1" transition on CP (18) that loads the register.

Figure 3. Programming Pinouts

During programming and verification, all unspecified pins to be at V<sub>ILP</sub>.

5. If the registered device is being operated in a synchronous mode, pin 19 must be HIGH prior to the "0" to "1" transition on CP (18) that loads the register.

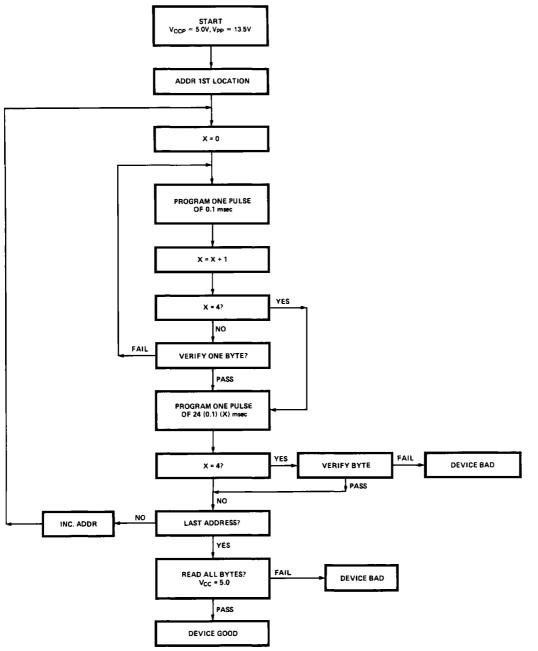

The CY7C245 programming algorithm allows significantly faster programming than the "worst case" specification of 10 msec.

Typical programming time for a byte is less than 2.5 msec. The use of EPROM cells allows factory testing of programmed cells, measurement of data retention and erasure to ensure reliable data retention and functional performance. A flowchart of the algorithm is shown in Figure 4.

The algorithm utilizes two different pulse types: initial and overprogram. The duration of the  $\overline{PGM}$  pulse (tpp) is 0.1 msec which will then be followed by a longer overprogram pulse of 24 (0.1) (X) msec. X is an iteration counter and is equal to the NUMBER of the initial 0.1 msec pulses applied before verification occurs. Up to four 0.1 msec pulses are provided before the overprogram pulse is applied.

The entire sequence of program pulses and byte verifications is performed at  $V_{CCP} = 5.0V$ . When all bytes have been programmed all bytes should be compared (Read mode) to original data with  $V_{CC} = 5.0V$ .

## Bit Map Data

| Programmer | Address | RAM Data     |

|------------|---------|--------------|

| Decimal    | Hex     | Contents     |

| 0          | 0       | DATA         |

| •          | •       | •            |

| •          | •       | •            |

| •          | •       | •            |

| 2047       | 7FF     | DATA         |

| 2048       | 800     | INIT BYTE    |

| 2049       | 801     | CONTROL BYTE |

#### Control Byte

- 00 Asynchronous output enable (default state)

- 01 Synchronous output enable

0016-8

Figure 4. Programming Flowchart

0016-9

## Programming Sequence 2K x 8 Array

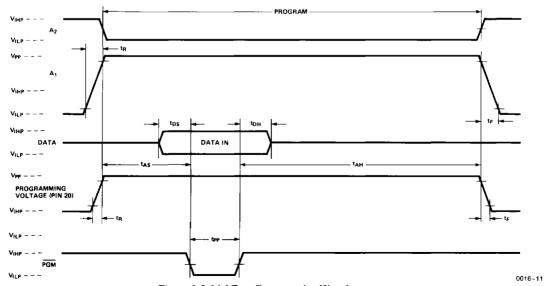

Power the device for normal read mode operation with pin 18, 19 and 20 at V<sub>IH</sub>. Per Figure 5 take pin 20 to V<sub>PP</sub>. The device is now in the program inhibit mode of operation with the output lines in a high impedance state; see Figures 5 and 6. Again per Figure 5 address program and verify one byte of data. Repeat this for each location to be programmed.

If the brute force programming method is used, the pulse width of the program pulse should be 10 ms, and each

location is programmed with a single pulse. Any location that fails to verify causes the device to be rejected.

If the intelligent programming technique is used, the program pulse width should be  $100~\mu s$ . Each location is ultimately programmed and verified until it verifies correctly up to and including 4 times. When the location verifies, one additional programming pulse should be applied of duration 24X the sum of the previous programming pulses before advancing to the next address to repeat the process.

Figure 5. PROM Programming Waveforms

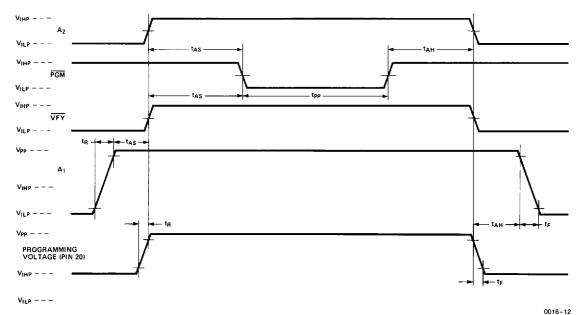

Figure 6. Initial Byte Programming Waveforms

### **Programming the Initialization Byte**

The CY7C245 registered PROM has a 2049th byte of data used to initialize the value of the register. This initial byte is value "O" when the part is received. If the user desires to have a value other than "O" for register initialization, this must be programmed into the 2049th byte. This byte is programmed in a similar manner to the 2048 normal bytes in the array except for two considerations. First, since all of the normal addresses of the part are used up, a super voltage will be used to create additional effective addresses. The actual address has Vpp on A<sub>1</sub> pin 7, and V<sub>ILP</sub> on A<sub>2</sub>, pin 6, per Table 3. The programming and verification of "INITIAL BYTE" is accomplished operationally by performing an initialize function.

### **Programming Synchronous Enable**

The CY7C245 provides for both a synchronous and asynchronous enable function. The device is delivered in an asynchronous mode of operation and only requires that the user alter the device if synchronous operation is required. The determination of the option is accomplished thru the use of an EPROM cell which is programmed only if synchronous operation is required. As with the INITIAL byte, this function is addressed thru the use of a supervoltage. Per Table 3, VPP is applied to pin 7 (A<sub>1</sub>) with pin 6 (A<sub>2</sub>) at V<sub>IHP</sub>. This addresses the cell that programs synchronous enable. Programming the cell is accomplished with a 10 ms program pulse on pin 18 (PGM) but does not require any data as there is no choice as to how synchronous enable may be programmed, only if it is to be programmed.

Figure 7. Program Synchronous Enable

# Verification of Synchronous Enable

Verification of the synchronous enable function is accomplished operationally. Power the device for read operation with pin 20 at  $V_{IH}$ , cause clock pin 18 to transition from  $V_{IL}$  to  $V_{IH}$ . The output should be in a High Z state. Take pin 20, ENABLE, to  $V_{IL}$ . The outputs should remain in a high Z state. Transition the clock from  $V_{IL}$  to  $V_{IH}$ , the outputs should now contain the data that is present. Again set pin 19 to  $V_{IH}$ . The output should remain driven. Clocking pin 18 once more from  $V_{IL}$  to  $V_{IH}$  should place the outputs again in a High Z state.

#### Blank Check

A virgin device contains neither one's nor zero's because of the differential cell used for high speed. To verify that a PROM is unprogrammed, use the two blank check modes provided in Table 3. In both of these modes, address and read locations 0 thru 2047. A device is considered virgin if all locations are respectively "1's" and "0's" when addressed in the "BLANK ONES AND ZEROS" modes.

Because a virgin device contains neither ones nor zeros, it is necessary to program both one's and zero's. It is recommended that all locations be programmed to ensure that ambiguous states do not exist.

# **Ordering Information**

| Speed | l (ns) | I <sub>CC</sub> | Ordering      | Package     | Operating  |

|-------|--------|-----------------|---------------|-------------|------------|

| tsa   | tco    | mA              | Code          | Type        | Range      |

| 25    | 12     | 90              | CY7C245-25PC  | P13         | Commercial |

|       |        |                 | CY7C245-25WC  | <b>W</b> 14 |            |

| 35    | 15     | 60              | CY7C245L-35PC | P13         | Commercial |

|       |        |                 | CY7C245L-35WC | W14         |            |

|       |        | 90              | CY7C245-35PC  | P13         |            |

|       |        |                 | CY7C245-35SC  | S13         |            |

|       |        |                 | CY7C245-35WC  | W14         |            |

|       |        |                 | CY7C245-35LC  | L64         |            |

|       |        | 120             | CY7C245-35DMB | D14         | Military   |

|       |        |                 | CY7C245-35QMB | Q64         |            |

|       |        |                 | CY7C245-35WMB | W14         |            |

|       |        |                 | CY7C245-35LMB | L64         |            |

| Speed | l (ns) | I <sub>CC</sub> | Ordering      | Package | Operating  |

|-------|--------|-----------------|---------------|---------|------------|

| tSA   | tco    | mA              | Code          | Туре    | Range      |

| 45    | 25     | 60              | CY7C245L-45PC | P13     | Commercial |

|       |        |                 | CY7C245L-45WC | W14     |            |

|       |        | 90              | CY7C245-45PC  | P13     |            |

|       |        |                 | CY7C245-45SC  | S13     |            |

|       |        |                 | CY7C245-45WC  | W14     |            |

|       |        |                 | CY7C245-45LC  | L64     |            |

|       |        | 120             | CY7C245-45WMB | W14     | Military   |

|       |        |                 | CY7C245-45LMB | L64     |            |

|       |        |                 | CY7C245-45DMB | D14     |            |

|       |        |                 | CY7C245-45QMB | Q64     |            |

# MILITARY SPECIFICATIONS Group A Subgroup Testing

# DC Characteristics

| Parameters      | Subgroups |

|-----------------|-----------|

| V <sub>OH</sub> | 1,2,3     |

| $v_{OL}$        | 1,2,3     |

| $V_{IH}$        | 1,2,3     |

| $V_{IL}$        | 1,2,3     |

| $I_{IX}$        | 1,2,3     |

| I <sub>OZ</sub> | 1,2,3     |

| I <sub>CC</sub> | 1,2,3     |

# **Switching Characteristics**

| Parameters | Subgroups   |

|------------|-------------|

| tsA        | 7,8,9,10,11 |

| tHA        | 7,8,9,10,11 |

| tco        | 7,8,9,10,11 |

Document #: 38-00004-D