# MPEG Audio Decoder System

#### Features

- DSP Optimized for Audio Decode, 24-bit Fixed Point w/48-bit Accumulator

- On-Chip Functional Blocks Include:

- DSP with RAM and ROM Memories

- CD Quality Stereo DAC with Output Filtering

- Mono Output & Digital Volume Control

- S/PDIF Transmitter, Bidirectional PCM Audio Port

- Programmable Phase Locked Loop for Clocking

- Dedicated Compressed Serial Input Interface

- MPEG-1 & MPEG-2 Layers 1 & 2 With All Sample/Bit Rates and Ancilliary Data Support.

- MPEG-1 & MPEG-2 Packetized Audio Stream and Elementary Stream Input

- PCM Synthesis for Auxiliary Audio

- Pin Compatibility with CS4920A and Primary Feature/Firmware Compatible

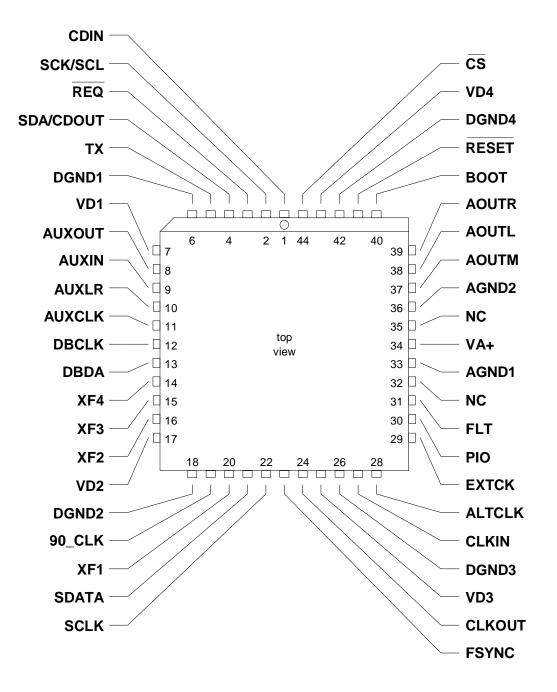

- +5 Volt Only CMOS, 44 pin PLCC

#### Description

The CS4922 is a complete audio decompression subsystem implemented in a single high integration mixed signal CMOS chip. The CS4922 is a performance enhanced and cost reduced version of the CS4920A audio decoder IC product. The CS4920A has been widely used in direct broadcast system set-top boxes as well as other media terminals including PC adapter cards.

The CS4922 is tailored for MPEG-2 audio decompression to include the necessary hardware and firmware to ensure proper audio/video synchronization. In addition to audio decoding this programmable DSP solution provides robust error concealment and feature implementations like ancilliary data support and PCM synthesis. The CS4922 enhancements include additional MIPS, a bi-directional I<sup>2</sup>S port and more general purpose output pins.

The CS4922 will supersede the CS4920A as the most popular MPEG audio decoder on the market and the only complete MPEG audio subsystem IC in the world.

#### ORDERING INFORMATION

CS4922-CL CDB4922 44-pin PLCC Evaluation Board

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

## **Table Of Contents**

| 1. | THEORY OF OPERATION                                        | . 13 |

|----|------------------------------------------------------------|------|

|    | 1.1 Introduction                                           | . 13 |

| 2. | PERIPHERALS                                                | . 14 |

|    | 2.1 Clock Manager                                          | . 14 |

|    | 2.2 33-bit Counter                                         | 16   |

|    | 2.3 Digital to Analog Converter                            | . 16 |

|    | 2.4 Digital Audio Transmitter                              | . 17 |

|    | 2.5 Audio Serial Input Port                                | . 18 |

|    | 2.6 Auxiliary Digital Audio Port                           |      |

|    | 2.7 Serial Control Port                                    | . 19 |

|    | 2.8 User Definable Pins                                    | . 25 |

|    | BOOT PROCEDURE                                             |      |

| 4. | COMMON CS4922 INTERFACE ROUTINES                           |      |

|    | 4.1 Boot Procedure Routine                                 |      |

|    | 4.2 Writing a Byte(s) to the Host Port                     |      |

|    | 4.3 Reading a Byte(s) from the Host Port                   |      |

| 5. | REGISTER DESCRIPTIONS                                      |      |

|    | 5.1 Digital to Analog Converter Output Register            |      |

|    | 5.2 Audio Serial Input Register, Typically Compressed Data |      |

|    | 5.3 Audio Serial Input Control Register                    |      |

|    | 5.4 Serial Control Port Data I/O Register                  |      |

|    | 5.5 Serial Control Port Control Register                   |      |

|    | 5.6 Clock Manager Control Register Zero                    |      |

|    | 5.7 Clock Manager Control Register One                     |      |

|    | 5.8 Digital Audio Transmitter Data Register                |      |

|    | 5.9 Digital Audio Transmitter Channel Status Register      |      |

|    | 5.10 Digital Audio Transmitter Control Register            |      |

|    | 5.11 Long Interrupt Register                               |      |

|    | 5.12 Debugger Data I/O Register                            |      |

|    | 5.13 Debugger Data Status Register                         |      |

|    | 5.14 Playback Timing Clock MSB                             |      |

|    | 5.15 Playback Timing Clock LSB                             |      |

|    | 5.16 DSP Status Register                                   |      |

|    | 5.17 DSP Shadow Status Register                            |      |

|    | 5.18 Auxiliary Audio Port Data Register                    |      |

|    | 5.19 Auxiliary Audio Port Control Register                 |      |

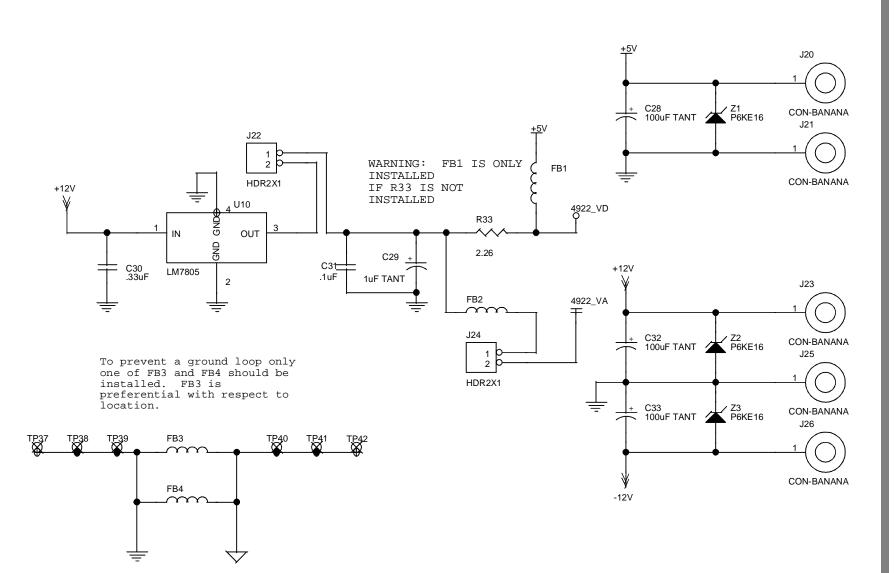

|    | POWER SUPPLY AND GROUNDING                                 |      |

|    | DAC FILTER RESPONSE PLOTS                                  |      |

|    | PIN DESCRIPTIONS                                           |      |

|    | PARAMETER DEFINITIONS                                      |      |

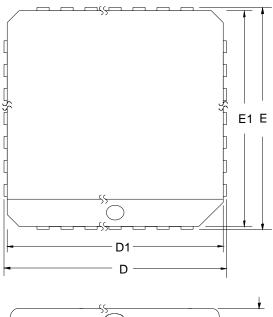

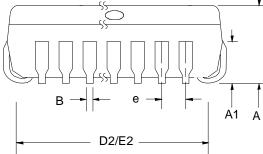

| 10 | PACKAGE DIMENSIONS                                         | 57   |

**ANALOG CHARACTERISTICS** ( $T_A = 25 \text{ °C}$ ; VA+, VD+ = 5V; CLKIN = 27 MHz; Full-Scale Output Sinewave, 1.125 kHz; Word Clock = 48 kHz (PLL in use); Logic 0 = GND, Logic 1 = VD+; Measurement Bandwidth is 20 Hz to 20 kHz; Local components as shown in "Typical Connection Diagram"; SPI mode, I<sup>2</sup>S audio data; unless otherwise specified.)

| Parame                                                     | Parameter*                     |     | Min         | Тур          | Max           | Units    |

|------------------------------------------------------------|--------------------------------|-----|-------------|--------------|---------------|----------|

| Dynamic Performance                                        |                                |     |             | •            |               | •        |

| DAC Resolution                                             |                                |     | 16          | -            | -             | Bits     |

| DAC Differential Nonlinearity                              |                                | DNL | -           | -            | ±0.9          | LSB      |

| Total Harmonic Distortion                                  | AOUTL, AOUTR (Note 1)<br>AOUTM | THD | -           | 0.01<br>0.02 | 0.015<br>0.03 | %        |

| Instantaneous Dynamic Range<br>(DAC not muted, A weighted) | AOUTL, AOUTR (Note 1)<br>AOUTM | IDR | 85<br>80    | 90<br>85     | -             | dB       |

| Interchannel Isolation                                     | (Note 1)                       |     | -           | 85           | -             | dB       |

| Interchannel Gain Mismatch                                 |                                |     | -           | -            | 0.2           | dB       |

| Frequency Response                                         |                                |     | -3.0        | -            | +0.2          | dB       |

| Full Scale output Voltage                                  | AOUTL, AOUTR (Note 1)<br>AOUTM |     | 2.66<br>2.7 | 2.88<br>3.0  | 3.2<br>3.3    | Vpp      |

| Gain Drift                                                 |                                |     | -           | 100          | -             | ppm/°C   |

| Deviation from Linear Phase                                |                                |     | -           | -            | 5             | Deg      |

| Out of Band Energy                                         | (Fs/2 to 2Fs)                  |     | -           | -60          | -             | dB       |

| Analog Output Load                                         | Resistance:<br>Capacitance:    |     | 8<br>-      | -            | -<br>100      | kΩ<br>pF |

| Power Supply                                               |                                |     |             |              |               |          |

| Power Supply Rejection                                     | (1 kHz)                        |     | -           | 40           | -             | dB       |

| Power Supply Consumption                                   | VA+<br>VD+                     |     | -<br>-<br>- | 20<br>100    | 40<br>140     | mA<br>mA |

Note: 1. 10 k $\Omega$ , 100pF load for each analog signal (Left, Right). 30 k $\Omega$ , 100pF load for analog Mono signal.

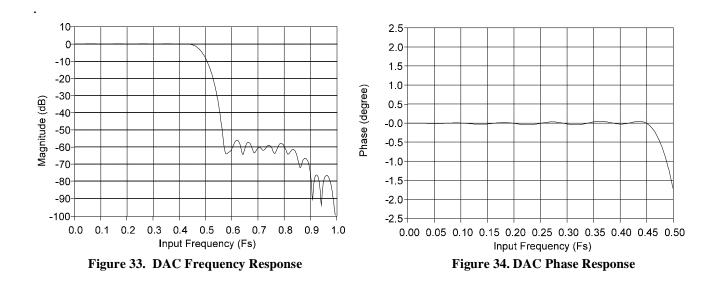

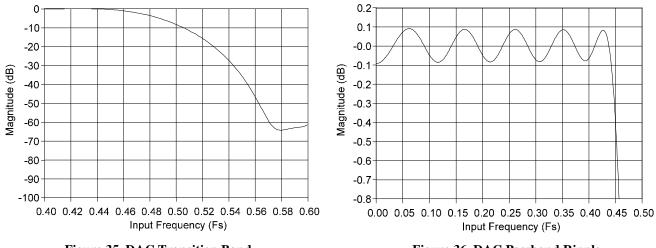

## **D/A INTERPOLATION FILTER CHARACTERISTICS**

(See graphs toward the end of this data sheet)

| Parameter                                          | Symbol | Min      | Тур   | Max     | Units |

|----------------------------------------------------|--------|----------|-------|---------|-------|

| Passband (to -3 dB corner)(Fs is conversion freq.) |        | 0        | -     | 0.476Fs | Hz    |

| Passband Ripple                                    |        | -        | -     | ±0.1    | dB    |

| Transition Band                                    |        | 0.442Fs  | -     | 0.567Fs | Hz    |

| Stop Band                                          |        | ≥0.567Fs | -     | -       | Hz    |

| Stop Band Rejection                                |        | 50       | -     | -       | dB    |

| Stop Band Rejection with Ext. 2Fs RC filter        |        | 57       | -     | -       | dB    |

| Group Delay                                        |        | -        | 12/Fs | -       | S     |

\* Refer to Parameter Definitions at the end of this data sheet.

Specifications are subject to change without notice.

## **ABSOLUTE MAXIMUM RATINGS**

(AGND, DGND = 0V, all voltages with respect to ground.)

| Paramet                               | Symbol           | Min               | Мах  | Units       |    |

|---------------------------------------|------------------|-------------------|------|-------------|----|

| DC Power Supplies:                    | Positive Digital | VD+               | -0.3 | 6.0         | V  |

|                                       | Positive Analog  | VA+               | -0.3 | 6.0         | V  |

|                                       | VA+   -   VD+    |                   | -    | 0.4         | V  |

| Input Current, Any Pin Except Supplie | S                | l <sub>in</sub>   | -    | ±10         | mA |

| Digital Input Voltage                 |                  | V <sub>IND</sub>  | -0.3 | (VD+) + 0.4 | V  |

| Ambient Operating Temperature (pow    | er applied)      | T <sub>Amax</sub> | -55  | 125         | °C |

| Storage Temperature                   |                  | T <sub>stg</sub>  | -65  | 150         | °C |

WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

## **RECOMMENDED OPERATING CONDITIONS**

(AGND, DGND = 0V; all voltages with respect to ground.)

| Parameter                     |                  | Symbol         | Min  | Тур | Max  | Units |

|-------------------------------|------------------|----------------|------|-----|------|-------|

| DC Power Supplies:            | Positive Digital | VD+            | 4.50 | 5.0 | 5.50 | V     |

|                               | Positive Analog  | VA+            | 4.50 | 5.0 | 5.50 | V     |

|                               | VA+   -   VD+    |                | -    | -   | 0.4  | V     |

| Ambient Operating Temperature |                  | T <sub>A</sub> | 0    | -   | 70   | °C    |

## DIGITAL CHARACTERISTICS

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V $\pm$ 10%; measurements performed under static conditions.)

| Parameter                                             | Symbol          | Min      | Тур  | Max      | Units |

|-------------------------------------------------------|-----------------|----------|------|----------|-------|

| High-Level Input Voltage                              | V <sub>IH</sub> | TBD      | 2.25 | -        | V     |

| Low-Level Input Voltage                               | V <sub>IL</sub> | -        | -    | 0.8      | V     |

| High-Level Output Voltage at I <sub>o</sub> = -2.0 mA | V <sub>OH</sub> | VD x 0.9 | -    | -        | V     |

| Low-Level Output Voltage at I <sub>o</sub> = 2.0 mA   | V <sub>OL</sub> | -        | -    | VD x 0.1 | V     |

| Input Leakage Current (Note 2)                        | I <sub>in</sub> | -        | -    | 1.0      | μA    |

Note: 2. Not Valid for pin numbers 9, 12, 13, and 30 which are configured with on-chip pull-down resistors. Not valid for pin number 29 which is a static input signal and should be tied to either VD+ or DGND.

## **SWITCHING CHARACTERISTICS - CLOCKS**

$(T_A = 25 \text{ °C}; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C_L = 20pF)$

| Parameter                      | Symbol | Min   | Тур   | Max    | Units |

|--------------------------------|--------|-------|-------|--------|-------|

| Master Clock Frequency         | CLKIN  | 0.256 | 27    | 30     | MHz   |

| Master Clock Duty Cycle        | CYCK   | 40    | 50    | 60     | %     |

| Alternate Clock P = 0 (Note 3) | ALTCLK | -     | 512Fs | -      | Hz    |

| P = 1                          |        | -     | 768Fs | -      | Hz    |

| Clock Output                   | CLKOUT | -     | -     | 256 Fs | MHz   |

Note: 3. ALTCLK is required to run at 512 or 768 times the sample frequency.

### **SWITCHING CHARACTERISTICS - EXTERNAL FLAGS**

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C<sub>L</sub> = 20pF)

| Parameter            |          | Symbol           | Min | Тур | Max | Units |

|----------------------|----------|------------------|-----|-----|-----|-------|

| Rise time of XF1-XF4 | (Note 4) | t <sub>rxf</sub> |     |     | 200 | ns    |

| Fall time of XF1-XF4 |          | t <sub>fxf</sub> |     |     | 100 | ns    |

Note: 4. Assumes  $2k\Omega$  pull-up to 5V supply on XF1-XF4 pins.

## **SWITCHING CHARACTERISTICS - PROGRAMMABLE INPUT/OUTPUT**

$(T_A = 25 \text{ °C}; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C_L = 20pF)$

| Paramet          | er       | Symbol            | Min | Тур | Max | Units |

|------------------|----------|-------------------|-----|-----|-----|-------|

| I_O = 0          | (Note 5) | L                 |     |     |     | I.    |

| Input Frequency  |          | f <sub>pio</sub>  |     |     | 350 | kHz   |

| Risetime of PIO  |          | t <sub>rpio</sub> |     |     | 200 | ns    |

| Fall time of PIO |          | t <sub>fpio</sub> |     |     | 200 | ns    |

| I_O = 1          | (Note 5) |                   |     |     |     |       |

| Rise time of PIO |          | t <sub>rpo</sub>  |     |     | 200 | ns    |

| Fall time of PIO |          | t <sub>fpo</sub>  |     |     | 200 | ns    |

Note: 5. I\_O is a bit in the LINT register.

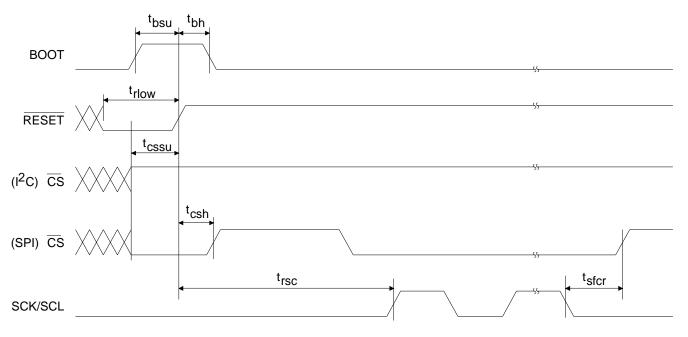

#### SWITCHING CHARACTERISTICS - BOOT INITIALIZATION ( $T_A = 25 \degree C$ ; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C<sub>L</sub> = 20pF)

|                                                                    |          | -                 |     | • • |       |

|--------------------------------------------------------------------|----------|-------------------|-----|-----|-------|

| Parameter                                                          |          | Symbol            | Min | Max | Units |

| BOOT Setup Time to RESET Rising                                    |          | t <sub>bsu</sub>  | 350 | -   | ns    |

| RESET Rising to Boot Hold Time                                     |          | t <sub>bh</sub>   | 450 | -   | ns    |

| CS Setup Time to RESET Rising                                      | (Note 6) | t <sub>cssu</sub> | 200 | -   | ns    |

| RESET Rising to CS Hold Time                                       |          | t <sub>csh</sub>  | 400 | -   | ns    |

| RESET Low Time                                                     |          | t <sub>rlow</sub> | 50  | -   | μs    |

| SCK/SCL Delay Time from RESET Rising                               | (Note 7) | t <sub>rsc</sub>  | 2   | -   | ms    |

| SCK/SCL falling to $\overline{CS}$ rising on last byte of download |          | t <sub>sfcr</sub> | 3   | -   | μs    |

Note: 6. The mode of the Serial Control Port is selected by  $\overline{CS}$ .  $\overline{CS} = 1$  is  $I^2 C^{(R)}$ .  $\overline{CS} = 0$  is SPI mode.

This delay is necessary after any rising edge of RESET to allow time for the part to initialize and for the on-board PLL to stablize.

**Boot Timing**

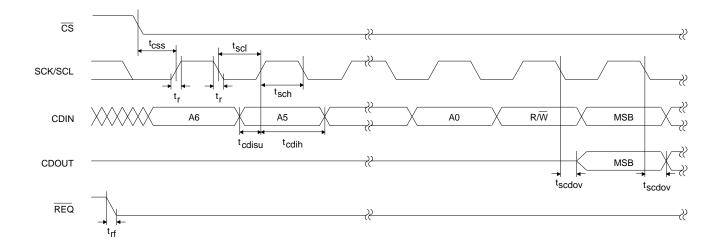

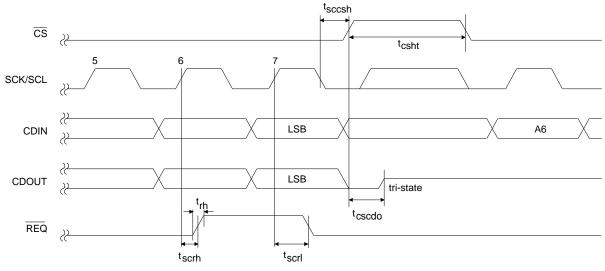

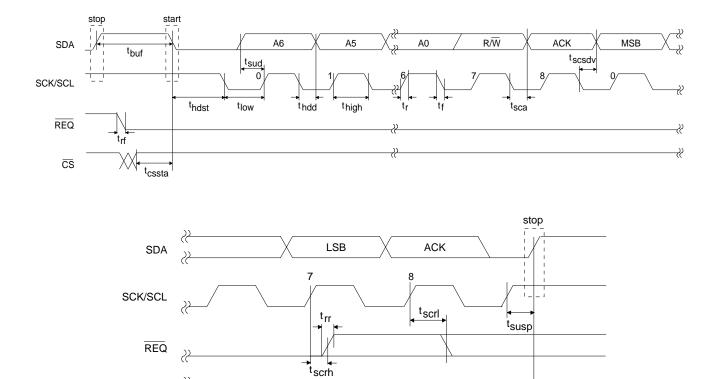

## **SWITCHING CHARACTERISTICS - CONTROL PORT**

$(T_A = 25 \text{ °C}; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C_L = 20pF)$

| Parameter                                           |             |                | Symbol                               | Min         | Max         | Units    |

|-----------------------------------------------------|-------------|----------------|--------------------------------------|-------------|-------------|----------|

| SPI Mode (CS = 0)                                   |             |                |                                      | •           | •           | •        |

| SCK/SCL Clock Frequency<br>mode)                    |             | (slow<br>(fast | f <sub>sck</sub><br>f <sub>sck</sub> | -           | 350<br>2000 | kHz      |

|                                                     |             |                | +                                    | 20          | -           |          |

| CS Falling to SCK/SCL Rising                        | (slow mode) |                | t <sub>css</sub>                     |             |             | ns       |

| Rise Time of Both CDIN and SCK/SCL Lines            | (slow mode) |                | t <sub>r</sub>                       | -           | 50          | ns       |

| Fall Time of Both CDIN and SCK/SCL Lines mode)      | (slow mode) | (fast          | t <sub>f</sub><br>t <sub>f</sub>     | -           | 300<br>50   | ns<br>ns |

| SCK/SCL Low Time<br>mode)<br>mode)                  |             | (slow<br>(fast | t <sub>scl</sub><br>t <sub>scl</sub> | 1100<br>150 | -           | ns<br>ns |

| SCK/SCL High Time<br>mode)<br>mode)                 |             | (slow<br>(fast | t <sub>sch</sub><br>t <sub>sch</sub> | 1100<br>150 | -           | ns<br>ns |

| Setup Time CDIN to SCK/SCL Rising                   | (slow mode) | (fast          | t <sub>cdisu</sub>                   | 250<br>50   | -           | ns<br>ns |

| Hold Time SCK/SCL Rising to CDIN                    | (Note 8)    |                | t <sub>cdih</sub>                    | 50          | -           | ns       |

| Transition Time from SCK/SCL to CDOUT Valid         | (Note 9)    |                | t <sub>scdov</sub>                   | -           | 40          | ns       |

| Time from SCK/SCL Rising to REQ Rising              | (Note 9)    |                | t <sub>scrh</sub>                    | -           | 200         | ns       |

| Rise Time for REQ<br>(Note 10)                      |             |                | t <sub>rr</sub>                      | -           | 50          | ns       |

| Fall Time for REQ<br>(Note 11)                      |             |                | t <sub>rf</sub>                      | -           | 20          | ns       |

| Hold Time for REQ from SCK/SCL Rising               | (Note 11)   |                | t <sub>scrl</sub>                    | 0           | -           | ns       |

| Time from SCK/SCL Falling to $\overline{CS}$ Rising |             |                | t <sub>sccsh</sub>                   | 20          | -           | ns       |

| High Time Between Active CS                         |             |                | t <sub>csht</sub>                    | 200         | -           | ns       |

Note: 8. Data must be held for sufficient time to bridge 300(50) ns transition time of SCK/SCL.

9. CDOUT should NOT be sampled during this time period.

REQ will only go HIGH if there is no data in SCPOUT at the rising edge of SCL/SCK during a READ operation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 kΩ. C<sub>L</sub> = 20 pF.

If REQ went HIGH as indicated in note 7, then REQ will hold high at least until the next rising edge of

11. If REQ went HIGH as indicated in note 7, then REQ will hold high at least until the next rising edge of SCK/SCL. If data is in SCPOUT at this time REQ will go active LOW again. This condition should be treated as a new READ process. Address and R/W bit should be sent again.

CS4922

**SPI Control Port Timing**

## **SWITCHING CHARACTERISTICS - CONTROL PORT**

$(T_A = 25 \text{ °C}; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C_L = 20pF)$

| Parameter                                                       |                | Symbol             | Min        | Max        | Units |

|-----------------------------------------------------------------|----------------|--------------------|------------|------------|-------|

| $I^2 C^{\mathbb{R}}$ Mode ( $\overline{CS}=1$ )                 | (Note 1        | 2)                 |            |            | 1     |

| SCK/SCL Clock Frequency<br>mode)                                | (slow<br>(fast | f <sub>scl</sub>   |            | 100<br>400 | kHz   |

| mode)                                                           | × ×            |                    |            |            |       |

| Bus Free Time Between Transmissions                             |                | t <sub>buf</sub>   | 4.7        |            | μs    |

| Start Condition Hold Time (prior to first clock pulse)          |                | t <sub>hdst</sub>  | 4.0        |            | μs    |

| Clock Low Time                                                  | slow<br>fast   | t <sub>low</sub>   | 4.7<br>1.2 |            | μs    |

| Clock High Time                                                 | slow<br>fast   | t <sub>high</sub>  | 4.0<br>1.0 |            | μs    |

| SDA Setup Time to SCK/SCL Rising                                |                | t <sub>sud</sub>   | 250        |            | ns    |

| SDA Hold Time from SCK/SCL Falling                              | (Note 13)      | t <sub>hdd</sub>   | 0          |            | μs    |

| Rise Time of Both SDA and SCK/SCL                               | (Note 14)      | t <sub>r</sub>     |            | 50         | ns    |

| Fall Time of Both SDA and SCK/SCL                               |                | t <sub>f</sub>     |            | 300        | ns    |

| Time from SCK/SCL Falling to CS4920 ACK                         |                | t <sub>sca</sub>   |            | 40         | ns    |

| Time from SCK/SCL Falling to SDA<br>Valid During READ Operation |                | t <sub>scsdv</sub> |            | 40         | ns    |

| Time from SCK/SCL Rising to REQ Rising                          | (Note 15)      | t <sub>scrh</sub>  |            | 200        | ns    |

| Hold Time for REQ from SCK/SCL Rising                           | (Note 16)      | t <sub>scrl</sub>  | 0          |            | ns    |

| Rise Time for REQ<br>15)                                        | (Note          | t <sub>rr</sub>    |            | 50         | ns    |

| Fall Time for REQ<br>16)                                        | (Note          | t <sub>rf</sub>    |            | 20         | ns    |

| Setup Time for Stop Condition                                   |                | t <sub>susp</sub>  | 4.7        |            | μs    |

Note: 12. Use of I<sup>2</sup>C<sup>®</sup> bus compatible interface requires a license from Philips. I<sup>2</sup>C is a registered trademark of Philips Semiconductor.

13. Data must be held for sufficient time to bridge the 300ns transition time of SCK/SCL.

14. This rise time is shorter than the I<sup>2</sup>C specifications recommend, please refer to the section on SCP communications for more information.

REQ will only go HIGH if there is no data in the SCPOUT register at the rising edge of SCL/SCK during a READ operation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 kΩ C<sub>L</sub> = 20pF.

if REQ went HIGH as indicated in Note 15 then REQ will hold HIGH at least until the next rising edge of

16. if REQ went HIGH as indicated in Note 15 then REQ will hold HIGH at least until the next rising edge of SCK/SCL. If data is in the SCPOUT register at this time REQ will go active LOW again. This condition should be treated as a new READ process. The address and R/W should be sent again following a new START condiiton.

$\mathcal{C}$

CS

I<sup>2</sup>C<sup>®</sup> Control Port Timing

t<sub>cssto</sub>

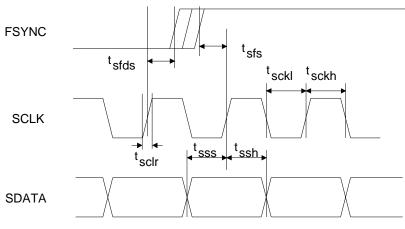

## SWITCHING CHARACTERISTICS - SERIAL AUDIO PORT

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = GND, Logic 1 = VD+; C<sub>L</sub> = 20 pF)

| Parameter                           |          | Symbol            | Min | Тур | Max  | Units |

|-------------------------------------|----------|-------------------|-----|-----|------|-------|

| SCLK Frequency                      |          |                   | -   | -   | 12.5 | MHz   |

| SCLK Pulse Width Low                |          | t <sub>sckl</sub> | 25  | -   | -    | ns    |

| SCLK Pulse Width High               |          | t <sub>sckh</sub> | 25  | -   | -    | ns    |

| SCLK rising to FSYNC edge delay (I  | Note 17) | t <sub>sfds</sub> | 20  | -   | -    | ns    |

| SCLK rising to FSYNC edge setup (I  | Note 17) | t <sub>sfs</sub>  | 20  | -   | -    | ns    |

| SDATA valid to SCLK rising setup (I | Note 17) | t <sub>sss</sub>  | 20  | -   | -    | ns    |

| SCLK rising to SDATA hold time (I   | Note 17) | t <sub>ssh</sub>  | 20  | -   | -    | ns    |

| Rise time of SCLK                   |          | t <sub>sclr</sub> | -   | -   | 20   | ns    |

Note: 17. The table above assumes data is output on the falling edge and latched on the rising edge. The SCLK edge is selectable in setting the EDG bit in the ASICN register. The diagram is for EDG = 1.

Serial Audio Port Timing

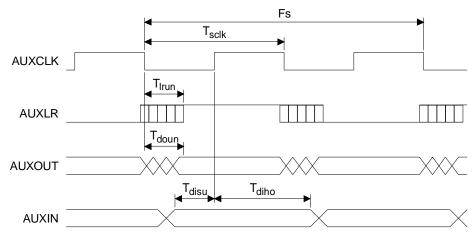

## SWITCHING CHARACTERISTICS - AUXILIARY DIGITAL AUDIO PORT

| Parameter                        |           | Symbol | Min | Тур                               | Max | Units |

|----------------------------------|-----------|--------|-----|-----------------------------------|-----|-------|

| Input Sample Rate                | (Note 18) | Fs     | 16  | -                                 | 48  | kHz   |

| AUXCLK Period                    | (Note 19) | tsclk  | -   | 1/(32Fs)<br>1/(64Fs)<br>1/(128Fs) | -   | ns    |

| AUXCLK to AUXLR valid            |           | tlrun  | 0   | -                                 | 25  | ns    |

| AUXCLK to AUXOUT data valid      |           | tdoun  | 0   | -                                 | 25  |       |

| AUXIN data setup time to AUXCLK  |           | tdisu  | 50  | -                                 | -   | ns    |

| AUXIN data hold time from AUXCLK |           | tdiho  | 3   | -                                 | -   | ns    |

Note: 18. Fs determined by clock input rate and configuration of on-chip pll. 19. AUXCLK frequency selectable @ 32, 64, or 128 Fs via AUXCN register bits 1:0.

**Auxiliary Audio Port Timing**

#### **1. THEORY OF OPERATION**

#### **1.1. Introduction**

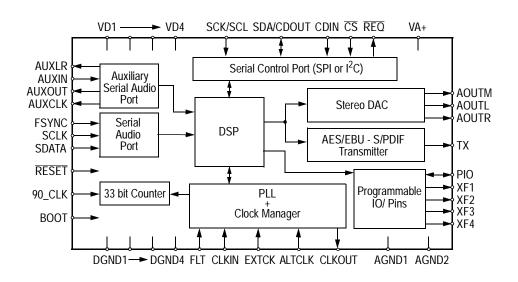

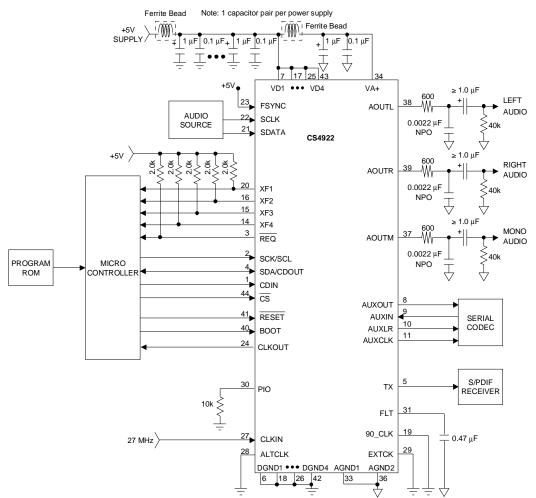

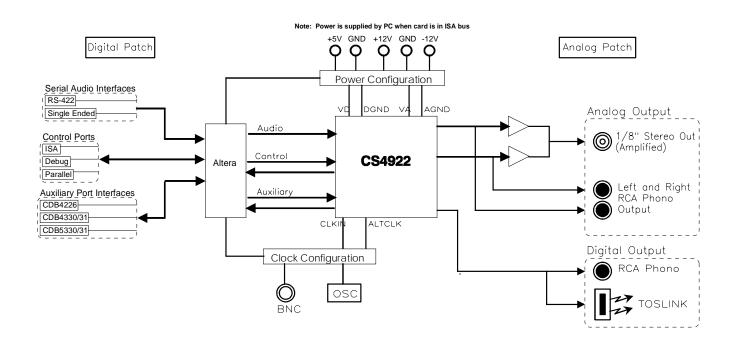

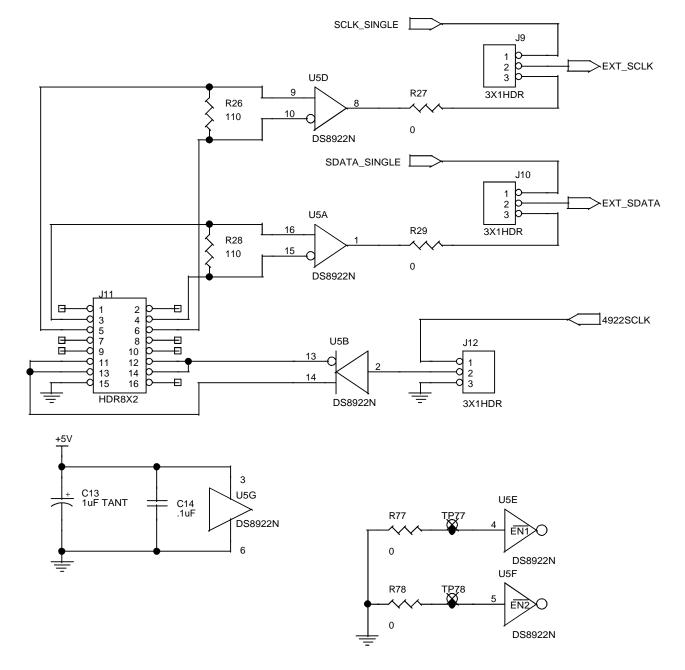

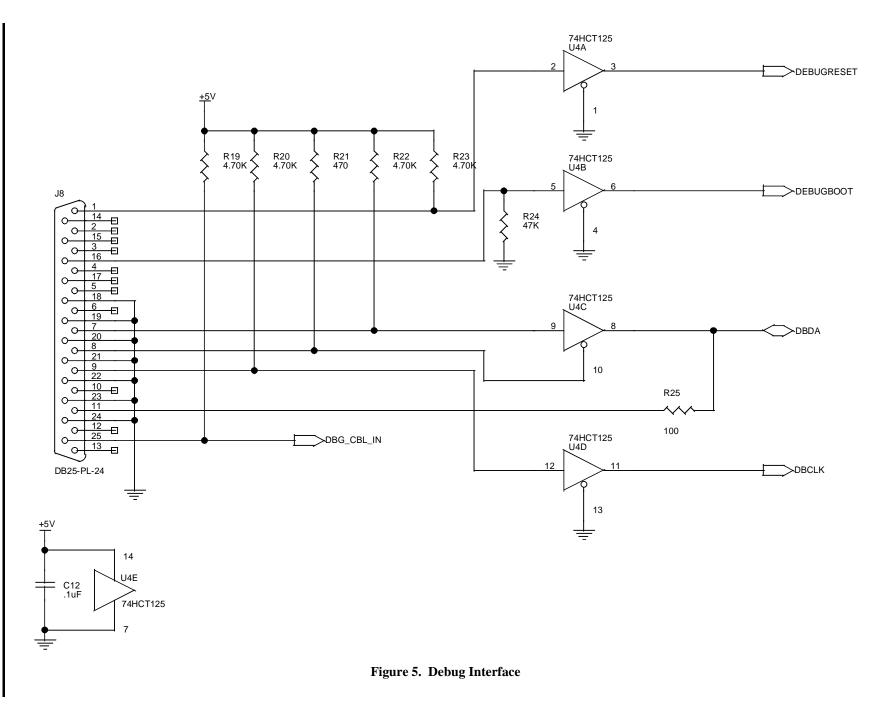

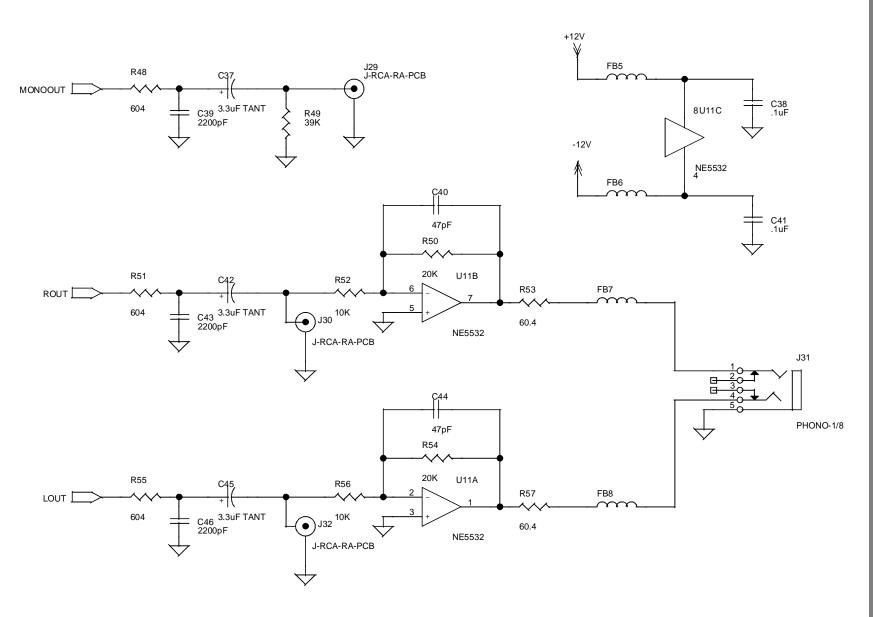

The CS4922 is a complete audio subsystem on a chip. It consists of a general-purpose Digital Signal Processor (DSP), and a number of supplementary analog and digital blocks. These supplementary blocks include a programmable PLL clock multiplier, a serial audio input port, an auxiliary serial audio port, a CD quality stereo Digital-to-Analog Converter (DAC), an AES/EBU - S/PDIF compatible digital audio transmitter, and a serial control port. Figure 1 shows a typical connection diagram for the CS4922 in which a micro controller is used for loading the program code.

The CS4922 is based on a programmable DSP core. A typical application is the decoding of a compressed digital audio signal. Serial audio data broadcast on networks such as cable TV, direct broadcast satellite TV, or the telephone system can be decompressed and converted to standard analog and digital signals. A wide variety of standard and proprietary decompression algorithms can be supported. An assembler, a simulator, and a debugger are available. CS4922 DSP code is available which performs industry standard MPEG 1 and 2, layers I and II.

The DSP has a 24-bit fixed point data path, 5K words of program RAM, and 3K words of data RAM. The execution unit includes a 48-bit accumulator. Typical ALU instructions read operands

Figure 1. Typical Connection Diagram

from memory and store results back to memory. Modulo and bit reverse addressing are supported. For a sample rate of 48 kHz, the DSP can provide 18 MIPS.

The CS4922 includes a flexible clock manager. This section allows clock inputs on CLKIN to range from 256 kHz to 30 MHz, while producing the necessary DSP and DAC clocks through a programmable PLL.

The digital audio data is input through the serial audio port. Multiple data formats are supported by this port.

For analog reproduction of the digital input, a stereo DAC using delta-sigma architecture is built-in. Switched-capacitor filters perform most of the reconstruction process. Only a simple external passive filter is needed to complete reconstruction.

In addition to the analog output, an AES/EBU - S/ PDIF compatible output is provided. This allows the designer the flexibility of transmitting the audio data in a standard digital format to an external system. To facilitate the downloading of DSP code to the CS4922, a serial control port, communicating in either  $I^2C^{(B)}$  or SPI format, is used. This port may also be used during run time to issue control commands to the DSP.

#### 2. PERIPHERALS

Six on-chip peripherals make the audio decoder ideal for decoding broadcast digital audio signals. It has a PLL clock manager, a CD quality DAC, a digital audio transmitter, a three pin serial port for inputting audio data, a serial bi-directional auxiliary port for digital audio data, and an SPI/I<sup>2</sup>C port for serial control information. Each peripheral has I/O mapped data, control, and status registers. Many peripherals can also generate interrupts.

#### 2.1. Clock Manager

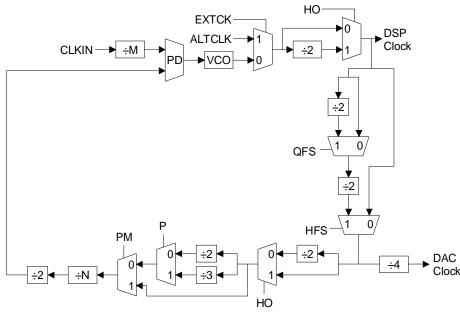

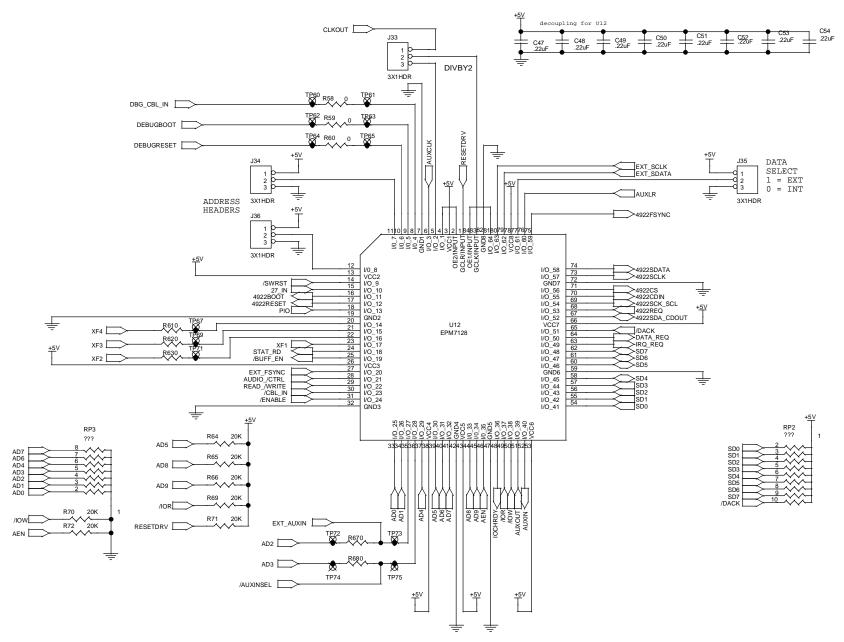

The clock manager is primarily a clock multiplier circuit that takes CLKIN input of any frequency from 256 kHz to 30 MHz and produces all the internal clocks required to run the DSP and the audio peripherals. A block diagram of the clock manager is shown in Figure 2.

Figure 2. Clock Manager

At the heart of the clock manager circuit is a PLL (Phase-Locked Loop) circuit. The PLL is configured to produce the appropriate DSP Clock for the desired sample rate. All other internal clocks required for the DAC and other peripherals are derived from this root clock.

The PLL's internal VCO requires a capacitor to be connected to the FLT pin (pin 31). The typical value of the FLT capacitor is 0.47  $\mu f$ , which is sufficient for all allowable CLKIN input frequencies. It must be stressed that the best analog performance can only be achieved by placing the capacitor as close as possible to the FLT pin and that the proper layout precautions be taken to avoid noise coupling onto the FLT pin.

The PLL generates the DSP clock by dividing the CLKIN input frequency by M and locking that reference clock to a divided down version of the DSP clock, whose frequency is set by the value of N in the CM1 register and the HO, HFS, P, and PM bits in the CM0 register. The clock manager circuitry can support sample rate frequencies in the range of 8 KHz to 50 KHz.

A typical CLKIN input frequency is the 27 MHz MPEG reference clock. Many other input frequency combinations are possible, such as the compressed bit rate of the input audio stream. Table 1 shows the recommended clock manager configuration for common sample rates with a 27 MHz CLKIN.

The external clock pin (EXTCK) specifies the function of ALTCLK. When EXTCK Is low, the internal VCO of the PLL is used to provide the DSP clock. If EXTCK is high, an external oscillator connected to ALTCLK can be used to generate the DSP clock. Note that the frequency of ALTCLK should typically be 512Fs or 768Fs for proper DAC clock generation. (The sampling rate is commonly called Fs). Additionally, the duty cycle of ALT-CLK should be as close to 50% as possible.

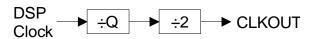

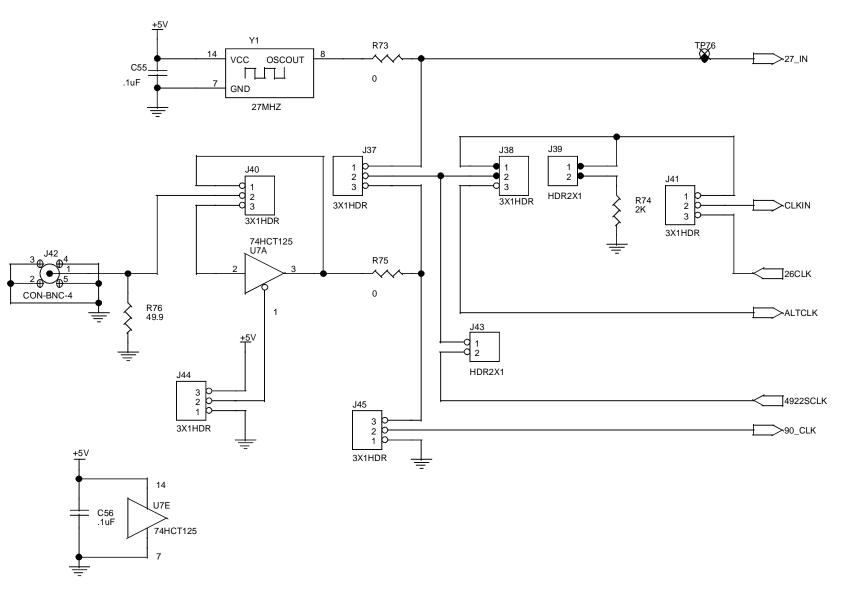

The CLKOUT pin is a divided version of the DSP clock. A diagram of the CLKOUT generation circuit is shown in Figure 3.

Figure 3. CLKOUT Generation Circuit

| Fs<br>(KHz) | М    | N   | Р | РМ | HFS | QFS | DAC Clock<br>(MHz) | DSP Clock<br>(MHz) |

|-------------|------|-----|---|----|-----|-----|--------------------|--------------------|

| 8           | 1125 | 64  | 1 | 1  | 1   | 1   | 1.536              | 24.576             |

| 16          | 3375 | 256 | 0 | 1  | 1   | 1   | 2.048              | 32.768             |

| 22.05       | 625  | 98  | 1 | 1  | 1   | 0   | 4.233              | 33.868             |

| 24          | 375  | 64  | 1 | 1  | 1   | 0   | 4.608              | 36.864             |

| 32          | 3375 | 512 | 0 | 1  | 1   | 0   | 4.096              | 32.768             |

| 44.1        | 625  | 196 | 1 | 1  | 0   | 0   | 8.467              | 33.868             |

| 48          | 375  | 128 | 1 | 1  | 0   | 0   | 9.216              | 36.864             |

Table 1. Enhanced Clock Manager Configuration

The DSP clock is divided by a programmable divider and an additional divide by 2 before being output. The divider output is stored in the ten bit field Q in the CM0 register. The divide by 2 guarantees a 50% duty cycle output. The Q value provides effective divides ranging from 1 to 1024, which means the frequency of CLKOUT can vary from the DSP clock frequency divided by 2 to the DSP clock frequency divided by 2048. CLKOUT can be used to synchronize external devices or generate most compressed bit rate clocks.

#### 2.2. 33-bit Counter

The 33-bit-counter can be used to support MPEG synchronization of audio and video. This loadable counter is targeted to operate at 90 kHz. The 90 kHz clock may be derived from a 27 MHz master clock provided at CLKIN (if available) or from a 90 kHz clock provided at Pin 19 90\_CLK. The selection of the counter clock is made via the register bit DIV in register CM0. When set, the DIV bit divides the clock at CLKIN by 300 and provides the divided clock to 33-bit-counter.

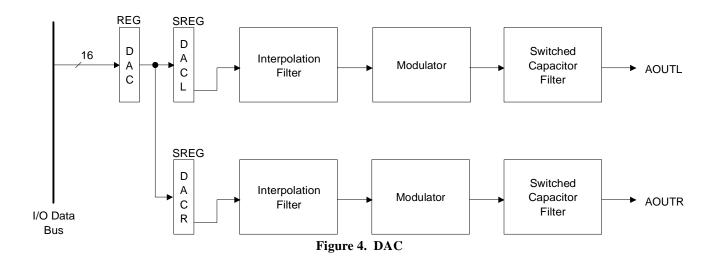

#### 2.3. Digital to Analog Converter

The digital to analog converter (DAC) is a dual channel CD quality DAC. It is designed with delta sigma architecture. The baseband audio is interpolated to 128Fs (192Fs) before going into the modulator. The modulator is third order and is followed by a 1 bit DAC/switch capacitor filter stage. An external passive filter completes the reconstruction process. The output is single ended with a drive capability down to 8 k $\Omega$ . Figure 4 is a block diagram of the DAC.

The interpolation filter produces images which are attenuated by at least 56 dB from .584Fs to 128Fs (192Fs). At a 48 kHz sample rate, a full scale signal at 20 kHz will produce an image at 28 kHz which is attenuated by more than 60 dB.

The out-of-band quantization noise from the delta sigma modulator extends from .417Fs to 128Fs (192Fs). This noise is attenuated by the switch capacitor filter and the continuous time filters. The total quantization noise and thermal noise from the analog filters integrated over the .417Fs to 128Fs (192Fs) is more than 50 dB below full scale power.

**Figure 5. Digital Audio Transmitter**

Left and right audio data are written to the DAC output register. This is a 16 bit write only register. The high 16 bits of the I/O data bus can be written to this register. The DACL and DACR output shift registers must be updated at the sample rate determined by the clock manager block. Feeding all zeros to the DAC register will produce a typical signal level of 2.2 volts.

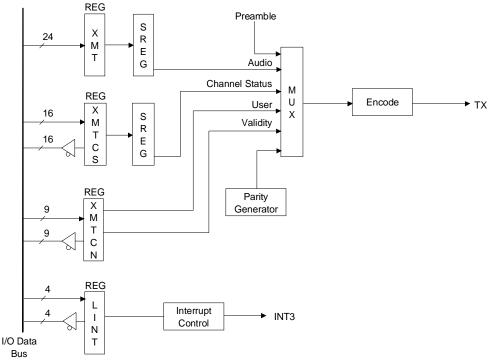

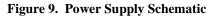

#### 2.4. Digital Audio Transmitter

The transmitter encodes digital audio data according to the Sony<sup>®</sup>/Philips<sup>®</sup> Digital Interface Format (S/PDIF) or the AES/EBU interface format. The encoded data is output on the TX pin. More information on the S/PDIF and AES/EBU standards are available from Crystal's application note library. The block diagram of the transmitter is shown in Figure 5.

The transmitter has a 24 bit write only register for audio data (XMT), a 16 bit read/write register for channel status data (XMTCS), and a read/write control register (XMTCN). The audio and channel status data are read from their registers and multiplexed with the validity and user bits from the control register, and the internally generated parity bit.

Figure 6. Audio Serial Input Port

#### 2.5. Audio Serial Input Port

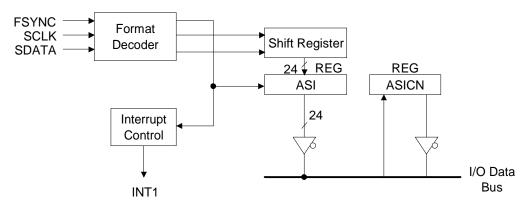

The audio serial input port has a three pin interface consisting of FSYNC, SCLK, and SDATA. SCLK clocks SDATA (serial data input) into the 24 bit input shift register. The contents of this shift register can be loaded into the Audio Serial Input (ASI) register by transitions of FSYNC or by a counter time out. An interrupt can be generated when ASI is loaded. Figure 6 shows a block diagram of the audio port.

The pulse mode (PUL) control bit in the audio serial port control register (ASICN) specifies whether both edges (PUL=0) or one edge (PUL=1) of FSYNC loads ASI. When configured to load on both edges, normal mode, up to 24 bits of data after a transition of FSYNC are clocked into the shift register. The next transition of FSYNC loads ASI with the contents of the shift register. Any number of SCLK periods can occur between FSYNC edges; the first 24 bits (or less) are accepted.

When the serial port is configured to load ASI on only one FSYNC edge, pulse mode, any number of SCLK periods can occur between active edges. ASI will be loaded on the active edge of FSYNC and every 16 or 24 SCLK periods after an active edge of FSYNC. The CNT16 bit in ASICN selects between 16 and 24 SCLK's. If FSYNC never toggles, ASI will be continuously loaded every 16 or 24 SCLK periods. The serial data is typically entered into the port MSB first. If at least 24 SCLK's occur between the times that ASI is loaded, the MSB of the input data will be loaded into the MSB of ASI. If the number of SCLK's between the times that ASI is loaded equals 24 minus N, the MSB will be loaded into the MSB minus N location in ASI. Shifting in software may be required to align the data.

The delay (DEL) bit in ASICN shifts the timing between FSYNC and SDATA by one SCLK period. When DEL is low, the MSB of the data in should occur immediately following a transition of FSYNC. When DEL is high, the MSB should occur one SCLK period after a transition of FSYNC.

The edge (EDG) bit internally inverts SCLK. When EDG is low, the falling edge of SCLK latches SDATA into the shift register. When EDG is high, the rising edge of SCLK latches SDATA.

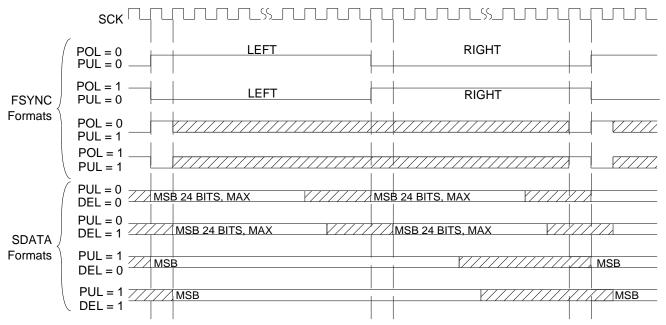

The polarity (POL) bit in ASICN inverts FSYNC. This switches the active edge of FSYNC in pulse mode. When not in pulse mode, FSYNC can be used to identify left and right channels of stereo audio data. When POL is low, FSYNC high identifies the left channel and when POL is high, FSYNC high identifies the right channel. Figure 7 shows the timing relationships of the various formats.

#### 2.6. Auxiliary Digital Audio Port

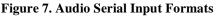

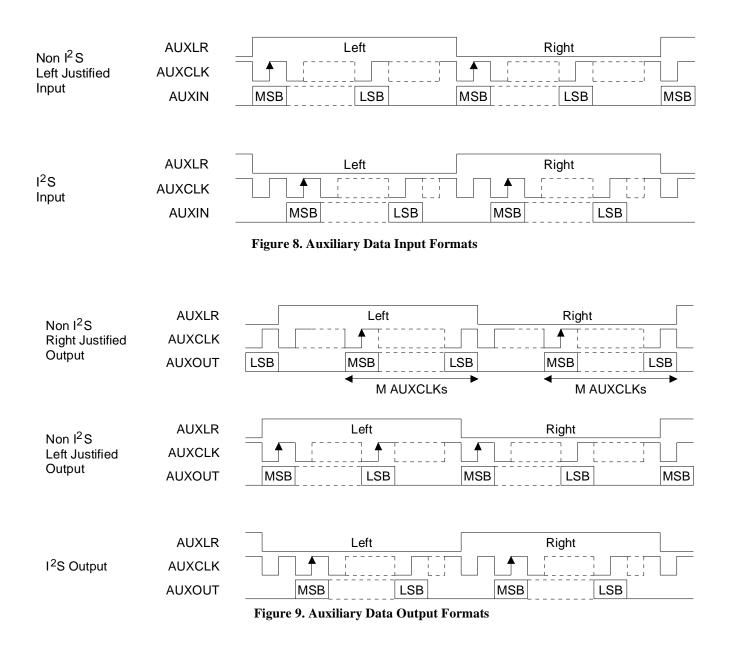

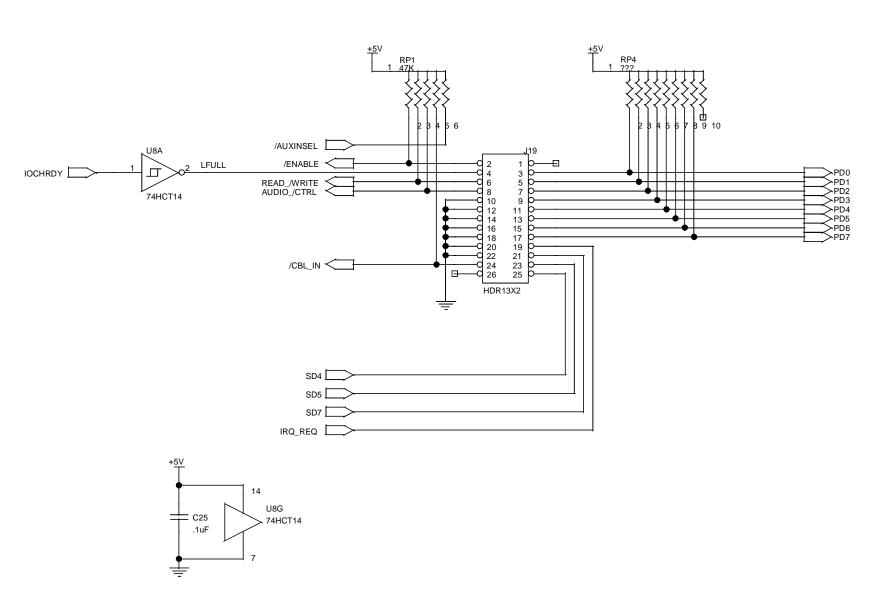

The CS4922 auxiliary port provides a path for the internal DSP core to directly read and write framed PCM digital audio data. The auxiliary port is designed to operate in a full duplex mode that can support simultaneous PCM input and output.

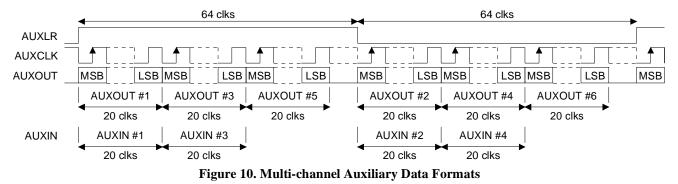

The DSP configures the port by programming the AUXCN Auxiliary Port Control Register. The port has the capability to support multiple digital audio formats. The formats are determined by AUXCN and each format is illustrated in Figures 8, 9, and 10. The input and output formats are controlled with the same register bits and thus are always in the same mode. The input and output sampling rates are the same as the sample rate for the on-chip DAC and are configured via the CM0 and CM1 clock manager control registers. The AUXCN mode settings provide the capability to support 16, 18, and 20 bit samples with up to 4 channels of input and 6 channels of output. The auxiliary interface is enabled or disabled by AUX-CN. AUXCN also provides a mechanism for scaling AUXCLK to be 32, 64, or 128Fs.

The CS4922 Auxiliary digital audio port physically is implemented with four device pins: AUXCLK pin 11, AUXLR pin 10, AUXIN pin 9, and AUX-OUT pin 8. AUXCLK is utilized as the primary synchronous clock. AUXOUT is the serial audio data output pin and AUXIN is the serial audio data input pin. AUXLR is an output pin used for framing the auxiliary digital audio port. AUXLR cycles at the same Fs as the on-chip stereo DAC. Fs is programmed by the DSP. AUXLR and AUXOUT transition with the falling edge of AUXCLK. The rising edge of AUXCLK samples AUXIN.

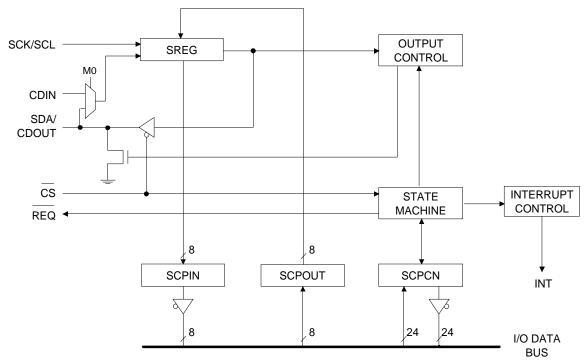

#### 2.7. Serial Control Port

The serial control port (SCP) can operate in  $I^2C$  or SPI compatible modes. In either mode, the control port performs eight bit transfers and is always configured as a slave. As a slave, it cannot drive the clock signal nor initiate data transfers. The port can request to be serviced by activating the REQ pin. The port is an asynchronous interface which provides interrupts and handshaking signals to allow communication between the on-chip DSP and an off-chip device such as a micro controller. Figure 12 shows a block diagram of the port.

## 2.7.1. $I^2C$ mode

The status of  $\overline{CS}$  sets the mode of the SCP during a hardware and software reset. If  $\overline{CS}$  is high during a reset the mode is I<sup>2</sup>C. Note that in most systems where I<sup>2</sup>C is the preferred control mode,  $\overline{CS}$  is connected to the digital supply.

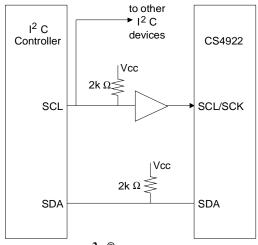

For normal  $I^2C$  operation SCL/SCK, SDA, and  $\overline{REQ}$  are used.  $\overline{CS}$  and CDIN are typically connected to the digital supply. SCL/SCK is the serial clock input which is always driven by an external device. SDA is the serial data Input/Output signal.  $\overline{REQ}$  is the active low request signal, which is driven low when there is valid data in the serial control port output SCPOUT register.

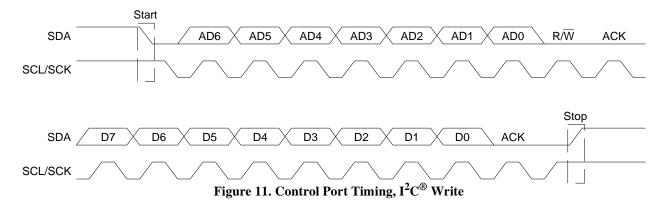

As an  $I^2C$  compatible port, data is communicated on the SDA pin and is clocked by the rising edge of SCL/SCK. The Philips  $I^2C$  bus specification provides details of this interface. Note the CS4922 does not meet the rise time specification of the SCL/SCK signal. For more details please refer to the section on Rise Time of SCL/SCK.

Figure 11 shows the relative timing necessary for an  $I^2C$  write operation for a single byte. A 'write' is defined as the transfer of data from an  $I^2C$  bus master to the CS4922 serial control port. A transfer is initiated with a start condition followed by a 7 bit address and a read/write bit (set low for a write). This address is the address assigned to the device being written to during the transfer. In the case of the CS4922, this address is stored in the SCPCN register. Immediately following power up, the CS4922's Address checking Enable (AEN) bit is set to zero. The AEN bit must be set high for the CS4922 to compare the address of the intended  $I^2C$ device on the bus to its internal address. This means the CS4922 will respond to any address on the  $I^2C$ bus until its address is initialized and address checking is enabled. To avoid bus conflicts the CS4922 should be held in reset (RESET active low) until the master is ready to communicate with the CS4922 and sets the address in the SCPCN. The address can only be set using the I<sup>2</sup>C bus interface, so the master should use the intended  $I^2C$  address when downloading microcode to the CS4922 to avoid conflict with other devices on the bus. Once the microcode is loaded into the CS4922 the microcode should either initialize the I<sup>2</sup>C address or provide a means for the master to program the  $I^2C$ address. If the CS4922 is the only device on the  $I^2C$ bus, address checking is optional. However, I<sup>2</sup>C bus protocol is still required. In other words, the address bits and read/write bit are still required.

If a write to the CS4922 is specified, 8 bits of data on SDA will be shifted into the input shift register as shown in Figure 12. When the shift register is full, the 8 bit data is transferred to the Serial Control Port Input (SCPIN) register on the falling edge of the 8th data bit. An acknowledge (ACK) is sent back to the master and the input ready flag (IRDY) flag is set. This flag generates an interrupt on interrupt line 2 if the input ready interrupt enable

(IRIEN) bit is set high. The interrupt vector is 0006H.

The master can continue to send data, but is will be rejected if the IRDY has not yet been cleared. This flag is cleared by reading the SCPIN register. If a byte is rejected, the reject (REJ) flag in the Long Interrupt (LINT) register is set. A rising edge of the REJ flag generates an interrupt on interrupt line 3 if the reject interrupt enable (RJIEN) bit is set high. The REJ flag is cleared by reading SCPCN. If the CS4922 fails to ACK it is possible that the byte was rejected and it should be transmitted again. If the second attempt fails the CS4922 should be issued a hardware reset to reinitialize the communication path.

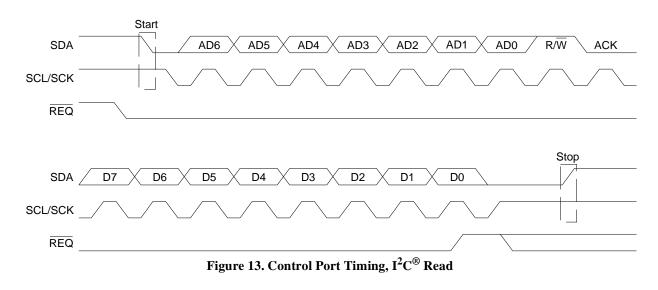

If the DSP core of the CS4922 wants to send a byte to the master, it first writes the byte to the Serial Control Port Output (SCPOUT) register. Note the DSP only sends 8 bits per transfer to the SCPOUT register. A write to the SCPOUT sets the request pin ( $\overline{REQ}$ ) active low. The master must recognize the request and issue a read operation to the DSP. Figure 13 shows the relative timing of a single byte read. The master must send the 7 bit address (if address checking is enabled it must match the address in the SCPCN register) and the read bit. For I<sup>2</sup>C protocol, it is always the device receiving the transfer that must ACK. Therefore, the CS4922 will ACK the address and the read bit. After the ACK by the CS4922 (the falling edge of SCL/SCK), the serial shift register is loaded with the byte to be sent and the most significant bit is placed on the SDA line.

The 8 bit value in the serial shift register is shifted out by the master. The data is valid on the rising edge of SCL/SCK and transitions immediately following the falling edge. For I<sup>2</sup>C the  $\overline{\text{REQ}}$  line will be de-asserted immediately following the rising edge of the last data bit of the current byte being transfered, if there is no data in the SCPOUT register. The  $\overline{\text{REQ}}$  line is guaranteed to stay de-asserted (high) until the rising edge of the SCL/SCK for the

ACK. This signals the host that the transfer is complete.

If there is data placed in SCPOUT prior to the rising edge of SCL/SCK for the last data bit, then  $\overline{\text{REQ}}$  will remain asserted (low). Immediately following the falling edge of SCL/SCK for the ACK, the new data byte will be loaded into the serial shift register. The host should continue to read this new byte. It is importat to note that once the data is in the shift register, clocks on the SCL/SCK line will shift the data bits out of the shift register. A STOP condition on the bus will not prevent this from occuring. The host must read the byte prior to any other bus activity or the data will be lost.

If data is placed in SCPOUT after the rising edge of SCL/SCK for the last data bit, but before the rising edge of SCL/SCK for the ACK,  $\overline{\text{REQ}}$  will not be asserted until after the rising edge of SCL/SCK for the ACK. This should be treated as a completed transfer. The data written to SCPOUT will not be loaded into the shift register on the falling edge of SCL/SCK for the ACK. Therefore, a new read operation is required to read this byte.

#### 2.7.2. Rise Time on SCL/SCK

The Philips  $I^2C$  bus specification allows for rise times of the SCL/SCK line up to 1 µs. The CS4922

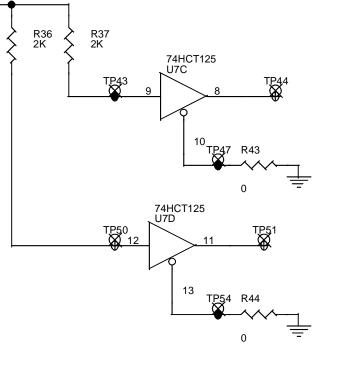

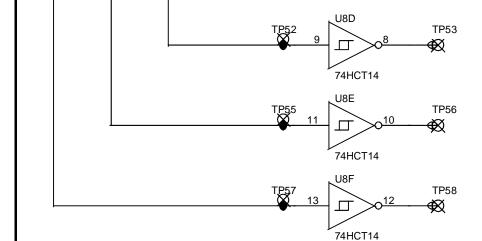

does not meet this specification. If the I<sup>2</sup>C bus master(s) has a rise time in excess of 50 ns the CS4922 will be unable to reliably communicate across the bus. In some systems a stronger pull-up resistor on the SCL/SCK line will provide the rise time needed for proper operation, but this is only helpful when the current rise time is near 50 ns. In cases where the CS4922 will be used in a system where a longer rise time on SCL/SCK is expected, a CMOS compatible buffer should be used. Figure 14 shows the necessary connections. Note the buffer is only used for the SCL/SCK connecting directly to the CS4922. Other devices on the I<sup>2</sup>C bus may need to hold SCL/SCK low while accepting data.

Figure 14. I<sup>2</sup>C<sup>®</sup> Connection Diagram

Figure 15. Control Port Timing, SPI Write

#### 2.7.3. SPI mode

The status of  $\overline{CS}$  sets the mode of the SCP during a hardware and software reset. If  $\overline{CS}$  is low during a reset the mode is SPI. It is important to note that  $\overline{CS}$  should be low when either a hardware of software reset is issued to ensure the mode remains SPI.

For normal SPI operation SCL/SCK,  $\overline{CS}$ , CDIN, CDOUT and  $\overline{REQ}$  are used. SCL/SCK is the serial clock input which is always driven by an external device.  $\overline{CS}$  is the active low enable signal. CDIN is the control data input. CDOUT is the control data output.  $\overline{REQ}$  is the active low request signal, which is driven low when there is valid data in the serial control port output SCPOUT register.

As an SPI compatible port, data is communicated on the CDIN and CDOUT pins and is clocked by the rising edge of SCL/SCK.  $\overline{CS}$  is used to select the device on which the CDIN and CDOUT signals will be valid.

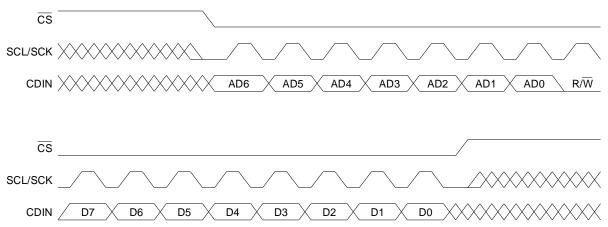

Figure 15 shows the relative timing necessary for an SPI write operation of a single byte. A 'write' is defined as the transfer of data from an SPI bus master to the CS4922 serial control port via CDIN. A transfer is initiated with  $\overline{CS}$  being driven active low. This is followed by a 7 bit address and a read/ write bit (set low for a write). For SPI mode, this address is typically not used, however it is still necessary to clock an address across the bus followed by the read/write bit.

If a write to the CS4922 is specified, 8 bits of data on CDIN will be shifted into the input shift register as shown in Figure 12. When the shift register is full, the 8 bit data is transferred to the Serial Control Port Input (SCPIN) register on the falling edge of the 8th data bit.

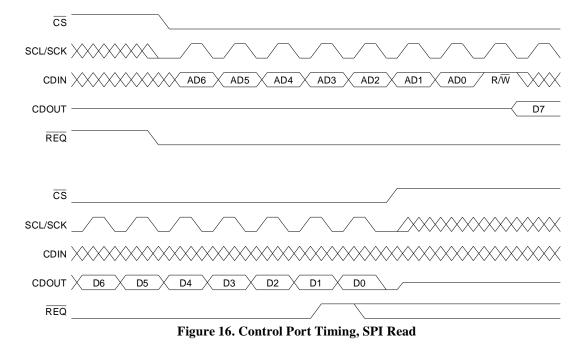

If the DSP core of the CS4922 wants to send a byte to the master, it first writes the byte to the Serial Control Port Output (SCPOUT) register. Note the DSP only sends 8 bits per transfer to the SCPOUT register. A write to the SCPOUT sets the request pin (REQ) active low. The master must recognize the request and issue a read operation to the DSP. Figure 16 shows the relative timing of a single byte read. The master must send the 7 bit address (if address checking is enabled it must match the address in the SCPCN register) and the read bit. After the the falling edge of SCL/SCK for the read/write bit, the serial shift register is loaded with the byte to be sent and the most significant bit is placed on the CDOUT line.

The 8 bit value in the serial shift register is shifted out by the master. The data is valid on the rising edge of SCL/SCK and transitions immediately following the falling edge. For SPI, the  $\overline{\text{REQ}}$  line will be de-asserted immediately following the rising

edge of the second to last data bit, of the current byte being transferred, if there is no data in the SCPOUT register. The  $\overline{\text{REQ}}$  line is guaranteed to stay de-asserted (high) until the rising edge of the SCL/SCK for the last data bit. This signals the host that the transfer is complete.

If there is data placed in SCPOUT prior to the rising edge of SCL/SCK for the second to last data bit, then  $\overline{\text{REQ}}$  will remain asserted (low). Immediately following the falling edge of SCL/SCK for the last data bit, the new data byte will be loaded into the serial shift register. The host should continue to read this new byte. It is important to note that once the data is in the shift register, clocks on the SCL/ SCK line will shift the data bits out of the shift register. The host should read the byte prior to any other bus activity or the data will be lost. If  $\overline{\text{CS}}$  is deasserted SCK/SCL will not shift the data out. However the data is still in the shift register. Once  $\overline{\text{CS}}$ becomes active (low) each SCL/SCK will shift the data out of the register.

If data is placed in SCPOUT after the rising edge of SCL/SCK for the second to last data bit, but before the rising edge of SCL/SCK for the last data bit,

**REQ** will not be asserted until after the rising edge of SCL/SCK for the last data bit. This should be treated as a completed transfer. The data written to SCPOUT will not be loaded into the shift register on the falling edge of SCL/SCK for the last data bit. Therefore, a new read operation is required to read this byte.

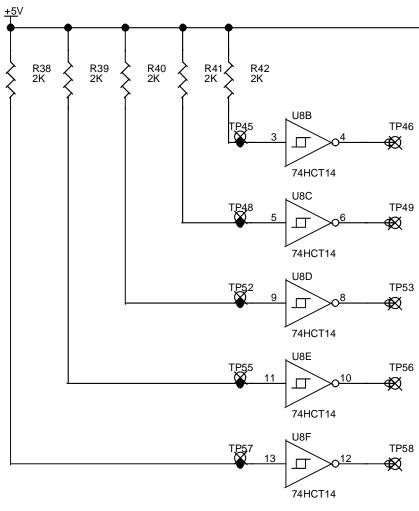

#### 2.8. User Definable Pins

The CS4922 has five pins which can be defined by the user, XF1-XF4 and PIO. The XF signals can be used as output pins. The PIO signal may be either an input or an output pin.

When active the XF4:XF1 bits in the LINT register are mapped directly to the XF pins. (For backwards compatibility with the CS4920A, XF1 can be accessed via the CM0 register as well.) An external pull-up (2.2 k $\Omega$  typical) is required for proper operation on each pin. An example application for this signal would be to use the pin as a request for audio data.

The PIO signal direction is configured by the  $I_O$  bit in the LINT register. When  $I_O = 0$  the PIO signal is configured as an input. The  $I_O$  bit is zero

following the power up and any reset. As an input, the level on the PIO pin is mapped to the PIN bit of the LINT register. A rising edge of the PIN bit will generate a interrupt on line 3 if the PIEN bit is set to one. The LINT register must be read to clear this interrupt.

If the I\_O bit is set to a logic one, the PIO pin is an output. A pull-down resistor (10 k $\Omega$  typical) is required for proper operation. As an output, the POUT bit of the LINT register is mapped directly to the PIO pin.

#### **3. BOOT PROCEDURE**

Program and data RAM must be loaded from external memory after power up or when a new program needs to be loaded. During the loading procedure (boot), data is transferred through the serial control port to program and data memory. This procedure is controlled by a program stored internally in ROM.

Following a power up or reset, the fast mode bit (FSTB) is cleared. This places the CS4922 into a 'fast mode'. While the serial control port (SCP) still conforms to the data format determined by  $\overline{CS}$  on power up, the port can be operated at much higher bit rates to facilitate faster downloading of the DSP code. Once the code has been loaded the software can set the FSTB for normal communication in either SPI or I<sup>2</sup>C. Since the CS4922 is always a slave this fast mode will not affect the operation of other devices sharing the same communication bus.

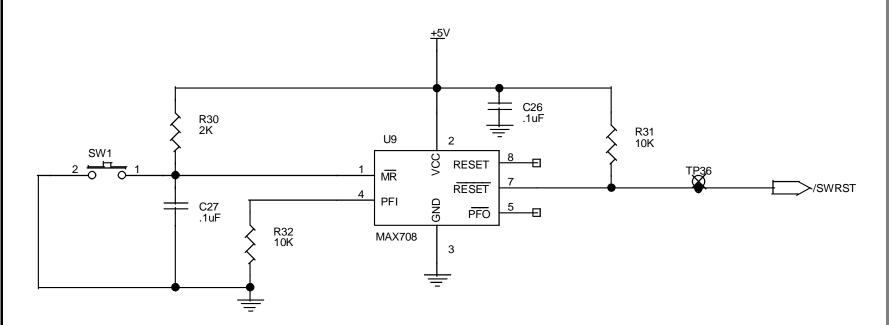

The boot procedure is initiated by a low to high transition of the reset (RESET) pin with the BOOT pin high. This initializes the program counter to location  $1000_{\text{H}}$ , the first location in ROM. After the ROM program transfers data from the control port to memory, it issues a software reset. This is done by writing a one to the RS (reset) bit in the control register. The software reset clears all registers in-

cluding the program counter, which transfers control to the new program in RAM.

A hardware reset (RESET pin toggled low) has the same affect as a software reset. During the boot procedure, all interrupts, except the debug interrupt, are disabled.

The CS4922 will boot from a micro controller using the serial control port. When booting, it can communicate in an I<sup>2</sup>C or SPI format. If the  $\overline{CS}$ (chip select) pin is high when boot is initiated, the port will communicate in I<sup>2</sup>C format. If the  $\overline{CS}$  pin is low when boot is initiated, the port will communicate in SPI. Please refer to the timing requirements found at the beginning of this document.

Nodes in an  $I^2C$  network have unique network addresses. A message in an  $I^2C$  network consists of the address of the node receiving the message followed by the message data. When the control port is configured for  $I^2C$  format, it normally compares the address to an address stored in an internal register. During the boot procedure, the control port is programmed to ignore the address. The SCP section on  $I^2C$  operation explains the mechanics of writing to the CS4922.

The boot program in internal ROM expects data transferred through the control port to have the proper file format. The first two bytes contain the starting address for the following block of data. The starting address is 13 bits with the 13th bit specifying program or data memory. Therefore, the upper 3 bits of these two bytes are discarded internally. The second two bytes contain the length of the block of data. Successive bytes are concatenated into 24 bit words. These words are sequentially loaded into program and data memory beginning at the starting address.

Any number of blocks of data can be loaded. Two bytes containing FF and 3 bytes containing a check

sum must follow the last block of data. This check sum is generated by summing all the previous data, address, and length bytes and truncating to 24 bits. This check sum is compared to the value calculated internally. If they do not match, the  $\overline{\text{REQ}}$  (request) pin is pulled low and the processor does not issue the software reset. It stays in a loop until boot is initiated again.

# 4. COMMON CS4922 INTERFACE ROUTINES

The following common CS4922 routines are modified excerpts from the CDB4922 evaluation board software. When reviewing these routines, keep in mind that timing requirements will change based on the performance of the host processor. Please refer to the "Switching Characteristics", "Serial Control Port", and "Boot Procedure" sections in the CS4922 data sheet.

#### 4.1. Boot Procedure Routine

The CS4922's on-board RAM is ready to be loaded after a RESET pulse while the BOOT pin is high. The host then sends the CS4922's microcode image to the CS4922's serial host port (the host may send the data in either  $I^2C$  or SPI mode, based on the state of the  $\overline{CS}$  pin during the RESET pulse).

Upon completion of download the CS4922's  $\overline{\text{REQ}}$  pin should be checked to verify that the download was successful. If the REQ pin is high, then the download was good. (note: the  $\overline{\text{REQ}}$  will remain high if no data is sent to the CS4922 or if the data is stopped. Therefore, for debugging purposes a microcode image with a bad checksum should be used to simulate a bad download and verify that the image is truly being sent successfully.)

| /*   |                         |      |                                 |

|------|-------------------------|------|---------------------------------|

|      | Function                | :    | boot_4922()                     |

|      | Return                  | :    | None                            |

|      | Arguments               | :    | None                            |

|      | Description             | :    | This function boots the CS4922. |

| */   |                         |      |                                 |

|      | 1 1 1000/               | • •  |                                 |

| VOID | boot_4922(vo            | old) |                                 |

| {    |                         | N    |                                 |

|      | BOOT(HIGH               | 1);  | /* hald 1 */                    |

|      | pause(1);               | M.   | /* hold 1 us */                 |

|      | RESET(LOV               | v);  | /* hold E0 up */                |

|      | pause(50);<br>RESET(HIG | ц).  | /* hold 50 us */                |

|      | pause(1);               | п),  | /* hold 1 us */                 |

| ۱    | pause(1),               |      |                                 |

| ſ    |                         |      |                                 |

## Figure 17. Sample pseudo C code for initializing the CS4922 for downloading.

| CS(HIGH);<br>byte_load_count=0;<br>boot_4922();<br>pause(2000);<br>Send_I2C(START);<br>Write_Byte(ADDR4922 & WRITE);                          | /* Set the CS pin high */<br>/* Note: for I2C mode this pin should be kept high */<br>/* toggle the lines to initiate download */<br>/* delay 2 ms */<br>/* Send I2C start condition */<br>/* Send I2C address with R/W bit set to WRITE */<br>/* Note: I2C address is not checked, but still must be sent */ |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>if (get_ACK()) {      printf("error sending address byte for write condition \n");      fclose(scp_in);      return(1); } do {</pre>     | /* Check if the CS4922 acknowledges the address byte sent */                                                                                                                                                                                                                                                  |

| if (fgets( &hexin, 80, scp_in ) != NULL) {                                                                                                    | /* Get the next byte in the microcode image file to send to the CS4922 */                                                                                                                                                                                                                                     |

| sscanf( &hexin, "%2x", &val );<br>Write_Byte( val );                                                                                          | /* Send the next byte to the CS4922 */                                                                                                                                                                                                                                                                        |

| byte_load_count++;<br>if (get_ACK())<br>{<br>error = 1;<br>printf("Error transferring data on I<br>no ACK\n",byte_load_count);<br>break;<br>} | /* Check if the CS4922 acknowledges the byte sent */                                                                                                                                                                                                                                                          |

| }<br>} while ( !feof(scp_in));                                                                                                                |                                                                                                                                                                                                                                                                                                               |

| Send_I2C(STOP);                                                                                                                               | /* Send I2C stop condition */                                                                                                                                                                                                                                                                                 |

| pause(2000);                                                                                                                                  | /* give time (2ms) for 4922 to respond */                                                                                                                                                                                                                                                                     |

| if (get_req() && !error)<br>printf ("Download complete\n");<br>else<br>{                                                                      | /* Check the status of the CS4922's REQ pin */<br>/* REQ = high, PASS */                                                                                                                                                                                                                                      |

| printf("Download failure\n");<br>}                                                                                                            | /* REQ = low, FAIL */                                                                                                                                                                                                                                                                                         |

Figure 18. Sample pseudo C code for downloading the CS4922 in I<sup>2</sup>C Mode.

| CS(LOW);<br>byte_load_count=0;<br>boot_4922();<br>pause(2000);<br>CS(HIGH); | /* Set the CS pin low */<br>/* toggle the lines to initiate download */<br>/* delay 2 ms */<br>/* Set the CS pin high */               |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| wait(200);                                                                  | /* delay 200 ns */                                                                                                                     |

| CS(LOW);<br>Write_Byte(ADDR4922 & WRITE);                                   | /* Set the CS pin low */<br>/* Send address with R/W bit set to WRITE */<br>/* Note: address is not checked, but still must be sent */ |

| do<br>{<br>if (fgets( &hexin, 80, scp_in ) != NULL)<br>{                    | /* Get the next byte in the microcode image file to send to the CS4922 $^{\prime\prime}$                                               |

| sscanf( &hexin, "%2x", &val );<br>Write_Byte( val );<br>byte_load_count++;  | /* Send the next byte to the CS4922 */                                                                                                 |

| }<br>} while ( !feof(scp_in));                                              |                                                                                                                                        |

| pause(2000);                                                                | /* give time (2ms) for 4922 to respond */                                                                                              |

| CS(HIGH);                                                                   | /* Set the CS pin high */                                                                                                              |

| if (get_req() && lerror)<br>printf("Download complete\n");<br>else<br>{     | /* Check the status of the CS4922's REQ pin */<br>/* REQ = high, PASS */                                                               |

| printf("Download failure\n");<br>}                                          | /* REQ = low, FAIL */                                                                                                                  |

Figure 19. Sample pseudo C code for downloading the CS4922 in SPI Mode.

#### 4.2. Writing a Byte(s) to the Host Port

The host port of the CS4922 can be configured for  $I^2C$  or SPI mode. Writing a byte(s) to host port in  $I^2C$  mode begins with the host sending an  $I^2C$  start condition (SDA pin goes low while the SCL/SCK pin is high). The host must then send a 7-bit address followed by a R/W bit set to zero (the address must be sent even if the host port is not configured for address checking). The CS4922 will respond with a one bit acknowledge (ACK) after receiving the address and R/W bit. If the byte was received successfully, the ACK will be low. At this point the  $I^2C$  interface is configured to receive bytes from the host. The host may send multiple bytes (check-

ing for ACKs between every byte). The write process is stopped by the host sending an  $I^2C$  stop condition (SDA pin goes high while the SCL/SCK pin is high).

Writing a byte(s) to the host port in SPI mode begins with the host setting the  $\overline{CS}$  pin of the CS4922 low. The host must then send a 7-bit address followed a R/W bit set to zero (the address must be sent even if the host port is not configured for address checking). At this point the SPI interface is configured to receive bytes from the host. The host may send multiple bytes. The write process is stopped by the host raising the  $\overline{CS}$  pin of the CS4922.

```

SCL(HIGH);

/* Set SCL in default state */

SCL(HIGH);

/* Set SCL in default state */

SDA(HIGH);

SDA(HIGH);

/* Set SDA in default state */

/* Set SDA in default state */

Send_I2C(START);

CS(LOW);

pause(5);

/* hold for 5 us */

Write_Byte(ADDR4922 & WRITE);

pause(5);

/* hold for 5 us */

if(get_ACK())

{

Write_Byte(ADDR4922 & WRITE);

printf("error sending address byte for write condition\n");

return(1);

Write_Byte(first_byte);

}

Write_Byte(second_byte);

Write_Byte(first_byte);

if(get_ACK())

Write_Byte(third_byte);

{

printf("error sending byte \n");

Send_I2C(STOP);

return(ERROR);

CS(HIGH);

}

Figure 20. Sample pseudo C code for writing bytes

Write_Byte(second_byte);

to the CS4922 in SPI Mode.

if(get_ACK())

{

printf("error sending byte \n");

Send_I2C(STOP);

return(ERROR);

}

Write_Byte(third_byte);

if(get_ACK())

{

printf("error sending byte \n");

Send_I2C(STOP);

return(ERROR);

}

Send_I2C(STOP);

```

Figure 21. Sample pseudo C code for writing bytes to the CS4922 in I<sup>2</sup>C Mode.

```

-----*/

/*---

/*

Function

Send_I2C()

:

Return

None

:

Arguments :

select, tells the function if its a start or stop condition

Description :

This function is used to begin or end an I2C data transfer.

*/

void Send_I2C(char select)

{

if (select==START)

{

SDA(LOW);

/* drive SDA low while SCL is high for start condition */

pause(5);

/* hold for 5 us */

SCL(LOW);

/* drive SCL low for writing address */

pause(5);

/* hold for 5 us */

}

/* STOP condition */

else

{

SDA(LOW);

/* make sure SDA is low */

pause(5);

/* hold 5 us */

SCL(HIGH);

/* drive SCL high */

pause(5);

/* hold 5 us */

SDA(HIGH);

/* drive SDA for the STOP condition */

}

}

```

```

/*

-----*/

/*

Function

get_ACK()

:

returns 1 if I2C bus fails to ACK else

Return

:

returns 0

Arguments :

None

Description :

The get_ACK function will send the 9th clock of the SCL line and verify the slave has

acknowledged the transfer by driving the SDA line low.

*/

char get_ACK(void)

{

char ack;

SCL(HIGH);

/* latch the ACK */

/* Read the SDA pin */

ack = (char) (((inportb(gbStat_reg)) & SDA_POS)>>SDA_BIT);

SCL(LOW);

return(ack);

}

```

```

-----*/

1*-

1*

Function

Write_Byte()

Return

None

:

Arguments :

char write_byte

Description :

this function will write write_byte onto the I2C lines MSB first

*/

void Write_Byte(char write_byte)

int bit_number;

for (bit_number=7;bit_number>=0;bit_number--)

{

if((write_byte>>bit_number)&0x01)

/* check each bit to write */

SDA(HIGH);

/* Send a one */

else

SDA(LOW);

/* Send a zero */

SCL(HIGH);

/* latch the bit into the CS4922 */

pause(5);

/* hold for 5 us */

/* Set the clock line back low */

SCL(LOW);

}

SDA(HIGH);

/*release bus so 4922 can ACK*/

}

Figure 24. Sample pseudo C code for writing a byte to the I<sup>2</sup>C CS4922 host port.

/*-----*/

/*

Function

Write_Byte()

Return

None

Arguments :

char write_byte

Description :

this function will write write_byte onto the SPI lines MSB first

*/

void Write_Byte(char write_byte)

{

int bit_number;

for (bit_number=7;bit_number>=0;bit_number--)

{

if((write_byte>>bit_number)&0x01)

/* check each bit to write */

CDIN(HIGH);

/* Send a one */

else

CDIN(LOW);

/* Send a zero */

SCL(HIGH);

/* latch the bit into the CS4922 */

/* hold for 5 us */

pause(5);

SCL(LOW);

/* Set the clock line back low */

}

CDIN(HIGH);

/*return data line to default state*/

}

```

#### 4.3. Reading a Byte(s) from the Host Port

Reading a byte(s) from the host is initiated by the CS4922 setting the  $\overline{\text{REQ}}$  pin low. The  $\overline{\text{REQ}}$  pin will remain low until the data is read from the host port of the CS4922. When the host port is configured for  $I^2C$  mode, the host will initialize the CS4922's serial port for a read operation by sending an  $I^2C$  start condition followed by a 7-bit address and the R/W bit set to one. The host then will read 8-bits of data from the CS4922, check the status of the  $\overline{\text{REQ}}$  pin, and then send an I<sup>2</sup>C ACK. If the  $\overline{\text{REQ}}$  pin was low, then the CS4922 has another byte pending and the host must read the next byte (if the host instead sends an I<sup>2</sup>C stop condition, then the next byte will be lost). The host must send an  $I^2C$  stop condition if the status of the  $\overline{\text{REQ}}$  pin was high (the  $\overline{\text{REQ}}$  pin may go low again after the host sends the ACK, but the host must still send an  $I^2C$  stop condition).

For an SPI read, the host will initialize the CS4922's serial port for a read operation by setting the  $\overline{CS}$  pin low followed by sending 7-bits of address and the R/W bit set to one to the CS4922's host port. The host then will read 7-bits of data from the CS4922, check the status of the  $\overline{\text{REQ}}$  pin, and then read the  $8^{th}$  bit of data. If the  $\overline{\text{REQ}}$  pin was low, then the CS4922 has another byte pending and the host must read the next byte (if the host instead raises the  $\overline{CS}$  pin, then the next byte will be lost). After reading the  $8^{\text{th}}$  bit the host must raise the  $\overline{\text{CS}}$ pin to a high state if the status of the  $\overline{\text{REQ}}$  pin was high (the  $\overline{\text{REQ}}$  pin may go low again after the host reads the  $8^{th}$  bit, but the host must still raise the  $\overline{CS}$ pin).

```

while (get_req() && !kbhit());

/* Wait until REQ pin goes low */

if (!get_req())

/* read stream of output */

```

SCP Read();

Figure 26. Sample pseudo C code for reading bytes from the CS4922 host port.

```

char SCP_Read(void)

unsigned char DataIn = 0;

char notendofread = 1;

/* Setup port for I2C read */

Send_I2C(START);

Write Byte(ADDR4922 | READ);

if (get_ACK())

{

printf("error sending address byte for read condition \n");

return(ERROR);

}

/* Read data until REQ goes high */

do

{

notendofread = Read Byte(&DataIn);

printf("%02x ", DataIn);

}while (notendofread);

return(0);

}

```

Figure 27. Sample pseudo C code function for handling multi-byte reads in I<sup>2</sup>C mode from the CS4922 host port.

```

char SCP_Read( void )

{

unsigned char DataIn = 0;

char notendofread = 1;

/* Setup port for SPI read */

CS(LOW);

Write_Byte(ADDR4922 | READ);

/* Read data until REQ goes high */

do

{

notendofread = Read_Byte(&DataIn);

printf("%02x ", DataIn );

}while (notendofread);

return(0);

}

```

Figure 28. Sample pseudo C code function for handling multi-byte reads in SPI mode from the CS4922 host port.

```

CS4922

```

```

----*/

/*

Function

Read_Byte()

returns flag to indicate if a STOP condition has been sent. Returns 1 if no STOP has been sent, 0 if

Return

•

STOP has been sent.

Arguments :

*int -> address of byte to be read from the CS4922 SCP port.

This function reads a byte of data from the SCP port and replies with an ACK if there is still more

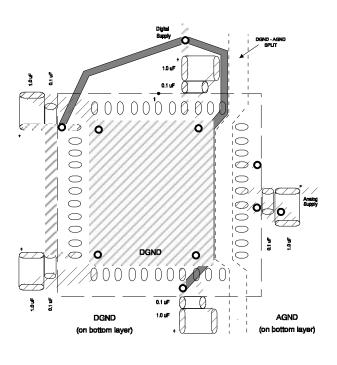

Description :