# F8680 PC/CHIP

Data Sheet

|  | <br> |  |  |

|--|------|--|--|

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

|  |      |  |  |

#### Copyright Notice

Manual Copyright © 1993, Chips and Technologies, Inc. All Rights Reserved. Printed in U.S.A.

#### Trademark Acknowledgement

CHIPS® and the CHIPS logotype are registered trademarks of Chips and Technologies, Inc. PC/CHIPTM, SuperStateTM, Virtual I/OTM, Virtual InterruptsTM, and Visual MapTM are trademarks of Chips and Technologies, Inc. IBM® is a registered trademark of International Business Machines, Inc. AT&T® is a registered trademark of AT&T Bell Laboratories.

National® is a registered trademark of National Semiconductor Corp. 386SX<sup>TM</sup> is a trademark of Intel Corp.

#### Disclaimer

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, ro translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without express written permission of Chips and Technologies, Inc.

The information contained in this document is being issued in advance of the production cycle for the device(s). The parameters for the device(s) may change before final production.

Chips and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or changes.

The information contained in this manual is provided for general use by our customers. Our customer should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### Restricted Frights and Limitations

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600

# F8680 PC/CHIP™

#### **Product Brief**

A true single-chip PC, the F8680 PC/CHIP™ features the SuperState™ R management system, low power consumption, high performance, direct PCMCIA card support, power management, and flexible memory support.

Chips and Technologies, Inc. has designed the F8680 microchip to accommodate a wide variety of low power, cost-sensitive DOS applications: palmtop, laptop, and desktop computers, electronic notebooks and handhelds, and embedded controller systems. Third-party designers can build complete systems around the F8680 chip by adding only memory, storage, and peripheral devices.

### Features

The F8680 PC/CHIP has the following features:

- 3.3V/5V operation, fully static design, and intelligent sleep mode reduce power consumption approximately 60 percent and allow direct battery drive.

- PC-compatible design supports PC software and 8-bit ISA cards.

- SuperState R mode provides a separate operating environment and enables complete I/O and interrupt monitoring without BIOS modification.

- Virtual I/O™ feature allows device emulation as well as I/O monitoring and control.

- Virtual Interrupts™ feature allows interrupts to be monitored and/or redirected before any operating system, application program, or TSR sees them.

- Four-stage pipeline and 14MHz operation give performance comparable to a 286 or 386SX™ system.

- 26-bit address bus enables 64MB memory map and allows direct support of PCMCIA memory card.

- · Flexible memory management supports PCMCIA cards and up to three banks of PSRAM, SRAM, and/or DRAM.

- Bank switching and high memory access overcome the 1MB addressing limitation of the 8086 processor, and enable PCMCIA and EMS support.

- Single CGA controller manages a CRT or LCD panel display and requires only a single 32Kx8 SRAM to minimize power consumption and board space.

- Visual Map<sup>TM</sup> gray scaling provides excellent visual contrast on any LCD panel.

- 16C450-compatible UART supports COM1 or COM2.

- Over 100 configuration registers allow flexibility, control, and differentiation in system design.

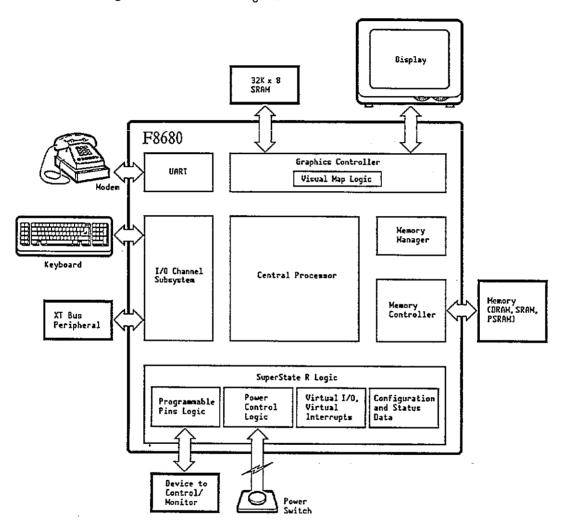

A block diagram of the F8680 PC/CHIP is shown in Figure 1.

Figure 1. F8680 Block Diagram

## Contents

| F8680 PC    | CHIP                                        |

|-------------|---------------------------------------------|

| Introductio |                                             |

| Pin Descrip | otion                                       |

| Signal Des  | cription                                    |

| Functional  | Description                                 |

| Centra      | 1 Processor                                 |

| SuperS      | State R Logic                               |

| XT Su       | bsystem                                     |

| UART        |                                             |

| Memo        | ry Subsystem                                |

| CGA-0       | Compatible Graphics Controller              |

|             | cal Characteristics                         |

| AC Specifi  | cations                                     |

| Mechanica   | Specifications                              |

| Representa  | tives                                       |

|             |                                             |

| List of Tal | bles                                        |

| Table 1.    | F8680 Pin Allocation                        |

| Table 2.    | Signal Names6                               |

| Table 3.    | Programmable Pin Functions 16               |

| Table 4.    | XT-Compatible I/O Port Assignment 19        |

| Table 5.    | System Memory Usage 20                      |

| Table 6.    | Bank Switch Register Ranges                 |

| Table 7.    | Pin Assignments - DRAM Interface Signals 26 |

| Table 8.    | Address Multiplexing                        |

| Table 9.    | Pin Assignments - SRAM Interface Signals 31 |

| Table 10.   | Address Bus Connections for SRAM Devices 32 |

■ Contents F8680 PC/CHIP

| Table 11.    | Pin Assignments - ROM/PROM Interface Signals 35             |

|--------------|-------------------------------------------------------------|

| Table 12.    | PCMCIA Signal Name Equivalents                              |

| Table 13.    | Pin Assignments - PCMCIA Interface Signals 37               |

| Table 14.    | Operating Conditions                                        |

| Table 15.    | Capacitance                                                 |

| Table 16.    | DC Characteristics at 5V 47                                 |

| Table 17.    | DC Characteristics at $3.3V$ 48                             |

| Table 18.    | Timing Symbols Associated with Signal Types $\ \ldots \ 50$ |

| Table 19.    | Timing Parameters                                           |

| Table 20.    | AC Characteristics - System Clock Timings 52                |

| Table 21.    | AC Characteristics - DRAM Signal Timings 54                 |

| Table 22.    | AC Characteristics - SRAM Signal Timings $\dots 56$         |

| Table 23.    | AC Characteristics - PSRAM Signal Timings 57                |

| Table 24.    | AC Characteristics - Suspend Refresh Signal Timings         |

| Table 25.    | AC Characteristics - DMA Signal Timings 59                  |

| Table 26.    | AC Characteristics - XT Bus I/O Cycle<br>Signal Timings 61  |

| Table 27.    | AC Characteristics - XT Bus Memory Signal Timings           |

| Table 28.    | AC Characteristics - PCMCIA Interface Signal Timings        |

| Table 29.    | AC Characteristics - Graphics Controller Signal Timings 67  |

| Table 30.    | AC Characteristics - RESET Signal Timing 70                 |

| List of Figu | ures                                                        |

| Figure 1.    | F8680 Block Diagramiv                                       |

| Figure 2.    | F8680 Pinout, Top View $\dots 1$                            |

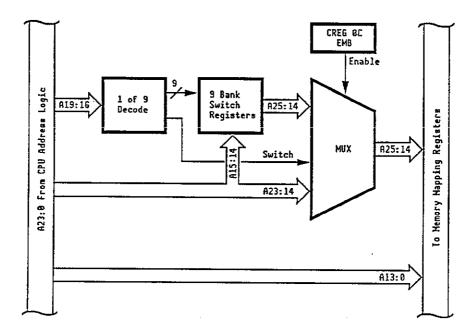

| Figure 3.    | Bank Switching Logic                                        |

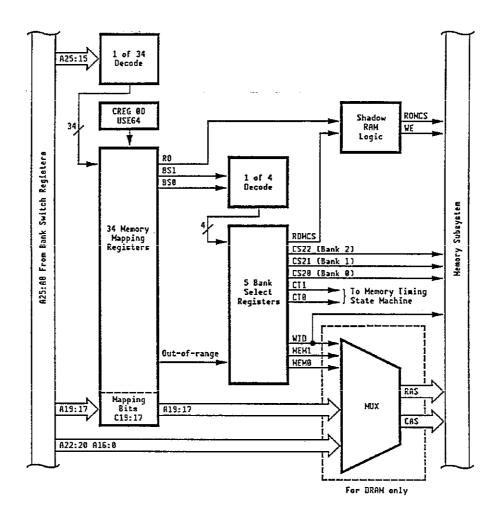

| Figure 4     | Memory Manning Logic 24                                     |

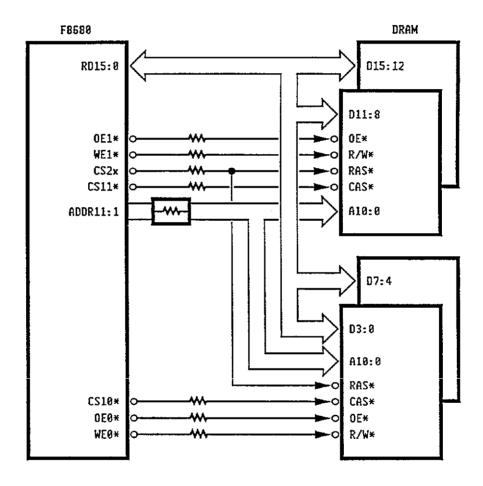

| Figure 5.  | Interface to 4-bit DRAM                                 |

|------------|---------------------------------------------------------|

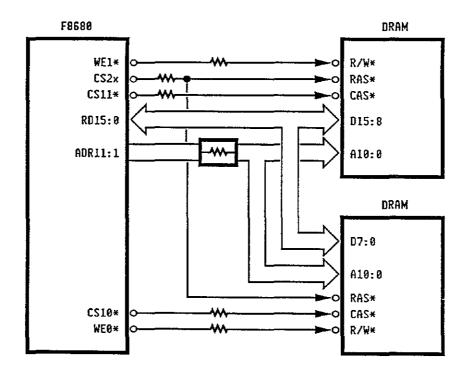

| Figure 6.  | Interface to 8-bit DRAM 29                              |

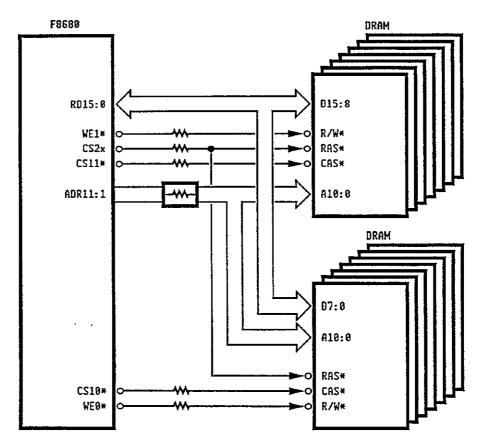

| Figure 7.  | Interface to 1-bit DRAM                                 |

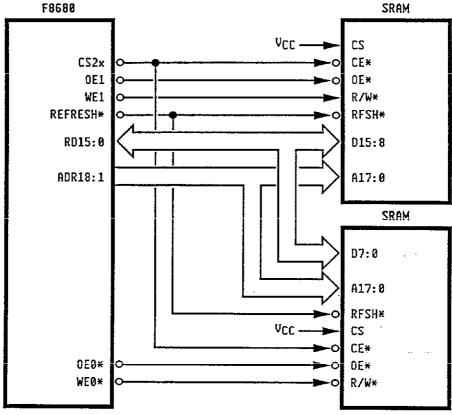

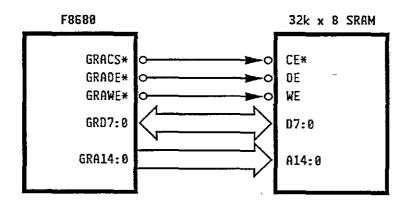

| Figure 8.  | Interface to SRAM                                       |

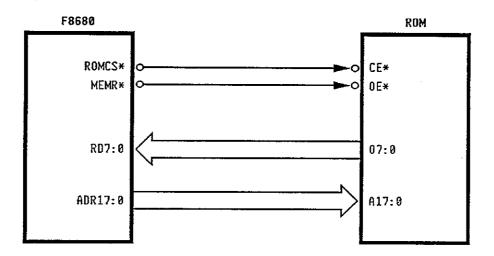

| Figure 9.  | Interface to 8-bit ROM                                  |

| Figure 10. | Connection of Display SRAM                              |

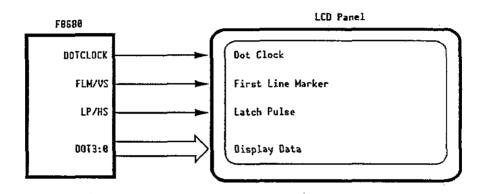

| Figure 11. | Display Controller Signals to the LCD Panel 41          |

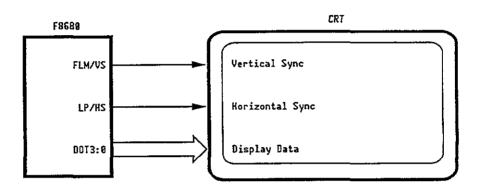

| Figure 12. | Display Controller Signals to the CRT 44                |

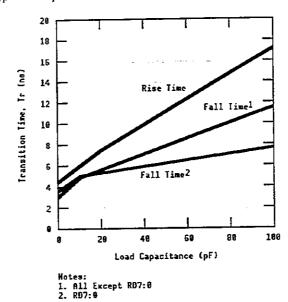

| Figure 13. | Typical Output Transition Time vs Load Capacitance      |

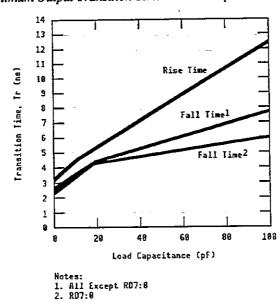

| Figure 14. | Minimum Output Transition Time vs Load Capacitance      |

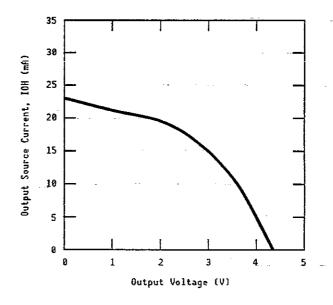

| Figure 15. | Output Source Current vs Output Voltage (@Vcc=4.5V)     |

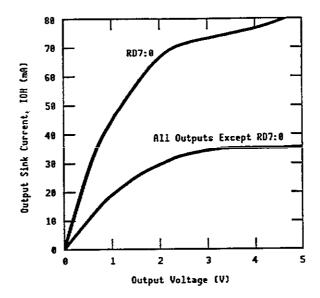

| Figure 16. | Output Sink Current vs Output Voltage (@Vcc=4.5V)       |

| Figure 17. | Output Source Current vs Output Voltage (@Vcc=3V)       |

| Figure 18. | Output Sink Current vs Output Voltage (@Vcc=3V)         |

| Figure 19. | Output Delay Parameters—General Case 51                 |

| Figure 20. | Input Setup and Hold Parameters—General Case 52         |

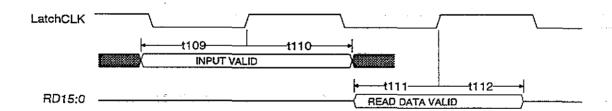

| Figure 21. | Timing for System Clocks                                |

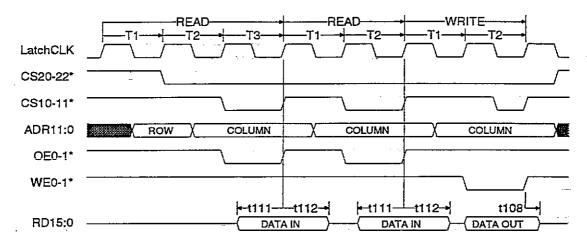

| Figure 22. | Timing for Non-page-mode DRAM Cycles 54                 |

| Figure 23. | Timing for Page-mode DRAM Cycles 55                     |

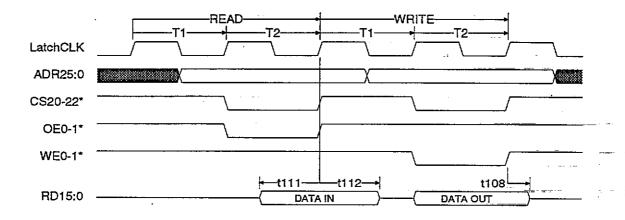

| Figure 24. | Timing for SRAM Access                                  |

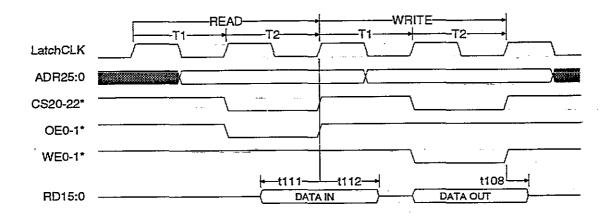

| Figurë 25. | Timing for Pseudo-SRAM Access 57                        |

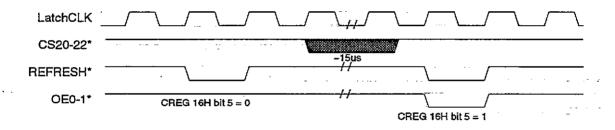

| Figure 26. | Timing for DRAM Suspend Mode Refresh 58                 |

| Figure 27. | Functional Timing for PSRAM Active Mode Refresh $$ . 58 |

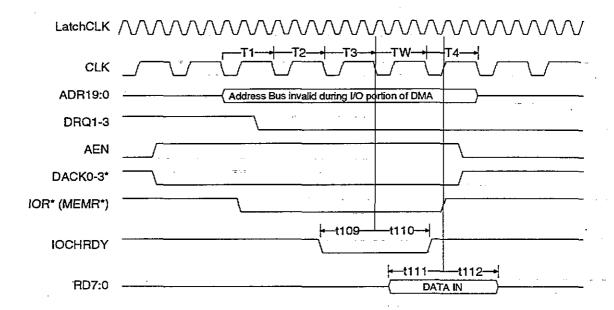

| Figure 28. | Functional Timing for PSRAM Suspend Mode Refresh 58     |

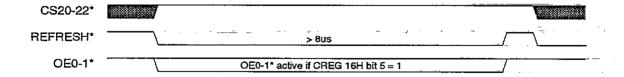

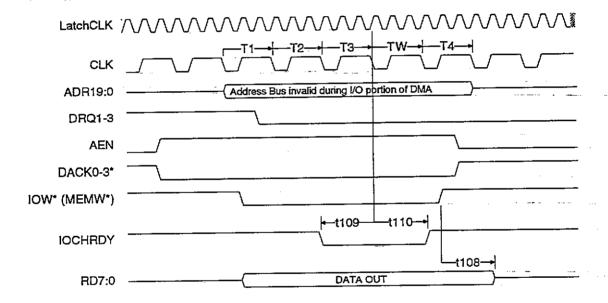

| Figure 29. | Timing for DMA Read Cycles 59                           |

| Figure 30. | Timing for DMA Write Cycles 60                          |

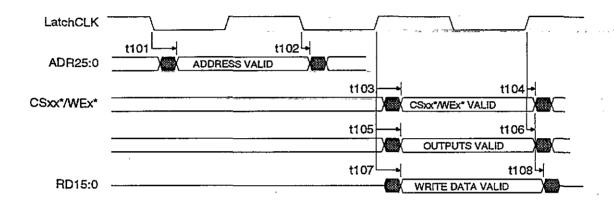

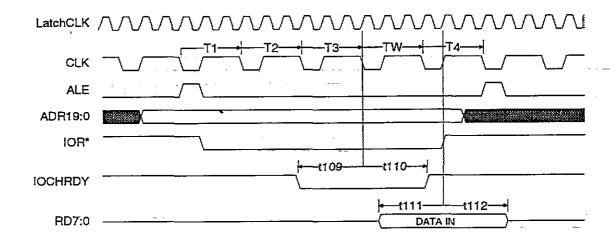

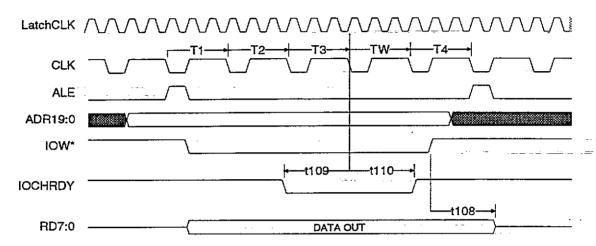

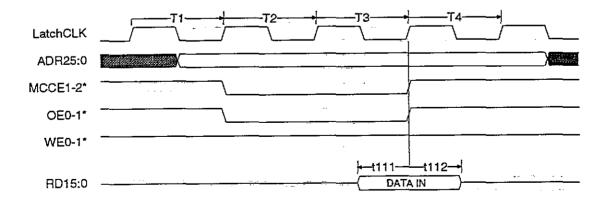

| Figure 31. | Timing for I/O Read                                 | 61 |

|------------|-----------------------------------------------------|----|

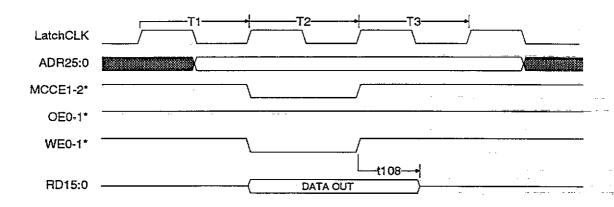

| Figure 32. | Timing for I/O Write                                | 62 |

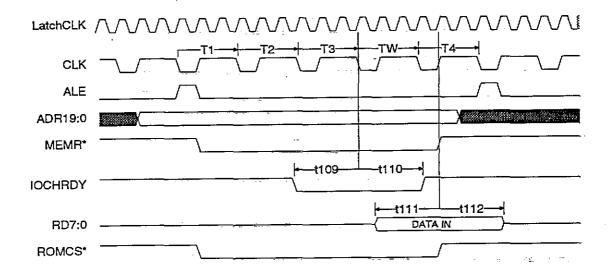

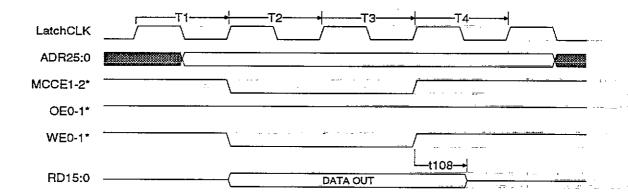

| Figure 33. | Timing for XT Bus Memory Read                       | 63 |

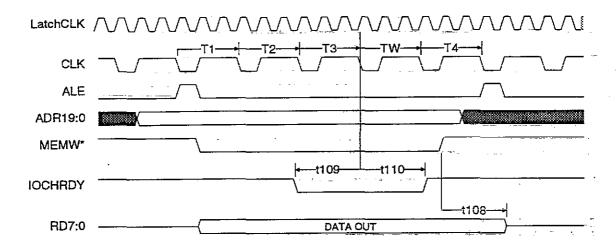

| Figure 34. | Timing for XT Bus Memory Write                      | 64 |

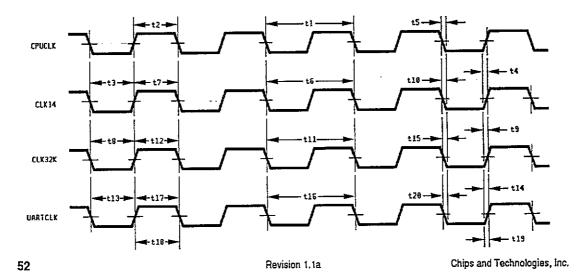

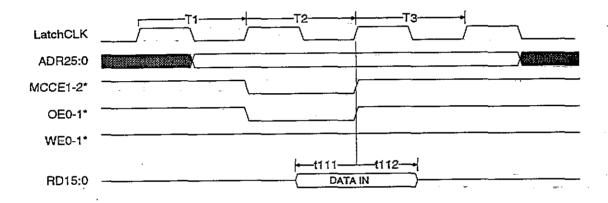

| Figure 35. | Timing for PCMCIA Memory Read (1 Cycle Per State)   | 65 |

| Figure 36. | Timing for PCMCIA Memory Read (2 Cycles Per State)  | 65 |

| Figure 37. | Timing for PCMCIA Memory Write (1 Cycle Per State)  | 66 |

| Figure 38. | Timing for PCMCIA Memory Write (2 Cycles Per State) | 66 |

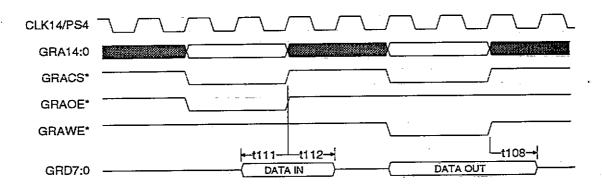

| Figure 39. | Timing for Graphics SRAM                            | 67 |

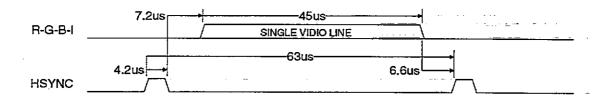

| Figure 40. | Functional Horizontal Sync Timing for CRT           | 68 |

| Figure 41. | Functional Vertical Sync Timing for CRT             | 68 |

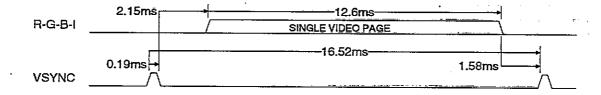

| Figure 42. | Functional Timing for LCD Panel Signals             | 69 |

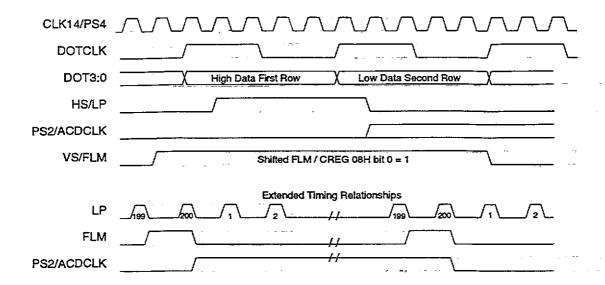

| Figure 43. | Timing for RESET                                    | 70 |

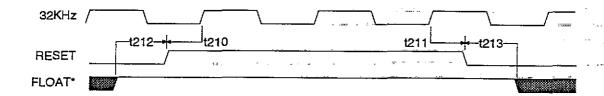

| Figure 44. | Timing for UART                                     | 70 |

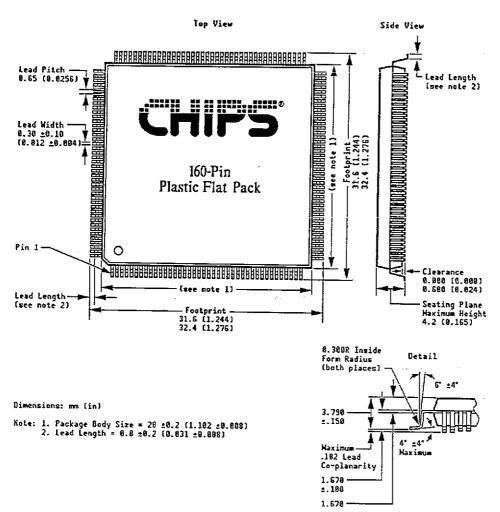

| Figure 45  | 160-Pin Plastic Flat Pack                           | 71 |

#### Introduction

The F8680 PC/CHIP is designed for use in low-power and cost-sensitive DOS applications such as small entry-level computers, electronic hand-helds, and embedded controller systems. The F8680 design integrates a high-speed 8086-compatible microprocessor with an XT subsystem, SuperState R management logic, a memory controller/manager, a graphics controller, and a UART.

## **Pin Description**

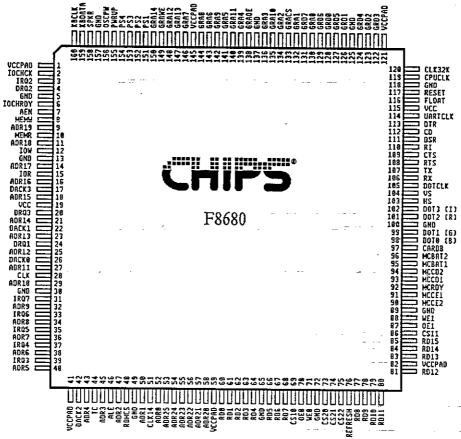

The F8680 single-chip PC is packaged in a 160-pin plastic flat pack package. Figure 2 shows the top view of the chip layout.

Figure 2. F8680 Pinout, Top View 160-Pin Plastic Flat Pack

Table I lists the chip signal assignment by pin number.

Table 1. F8680 Pin Allocation

| Pin No. | Signal  | Type | Description       |

|---------|---------|------|-------------------|

| 1       | VCCPAD  | I    | Power             |

| 2       | IOCHCK* | I    | I/O Channel Check |

| 3       | IRQ2    | I    | Interrupt Request |

| 4       | DRQ2    | I    | DMA Request       |

| 5       | GND     | I    | Ground            |

| 6       | IOCHRDY | I    | I/O Channel Ready |

| 7       | AEN     | 0    | Address Enable    |

| 8       | MEMW*   | 0 -  | Memory Write      |

| 9       | ADR19   | 0    | Address Bus       |

| 10      | MEMR*   | 0    | Memory Read       |

| 11      | ADR18   | 0    | Address Bus       |

| 12      | IOW*    | О    | I/O Write         |

| 13      | GND     | I    | Ground            |

| 14      | ADR17   | 0    | Address Bus       |

| 15      | IOR*    | 0    | I/O Read          |

| 16      | ADR16   | 0    | Address Bus       |

| 17      | DACK3*  | 0    | DMA Acknowledge   |

| 18      | ADR15   | 0    | Address Bus       |

| 19      | VCC     | I    | Core Power        |

| 20      | DRQ3    | I    | DMA Request       |

| 21      | ADR14   | 0    | Address Bus       |

| 22 -    | DACKI*  | О    | DMA Acknowledge   |

| 23      | ADR13   | О    | Address Bus       |

| 24      | DRQ1    | I    | DMA Request       |

| 25      | ADR12   | 0    | Address Bus       |

| 26      | DACKO*  | 0    | DMA Acknowledge   |

| 27      | ADR11   | 0    | Address Bus       |

| 28      | CLK     | 0    | XT bus clock      |

| 29      | ADR10   | 0    | Address Bus       |

| 30      | GND     | I    | Ground            |

| 31      | IRQ7    | I    | Interrupt Request |

| 32      | ADR9    | 0    | Address Bus       |

| 33      | IRQ6    | I    | Interrupt Request |

| 34      | ADR8    | 0    | Address Bus       |

| 35      | IRQ5    | I    | Interrupt Request |

| 36      | ADR7    | 0    | Address Bus       |

| 37      | IRQ4    | I    | Interrupt Request |

| 38      | ADR6    | 0    | Address Bus       |

| 39      | IRQ3    | - 'I | Interrupt Request |

| 40      | ADR5    | 0    | Address Bus       |

Table 1. F8680 Pin Allocation (continued)

| Pin No.    | Signal   | Type  | Description                |

|------------|----------|-------|----------------------------|

| 41         | VCCPAD   | I     | Power                      |

| 42         | DACK2*   | 0     | DMA Acknowledge            |

| 43         | ADR4     | 0     | Address Bus                |

| 44         | TC       | 0     | Terminal Count             |

| 45         | ADR3     | 0     | Address Bus                |

| 46         | ALE      | 0     | Address Latch Enable       |

| 47         | ADR2     | 0     | Address Bus                |

| 48         | ROMCS*   | 0     | ROM Chip Select            |

| 49         | GND      | I     | Ground                     |

| 50         | ADR1     | О     | Address Bus                |

| 51         | CLK14    | I     | 14MHz timer channels clock |

| 52         | ADR0     | Ó     | Address Bus                |

| 53         | ADR25    | . 0   | Address Bus                |

| 54         | ADR24    | 0     | Address Bus                |

| <b>5</b> 5 | ADR23    | 0     | Address Bus                |

| 56         | ADR22    | 0     | Address Bus                |

| 57         | ADR21    | Ō     | Address Bus                |

| 58         | ADR20    | Ō     | Address Bus                |

| 59         | VCCPAD   | Ī     | Power                      |

| 60         | RD0      | Ī/O   | Data Bus                   |

| 61         | RD1      | I/O   | Data Bus                   |

| 62         | RD2      | I/O   | Data Bus                   |

| 63         | RD3      | I/O   | Data Bus                   |

| 64         | RD4      | I/O   | Data Bus                   |

| 65         | GND      | Ĭ     | Ground                     |

| 66         | RD5      | I/O   | Data Bus                   |

| 67         | RD6      | I/O - | Data Bus                   |

| 68         | RD7      | I/O   | Data Bus                   |

| 69         | CS10*    | Ö     | High byte/low byte select  |

| 70         | OE0*     | 0     | Output Enable              |

| 71         | WE0*     | 0     | Write Enable               |

| 72         | GND      | I     | Ground                     |

| 73         | CS20*    | 0     | Bank select                |

| 74         | CS21*    | 0     | Bank select                |

| 75         | CS22*    | 0     | Bank select                |

| 76         | REFRESH* | 0     | Refresh                    |

| 77         | RD8      | ľO    | Data Bus                   |

| 78         | RD9      | ΙΟ    | Data Bus                   |

| 79         | RD10     | ľo    | Data Bus                   |

| 80         | RD11     | ΪΟ    | Data Bus                   |

Table 1. F8680 Pin Allocation (continued)

| Pin No. | Signal   | Туре | Description                 |

|---------|----------|------|-----------------------------|

| 81      | RD12     | 1/0  | Data Bus                    |

| 82      | VCCPAD   | I    | Power                       |

| 83      | RD13     | I/O  | Data Bus                    |

| 84      | RD14     | NO   | Data Bus                    |

| 85      | RD15     | NO   | Data Bus                    |

| 86      | CS11*    | 0    | High byte/low byte select   |

| 87      | OE1*     | 0    | Output Enable               |

| 88      | WE1*     | 0    | Write Enable                |

| 89      | GND      | 1    | Ground                      |

| 90      | MCCE2*   | 0    | Mem. Card Chip Slet. High   |

| 91      | MCCE1*   | 0    | Mem. Card Chip Slct. Low    |

| 92      | MCRDY    | 1    | Memory Card Ready           |

| 93      | MCCD1*   | I    | Memory Card Detect          |

| 94      | MCCD2*   | 1    | Memory Card Detect          |

| 95      | MCBAT1   | 1    | Memory Card Battery         |

| 96      | MCBAT2   | I    | Memory Card Battery         |

| 97      | CARDB    | 0    | Card B pin                  |

| 98      | DOT0/B   | 0    | Display data output         |

| 99      | DOT1/G   | 0    | Display data output         |

| 100     | GND      | 1    | Ground                      |

| 101     | DOT2/R   | 0    | Display data output         |

| 102     | DOT3/I   | 0    | Display data output         |

| 103     | HS/LP    | 0    | Hor. Sync/Latch Pulse       |

| 104     | VS/FLM   | 0    | Ver. Sync/First Line Marker |

| 105     | DOTCLOCK | 0    | Dot Clock                   |

| 106     | Rx       | I    | Receive Data                |

| 107     | Τx       | 0    | Transmit Data               |

| 108     | RTS*     | 0    | Ready To Send               |

| 109     | CTS*     | 1    | Clear To Send               |

| 110     | RI*      | ĭ    | Ring Indicator              |

| 111     | DSR*     | I    | Data Set Ready              |

| 112     | CD*      | I    | Carrier Detect              |

| 113     | DTR*     | 0    | Data Terminal Ready         |

| 114     | UARTCLK  | I    | UART clock                  |

| 115     | VCC      | 1    | Core Power                  |

| 116     | FLOAT*   | I    | Float all pins              |

| 117     | RESET    | I    | Chip Reset                  |

| 118     | GND      | 1    | Ground                      |

| 119     | CPUCLK - | I    | Processor clock             |

| 120     | CLK32K   | I    | 32kHz SuperState R clock    |

Table 1. F8680 Pin Allocation (continued)

| Pin No. | Signal  | Туре     | Description            |

|---------|---------|----------|------------------------|

| 121     | VCCPAD  | I        | Power                  |

| 122     | GRD3    | 0        | Graphics Data          |

| 123     | GRD2    | O        | Graphics Data          |

| 124     | GRD4    | 0        | Graphics Data          |

| 125     | GND     | I        | Ground                 |

| 126     | GRD1    | 0        | Graphics Data          |

| 127     | GRD5    | 0        | Graphics Data          |

| 128     | GRD0    | 0        | Graphics Data          |

| 129     | GRD6    | 0        | Graphics Data          |

| 130     | GRA0    | 0        | Graphics Address       |

| 131     | GRD7    | <b>O</b> | Graphics Data          |

| 132     | GRA1    | 0        | Graphics Address       |

| 133     | GRACS*  | 0        | Graphics Chip Select   |

| 134     | GRA2    | О        | Graphics Address       |

| 135     | GRA10   | 0        | Graphics Address       |

| 136     | GRA3    | 0        | Graphics Address       |

| 137     | GND     | I        | Ground                 |

| 138     | GRAOE*  | 0        | Graphics Output Enable |

| 139     | GRA4    | 0        | Graphics Address       |

| 140     | GRA11   | 0        | Graphics Address       |

| 141     | GRA5    | 0        | Graphics Address       |

| 142     | GRA9    | 0        | Graphics Address       |

| 143     | GRA6    | 0        | Graphics Address       |

| 144     | GRA8    | 0        | Graphics Address       |

| 145     | VCCPAD  | I        | Power                  |

| 146     | GRA7    | 0        | Graphics Address       |

| 147     | GRA13   | 0        | Graphics Address       |

| 148     | GRA12   | 0        | Graphics Address       |

| 149     | GRAWE*  | 0        | Graphics Write Enable  |

| 150     | GRA14   | 0        | Graphics Address       |

| 151     | PS1     | ŊΟ       | Programmable Pin       |

| 152     | PS2     | 1/0      | Programmable Pin       |

| 153     | PS3     | I/O      | Programmable Pin       |

| 154     | PS4     | I/O      | Programmable Pin       |

| 155     | PWRUP   | I        | Power Up               |

| 156     | OSCPW   | O        | Power to Oscillator    |

| 157     | GND     | I        | Ground                 |

| 158     | SPKR    | 0        | Speaker data           |

| 159     | KBDATA* | ľO       | Keyboard Data          |

| 160     | KBCLK*  | I/O      | Keyboard Clock         |

## **Signal Description**

The signal groups of the F8680 single-chip PC are summarized in Table 2. A signal description follows the table.

Table 2. Signal Names

| Address and Data  ADR25:0  RD15:0  J/O  Data Bus  Low or tri-state  Low or tri-state  ALE  ALE  O  Address Enable  Low or tri-state  ALE  DRQ1-3  DACK0-3*  O  DMA Acknowledge  IOCHCK*  I J/O Channel Check  IOCHRDY  IOCHANNEL  IOR*  O  J/O Read  INPUT  IOR*  IOW*  O  J/O Write  IRQ2-7  I Interrupt Request  MEMR*  O  Memory Write  Memory Write  Inactive or tri-state  Incut  Incut | Hup)  repulldn)  te 1E/0  te 1E/0  llup)  te 1E/0  | 1 1            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------|

| XT Bus Control AEN O Address Enable Low or tri-state  ALE O Address Latch Enable Inactive or tri-state  DRQ1-3 I DMA Request Input (use 10k pu  DACK0-3* O DMA Acknowledge Tri-state (use 10k  IOCHCK* I I/O Channel Check Input  IOCHRDY I I/O Channel Ready Input  IOR* O I/O Read Inactive or tri-state  IOW* O I/O Write Inactive or tri-state  IRQ2-7 I Interrupt Request Input (use 10k pu  MEMR* O Memory Read Inactive or tri-state  MEMW* O Memory Write Inactive or tri-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | te 1E/0 illup) te 1E/0 te 1E/0 llup) te 1E/0       | 1              |

| ALE O Address Latch Enable Inactive or tri-state DRQ1-3 I DMA Request Input (use 10k put DACK0-3* O DMA Acknowledge Tri-state (use 10k IOCHCK* I I/O Channel Check Input IOCHRDY I I/O Channel Ready Input IOR* O I/O Read Inactive or tri-state IOW* O I/O Write Inactive or tri-state IRQ2-7 I Interrupt Request Input (use 10k put INEMR* O Memory Read Inactive or tri-state INCM* O I/O Write Inactive or tri-state INCM* O Memory Write INCM* O Write INCM* O Memory Write INCM* O Write INC | te 1E/0 illup) te 1E/0 te 1E/0 llup) te 1E/0       | 1              |

| DRQ1-3 I DMA Request Input (use 10k put DACK0-3* O DMA Acknowledge Tri-state (use 10k put IOCHCK* I I/O Channel Check Input IOCHRDY I I/O Channel Ready Input IOR* O I/O Read Inactive or tri-state IOW* O I/O Write Inactive or tri-state IRQ2-7 I Interrupt Request Input (use 10k put INEMR* O Memory Read Inactive or tri-state INCM* O Memory Read Inactive or tri-state INCM* Inactive or tri-state INCM* Inactive or tri-state INCM* O Memory Write Inactive or tri-state INCM*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Illup)  pulldn)  te 1E/0  te 1E/0  Illup)  te 1E/0 | 1              |

| DACKO-3* O DMA Acknowledge Tri-state (use 10k IOCHCK* I I/O Channel Check Input IOCHRDY I I/O Channel Ready Input IOR* O I/O Read Inactive or tri-state IOW* O I/O Write Inactive or tri-state IRQ2-7 I Interrupt Request Input (use 10k put INEMR* O Memory Read Inactive or tri-state INCM* O Memory Write Inactive or tri-state INCM* Inactive or tri-state INCM* O Memory Write Inactive or tri-state INCM* O Memory Write Inactive or tri-state INCM* O Memory Write Inactive or tri-state INCM*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | te 1E/0 te 1E/0 llup) te 1E/0                      | 1              |

| IOCHCK* I I/O Channel Check Input IOCHRDY I I/O Channel Ready Input IOR* O I/O Read Inactive or tri-stat IOW* O I/O Write Inactive or tri-stat IRQ2-7 I Interrupt Request Input (use 10k put MEMR* O Memory Read Inactive or tri-stat MEMW* O Memory Write Inactive or tri-stat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | te 1E/0<br>te 1E/0<br>Ilup)<br>te 1E/0             | 1              |

| IOCHRDY I I/O Channel Ready Input IOR* O I/O Read Inactive or tri-state IOW* O I/O Write Inactive or tri-state IRQ2-7 I Interrupt Request Input (use 10k put MEMR* O Memory Read Inactive or tri-state MEMW* O Memory Write Inactive or tri-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | te 1E/0<br>Ilup)<br>te 1E/0                        | 1              |

| IOR* O I/O Read Inactive or tri-state IOW* O I/O Write Inactive or tri-state IRQ2-7 I Interrupt Request Input (use 10k put MEMR* O Memory Read Inactive or tri-state MEMW* O Memory Write Inactive or tri-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | te 1E/0<br>Ilup)<br>te 1E/0                        | 1              |

| IOW* O I/O Write Inactive or tri-stat IRQ2-7 I Interrupt Request Input (use 10k pu MEMR* O Memory Read Inactive or tri-stat MEMW* O Memory Write Inactive or tri-stat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | te 1E/0<br>Ilup)<br>te 1E/0                        | 1              |

| IRQ2-7 I Interrupt Request Input (use 10k put MEMR* O Memory Read Inactive or tri-stat MEMW* O Memory Write Inactive or tri-stat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | llup)<br>te. IE/O                                  | _              |

| MEMR* O Memory Read Inactive or tri-star MEMW* O Memory Write Inactive or tri-star                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | te. IE/O                                           |                |

| MEMW* O Memory Write Inactive or tri-sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1E/0                                               | 1              |

| TC O Terminal Count Inactive or tri-sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | لائتنا سد                                          | 1              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | te 04/0                                            | 1              |

| Clocks CLK O XT bus clock Inactive or tri-star                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | te 04/0                                            |                |

| CLK14 I Timer channels clock Input (drive low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • •                                                |                |

| CLK32K I SuperState R time-of-day clock Input (always act                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ive)                                               |                |

| CPUCLK I Processor clock Input (drive Iow)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                |

| UARTCLK I UART clock Input (drive low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |                |

| Memory Interface CS10-11* O High byte/low byte select Inactive or tri-star                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | te 1E/3                                            | 2              |

| CS20-22* O Bank select Inactive or tri-sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | **                                                 | 2              |

| OE0-1* O Outout Enable Inactive or tri-sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ·                                                  | 2              |

| WEO-1* O Write Enable Inactive or tri-sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    | 2              |

| ROMCS* O ROM Chip Select Tri-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    | -              |

| Graphics Controller DOT3:0 O Display data output Low or tri-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0E/0                                               | 3              |