# SN75LBC086 DIFFERENTIAL I/O DRIVER/RECEIVER PAIR WITH SQUELCH, JABBER CONTROL, AND COLLISION DETECTION

SLLS120A - JUNE 1991 - REVISED SEPTEMBER 1991

- Meets or Exceeds the IEEE STD 802.3I, Type 10BASE-T

- Differential (Twisted-Pair) I/O Driver/Receiver

- High-Speed Receiver . . . t<sub>pd</sub> = 50 ns Max

- Receiver Squelch Circuit Integrity Improved With Noise Filter

- Jabber Control Prevents Network Lockup

- Collision Detection for Multiple-User Networks

- Data Link Integrity Monitored With Link Test Pulse

- Externally Addressable Test Register Controls Signal Quality Error Testing

- CMOS and Raised ECL Compatible

- 24-Terminal, 300-mil Dual-In-Line Package

#### DW PACKAGE (TOP VIEW) 24 🛮 X1 CLKOUT [ TXDATAA [ 23 X2 22 SQEEN TXDATAB [ 3 TXEN **1** 4 21 TX+ GND (L) [] 5 20**∏** TX− 19 GND (P) V<sub>CC(L)</sub> [ 6 18 V<sub>CC(P)</sub> GND (L) [] 7 17 FULLD RXDATAA [] 8 16 RX+ RXDATAB [ RXEN [ 15∏ RX-14 CTL LOOP 1 11 13 JABB 12 LINK [

#### description

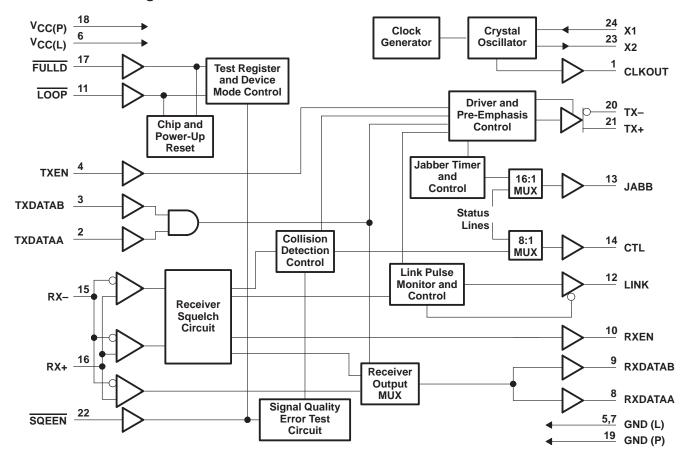

The SN75LBC086 is a single-channel differential driver/receiver interface device for the medium attachment unit (MAU) used in 10-MHz twisted-pair Ethernet applications. The device uses a 5-V supply and is designed to interface with two pairs of telephone-grade twisted-pair cables coupled through isolation transformers. The functional components of the device include a differential receiver and driver, receiver squelch with noise filter, jabber controls, collision detection, data link monitor, and signal quality error (SQE) testing. The LinBiCMOS™ process technology is used in the device design to ensure analog precision, low power, and high-speed operation.

The device contains an elaborate receiver-squelch circuit<sup>†</sup> that provides an improved level of noise rejection by qualifying the incoming signal stream with three different criteria. First, the signal is compared to a set threshold voltage level. Then, the pulse duration is compared to a set time window. Last, the signal must follow a set pattern of positive and negative pulses before the circuit finally opens the receiver channel to the incoming data packet.

The jabber control is designed to prevent a defective controller from locking up the network by limiting the data packet transmission time to 20 to 30 ms. When a packet length exceeds 20 to 30 ms, the driver is turned off for about 600 ms. The driver-enable input must be made inactive by the controller during this period before the jabber control will release the driver. The JABB output is active (high) when a jabber condition exists.

Collision detection is used to arbitrate access to the multiuser network. This detection is done logically by monitoring the receive line for a valid signal during a driver transmission. When a collision is detected, this device informs the controller with an active-high CTL output. After a valid packet transmission, the device also performs a signal quality error test causing the CTL output to go active (high). This test is disabled when the SQEEN input goes inactive (high).

The device tests data-link integrity during the idle state by periodically driving the driver line with a unipolar pulse called a link-test pulse. The receiver looks for this link-test pulse on the receive line. A failed line link is indicated by a high-impedance state at the LINK output. This output drives an LED for monitoring if needed.

An internal test register is externally controlled with inputs  $\overline{\text{FULLD}}$  and  $\overline{\text{LOOP}}$  to select the device testing mode. When in the test mode, serial test-mode control patterns are clocked into the test register through input  $\overline{\text{SQEEN}}$ . These control patterns select various modes to test the internal circuits.

† Embodies technology covered by one or more Digital Equipment Corporation Patents. LinBiCMOS is a trademark of Texas Instruments Incorporated.

#### SLLS120A – JUNE 1991 – REVISED SEPTEMBER 1991

# functional block diagram

#### **Terminal Functions**

| TE                 | RMINAL      |          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|-------------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | LEVEL       | NO.      | 1/0    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLKOUT             | CMOS        | 1        | 0      | Clock output. This 10-MHz buffered clock drives other interface devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CTL                | CMOS        | 14       | 0      | Control. In normal mode, CTL high indicates a collision. In test mode, status lines are muxed out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FULLD              | TTL         | 17       | I      | Full-duplex mode. When active (low), the device is placed in the full-duplex operating mode for simple point-to-point communication applications. In the full-duplex mode, the receiver and driver are both active with collision detection disabled. After LOOP and FULLD go active (low), in that order, a device reset is initiated and while both are active (low), test select data clocks into the test register using a 100-ns clock at the X1 input. This terminal is held inactive (high) due to an internal pullup resistor.                                                       |

| GND (L)            | GROUND      | 5<br>7   |        | Logic grounds. These terminals provide a ground return for the CMOS core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND (P)            | GROUND      | 19       |        | Power ground. This provides a ground return for the input and output buffers, driver (transmitter), and receiver circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| JABB               | CMOS        | 13       | 0      | Jabber control. When a jabber condition exists during normal mode operation, this signal goes active (high) to report jabber-control status to the controller. In the test mode, this provides a multiplexed signal for internal timer and counter functions.                                                                                                                                                                                                                                                                                                                                |

| LINK               | CMOS        | 12       | 0      | Link status. This 3-state output indicates the status of the receiver and interface link. When driving an LED (with anode to resistor to V <sub>CC</sub> ), a high-impedance level indicates a failed link and the LED is off. A momentary high level indicates the device is receiving valid data and the LED is blinking on and off. A continuous low level indicates the device is receiving valid link pulses but no data, and the LED is on.                                                                                                                                            |

| LOOP               | TTL         | 11       | ı      | Loop-back mode. When the device is in the normal operating mode (not test mode) and $\overline{\text{LOOP}}$ is active (low), the driver (transmit) data is directed to the receive data path to put the device in the loop-back mode and the driver is turned off. After $\overline{\text{LOOP}}$ and $\overline{\text{FULLD}}$ go active (low), in that order, a device reset is initiated and while both are active (low), test select data clocks into the test register using a 100-ns clock at the X1 input. This terminal is held inactive (high) due to an internal pullup resistor. |

| RX+                |             | 16       |        | Differential receiver inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RX-                |             | 15       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RXEN               | CMOS        | 10       | 0      | Receiver squelch status. This provides squelch status information to the controller. When active (high), this signal indicates that the data path is valid or open from the receive channel through the device. An inactive (low) indicates that the receive channel is squelched or closed. This signal is capable of driving an LED monitor.                                                                                                                                                                                                                                               |

| RXDATAA<br>RXDATAB | CMOS<br>ECL | 8<br>9   | 0      | Received-data serial outputs. These outputs provide a choice of logic levels and serial data either from the differential receiver input (RX+ and RX-) or data from the controller (TXDATAA or TXDATAB) when in the loop-back mode. When the receiver is idle, these output levels are normally high. These terminals are held inactive (high) due to an internal pullup resistor.                                                                                                                                                                                                           |

| SQEEN              | TTL         | 22       | I      | Signal-quality error-test enable. In normal operating mode, this enables the SQE test function performed at the end of a data packet transmission. In the test mode, SQEEN is used (with X1 clock) as a serial data input port to load test patterns or selections into the test register. This terminal is held inactive (high) due to an internal pullup resistor.                                                                                                                                                                                                                         |

| TX+                |             | 21       | 0      | Differential driver outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TX-                |             | 20       | 0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TXEN               | TTL         | 4        | I      | Transmitter (driver) enable. When TXEN is active (high), serial data at the TXDATA inputs starts and stops the driver. When TXEN is inactive (low), the driver begins transmitting an idle signal independent of the TXDATA inputs.                                                                                                                                                                                                                                                                                                                                                          |

| TXDATAA<br>TXDATAB | CMOS<br>ECL | 2<br>3   | I      | Transmit-data inputs. A choice of logic-level inputs provide Manchester-encoded serial data to the driver. Internal pullup resistors are included.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CC(L)</sub> | SUPPLY      | 6        |        | V <sub>CC</sub> logic power supply. This provides power to the CMOS core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>CC(P)</sub> | SUPPLY      | 18       |        | V <sub>CC</sub> power supply. This provides power to the input and output buffers, drivers, and receivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| X1<br>X2           | CMOS        | 24<br>23 | 1<br>0 | Crystal input/output. X1 provides an input from an external 10-MHz crystal or another external clock source when the crystal is disconnected. X2 provides an oscillator output.                                                                                                                                                                                                                                                                                                                                                                                                              |

# SN75LBC086 DIFFERENTIAL I/O DRIVER/RECEIVER PAIR WITH SQUELCH, JABBER CONTROL, AND COLLISION DETECTION

SLLS120A - JUNE 1991 - REVISED SEPTEMBER 1991

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)           | 0.5 V to 7 V                 |

|--------------------------------------------------------------|------------------------------|

| Input voltage range at any input, V <sub>I</sub>             | 0.5 V to 5.5 V               |

| Output voltage range at any output, VO                       | 0.5 V to 7 V                 |

| Continuous total power dissipation                           | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub>         | 0°C to 70°C                  |

| Storage temperature range, T <sub>stq</sub>                  | –65°C to 150°C               |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|

| DW      | 1350 mW                                                                    | 10.8 mW/°C                                     | 864 mW                                |

### recommended operating conditions

|                                             |                             |                       | MIN                         | NOM                                                        | MAX                         | UNIT          |  |

|---------------------------------------------|-----------------------------|-----------------------|-----------------------------|------------------------------------------------------------|-----------------------------|---------------|--|

| Supply voltage, V <sub>CC</sub>             |                             |                       | 4.75                        | 5                                                          | 5.25                        | V             |  |

|                                             | TXDATAA, X1                 |                       | 3.15                        |                                                            |                             |               |  |

|                                             | = 1/2 1= 1 2                | T <sub>A</sub> = 0°C  | 0.984V <sub>CC</sub> -0.922 | 0.984V <sub>CC</sub> -0.763                                |                             |               |  |

| High-level output voltage, VIH              | TXDATAB<br>(see Figure 1)   | T <sub>A</sub> = 25°C | 0.984V <sub>CC</sub> -0.877 |                                                            | 0.984V <sub>CC</sub> -0.727 | V             |  |

| nigri-level output voltage, VIH             | (See Figure 1)              | T <sub>A</sub> = 70°C | 0.984V <sub>CC</sub> -0.825 |                                                            | 0.984V <sub>CC</sub> -0.645 | V             |  |

|                                             | TXEN, LOOP,<br>FULLD, SQEEN |                       | 2                           |                                                            |                             |               |  |

|                                             | TXDATAA, X1                 |                       |                             | 0.8<br>.75V <sub>CC</sub> -0.59 0.75V <sub>CC</sub> -0.375 |                             |               |  |

|                                             | = 1/2 1= 1 2                | T <sub>A</sub> = 0°C  | 0.75V <sub>CC</sub> -0.59   |                                                            |                             |               |  |

| Low-level output voltage, VIH               | TXDATAB<br>(see Figure 1)   | T <sub>A</sub> = 25°C | 0.75V <sub>CC</sub> -0.55   |                                                            | 0.75V <sub>CC</sub> -0.35   | $\Box$ $\lor$ |  |

| Low-level output voltage, VIH               | (occ rigare r)              | T <sub>A</sub> = 70°C | 0.75V <sub>CC</sub> -0.531  |                                                            | 0.75V <sub>CC</sub> -0.324  | V             |  |

|                                             | TXEN, LOOP,<br>FULLD, SQEEN |                       |                             |                                                            | 0.8                         |               |  |

| Differential input voltage, V <sub>ID</sub> |                             |                       | 0.586                       |                                                            | 2.8                         | V             |  |

| Common-mode input voltage, V <sub>IC</sub>  |                             |                       | 1.8                         |                                                            | 3.2                         | V             |  |

| Operating free-air temperature, TA          |                             |                       | 0                           |                                                            | 70                          | °C            |  |

NOTE 1: All voltages are with respect to device ground pins GND(L) and GND(P) shorted together.

# **SN75LBC086 DIFFERENTIAL I/O DRIVER/RECEIVER PAIR** WITH SQUELCH, JABBER CONTROL, AND COLLISION DETECTION SLLS120A – JUNE 1991 – REVISED SEPTEMBER 1991

electrical characteristics over recommended operating free-air temperature and supply voltage range (unless otherwise noted)

#### drivers

|     | PARAME                                             | TER                                 | TEST CON                 | DITIONS               | MIN                          | TYP | MAX                          | UNIT |  |

|-----|----------------------------------------------------|-------------------------------------|--------------------------|-----------------------|------------------------------|-----|------------------------------|------|--|

|     |                                                    | CLKOUT, RXDATAA,<br>RXEN, JABB, CTL | I <sub>OH</sub> = -12 mA |                       | 3.7                          |     |                              | V    |  |

| VOH | High-level output voltage                          |                                     |                          | $T_A = 0$ °C          | 0.984 V <sub>CC</sub> -0.922 |     | 0.984 V <sub>CC</sub> -0.763 | V    |  |

|     | voltage                                            | RXDATAB                             | See Figure 1             | T <sub>A</sub> = 25°C | 0.984 V <sub>CC</sub> -0.877 |     | 0.984 V <sub>CC</sub> -0.727 |      |  |

|     |                                                    |                                     |                          | T <sub>A</sub> = 70°C | 0.984 V <sub>CC</sub> -0.825 |     | 0.984 V <sub>CC</sub> -0.645 |      |  |

|     |                                                    | CLKOUT, RXDATAA,<br>RXEN, JABB, CTL | I <sub>OL</sub> = 16 mA  |                       |                              |     | 0.5                          | V    |  |

| ļ., | Low-level output voltage                           | · •                                 |                          | $T_A = 0$ °C          | 0.75 V <sub>CC</sub> -0.59   |     | 0.75 V <sub>CC</sub> -0.375  |      |  |

| VOL |                                                    |                                     | See Figure 1             | T <sub>A</sub> = 25°C | 0.75 V <sub>CC</sub> -0.55   |     | 0.75 V <sub>CC</sub> -0.35   | V    |  |

|     |                                                    |                                     |                          | T <sub>A</sub> = 70°C | 0.75 V <sub>CC</sub> -0.531  |     | 0.75 V <sub>CC</sub> -0.324  |      |  |

|     |                                                    | LINK                                | I <sub>OL</sub> = 12 mA  |                       |                              |     | 0.5                          | V    |  |

| VOD | OD Differential-output voltage (peak)              |                                     | See Figure 2             |                       | 2.2                          |     | 2.8                          | V    |  |

| VOD | V <sub>OD</sub> Differential-output voltage (step) |                                     | See Figure 2             |                       | 1.53                         |     | 1.982                        | V    |  |

|     | Common-mode driver impedance                       |                                     |                          |                       | 2                            | 5   | 8                            | Ω    |  |

#### receivers

|     | PARAMETER  TXDATAA, TXEN, LOOP, FULLD, SQEEN  X1  TXDATAB |                                   | TEST CONDITIONS†        | MIN MAX | UNIT |

|-----|-----------------------------------------------------------|-----------------------------------|-------------------------|---------|------|

| lіН |                                                           | TXDATAA, TXEN, LOOP, FULLD, SQEEN | V <sub>I</sub> = 5.25 V | 20      |      |

|     | High-level input current                                  | X1                                | V  = 5.25 V             | 100     | μΑ   |

|     |                                                           | TXDATAB                           | V <sub>IH</sub> = MAX   | 400     |      |

| IIL | Low-level input current                                   | TXDATAA, TXEN, LOOP, FULLD, SQEEN | V <sub>I</sub> = 0      | -20     |      |

|     |                                                           | X1                                | V   = 0                 | -100    | μΑ   |

|     |                                                           | TXDATAB                           | $V_{IL} = MIN$          | -400    |      |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

#### drivers and receivers

|     |                | ETER           | TEST CONDITIONS                                           | MIN | MAX | UNIT |

|-----|----------------|----------------|-----------------------------------------------------------|-----|-----|------|

| ICC | Supply current | VCC(L), VCC(P) | $V_{CC(L)} = 5.25 \text{ V},  V_{CC(P)} = 5.25 \text{ V}$ |     | 180 | mA   |

# SN75LBC086 DIFFERENTIAL I/O DRIVER/RECEIVER PAIR WITH SQUELCH, JABBER CONTROL, AND COLLISION DETECTION SLLS120A – JUNE 1991 – REVISED SEPTEMBER 1991

# switching characteristics

|                    | PARAMETER                                                       | FROM<br>(INPUT)       | TO<br>(OUTPUT)              | TEST<br>CONDITIONS | MIN | TYP | MAX            | UNIT |

|--------------------|-----------------------------------------------------------------|-----------------------|-----------------------------|--------------------|-----|-----|----------------|------|

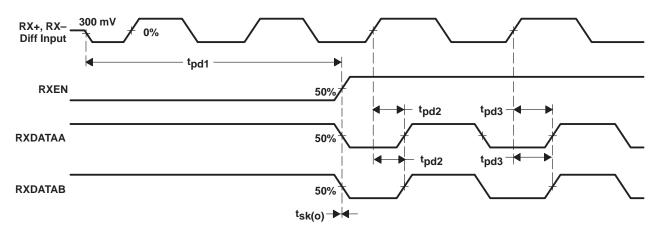

| tpd1               | Propagation delay time                                          | RX+, RX–              | RXEN                        | See Figure 4       |     |     | 5 bit<br>times |      |

| t <sub>pd2</sub>   | Propagation delay time at startup                               | RX+, RX–              | RXDATAA or<br>RXDATAB high  | See Figure 4       |     |     | 75             | ns   |

| t <sub>sk(o)</sub> | Output skew time                                                | RXEN high             | RXDATAA or<br>RXDATAB low   | See Figure 4       |     |     | ±10            | ns   |

| t <sub>pd3</sub>   | Propagation delay time after startup                            | RX+, RX–              | RXDATAA or<br>RXDATAB high  | See Figure 4       |     |     | 50             | ns   |

| t <sub>sk(p)</sub> | Pulse skew time ( tpd3(LH) - tpd3(HL) )                         | RX+, RX–              | RXDATAA or<br>RXDATAAB      | See Figure 4       |     | 2   |                | ns   |

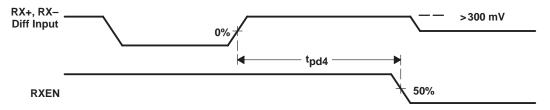

| t <sub>pd4</sub>   | Propagation delay time                                          | RX+, RX-              | RXEN low                    | See Figure 5       | 155 |     | 250            | ns   |

| t <sub>pd5</sub>   | Propagation delay time                                          | TXDATA or<br>TXDATAB  | TX+, TX-                    | See Figure 6       |     |     | 75             | ns   |

| t <sub>sk(p)</sub> | Pulse skew time (t <sub>pd5</sub> (LH) - t <sub>pd5</sub> (HL)) | TXDATAA or<br>TXDATAB | TX+, TX-                    | See Figure 6       |     | 2   |                | ns   |

| t <sub>pd6</sub>   | Propagation delay time in loop mode                             | TXDATAA or<br>TXDATAB | RXDATAA,<br>RXDATAB         | See Figure 7       |     |     | 50             | ns   |

| t <sub>pd7</sub>   | Propagation delay time in loop mode                             | TXEN high             | RXEN high                   | See Figure 7       |     |     | 50             | ns   |

| t <sub>pd8</sub>   | Propagation delay time in loop mode                             | LOOP low              | RXEN low                    | See Figure 7       |     |     | 30             | ns   |

| tpd10              | Propagation delay time                                          | TXEN low              | RXEN low                    | See Figure 8       |     |     | 350            | ns   |

| tpd11              | Propagation delay time                                          | TXEN low              | TX+, TX- high               | See Figure 8       |     |     | 50             | ns   |

| t <sub>p1</sub>    | Precompensation pulse duration                                  |                       | TX+, TX-                    | See Figure 6       | 45  |     | 55             | ns   |

| t <sub>p2</sub>    | Receiver link-beat minimum pulse duration                       |                       |                             | See Figure 9       | 80  |     | 120            | ns   |

| <sup>t</sup> en1   | Enable time                                                     | TXDATAA or<br>TXDATAB | TX+, TX-                    | See Figure 6       |     |     | 75             | ns   |

| t <sub>en2</sub>   | Enable time                                                     | TXEN                  | TX+, TX-                    | See Figure 6       |     |     | 75             | ns   |

| <sup>t</sup> dis1  | Disable time, caused by TXDATAA or TXDATAB high or TXEN low     | TX+, TX- high         | TX+, TX- at<br>585-mV level | See Figure 8       | 250 |     |                | ns   |

| t <sub>pd12</sub>  | Propagation delay time to looped RXEN                           | TXEN high             | RXEN high                   | See Figure 6       |     |     | 100            | ns   |

| <sup>t</sup> pd13  | Propagation delay time for looped back data                     | TXDATAA or<br>TXDATAB | RXDATAA<br>RXDATAB          | See Figure 6       |     |     | 75             | ns   |

# timing requirements

|                                                                 | TEST CONDITIONS | MIN | MAX | UNIT |

|-----------------------------------------------------------------|-----------------|-----|-----|------|

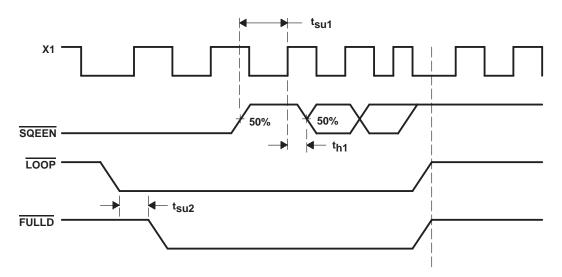

| Setup time, test mode, SQEEN before X1↑, t <sub>su1</sub>       | See Figure 10   | 30  |     | ns   |

| Setup time, test mode, LOOP low before FULLD↓, t <sub>Su2</sub> | See Figure 10   | 25  |     | ns   |

| Hold time, test mode, SQEEN after X1↑, th1                      | See Figure 10   | 25  |     | ns   |

SLLS120A – JUNE 1991 – REVISED SEPTEMBER 1991

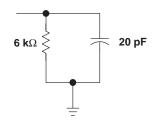

Figure 1. ECL Load Circuit

Figure 2. Differential Load Circuit

Figure 3. CMOS Load Circuit

Figure 4. Receiver Startup Waveforms

Figure 5. Receiver Shutdown Waveforms

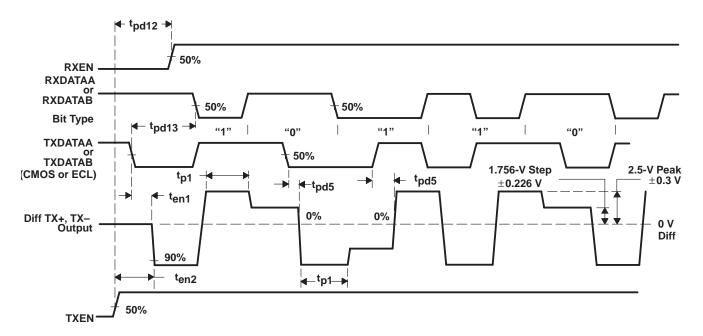

Figure 6. Driver Startup Waveforms

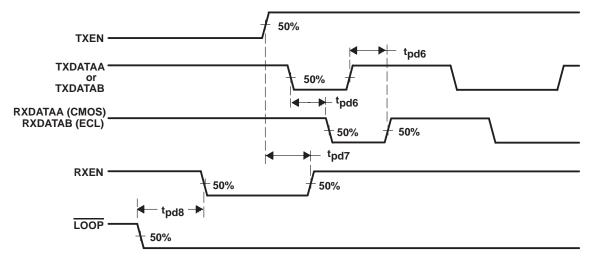

Figure 7. Propagation Delay Waveforms in Loop Mode

SLLS120A – JUNE 1991 – REVISED SEPTEMBER 1991

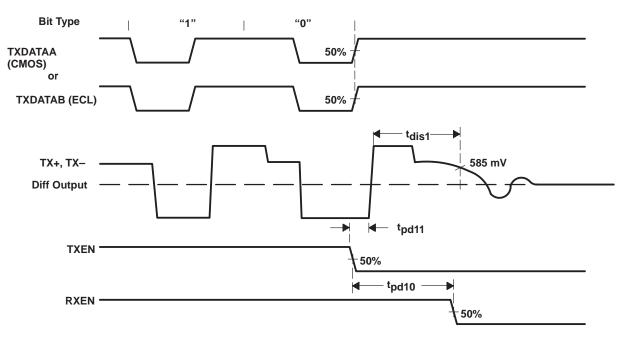

Figure 8. Driver Shutdown Waveforms

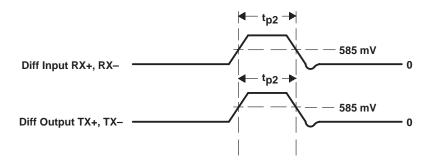

Figure 9. Link Beat Pulse Duration Waveform

Figure 10. Setup and Hold Time Waveforms

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated